## Gigabit Ethernet/PCI Network Interface Card

# Host/NIC Software Interface Definition

**Revision 12.4.13**

P/N 020001

Alteon WebSystems, Inc. 50 Great Oaks Blvd. San Jose, CA 95119

1-408-360-5500

© 1996, 1997, 1998 by Alteon Networks, Inc. All rights reserved.

This document contains proprietary and confidential information of Alteon Networks, Inc. The contents of this document may not be disclosed to third parties, copied, or duplicated in any form, in whole or in part, without the prior written permission of Alteon Networks, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision  $\mathbb{O}(1)$ (ii) of the Rights in Technical Data and Computer Software clause in DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Alteon Networks, Inc. 50 Great Oaks Blvd., San Jose, CA 95119.

#### **Revision History**

Rev 01 6/3/96 Initial Alteon Networks version.

Rev 02 6/5/96 Added statistics, completely described commands and events, fixed many figures.

Rev 03 6/10/96 Major re-write, added flow diagrams, added CONFIDENTIAL markings, lots of changed based on feedback from Wayne and Ted, removed EEPROM layout.

Rev 04 6/19/96 Minor re-organization, removed FRAME\_SENT and FRAME\_RECEIVED events.

Rev 05 7/5/96 Updated data structures, statistics, removed START\_FIRMWARE command, revised bibliography

Rev 06 9/26/96 Converted to framemaker, updated statistics and shared data structures, editorial changes.

Rev 07 11/8/96 Added SET\_HOST\_STATE command, rewrote initialization section, cleanup figures, update and expand command and event descriptions, Remove GET\_STATS command, update for address changes related to RR->TIGON ASIC change, general editorial changes.

Rev 08 1/9/97 Defined all undefined values.

Rev 09 6/1/97 Changed format to comply with Alteon documentation standards, removed GET\_RCB\_FLAGS and SET\_RCB\_FLAGS commands, updated flow diagrams to current design, added section on performance tuning, general editorial changes.

Rev 10 9/1/97 Update document to Revision 1.1 specifications

Rev 10.1 9/17/97 Fix documentation bugs, particularly field definition errors in several of the data structure. Add new section on Serial EEPROM and new fields in the buffer descriptor.

Rev 10.2 10/21/97 Add documentation for new features, correct English and descriptions

Rev 11.0 11/19/97 Update document to Revision 2.1 specifications

Rev 11.1 12/15/97 Add documentation for checksum offload support

Rev 11.2 1/9/98 Documentation corrections and clarifications

Rev 11.3 2/123/98 Documentation corrections and clarifications. Tigon 2 checksum offload support.

Rev 12.0 4/15/98 Reorganized the shared memory areas. New VLAN assist functionality. Update to clock tick handling. Internal loopback available. Special monitoring capability.

Rev 12.0.1 - 12.0.5 5/19/98 - 6/23/98 Minor clarifications

Rev 12.0.6 6/26/98 Add DMA Errata for Tigon 2

Rev 12.1 - 7/29/98 Add BD Coal Now bit, RCB Coal update only bit.

Rev 12.1.1 - 8/4/98 Add SBUS bit to mode\_status word

Rev 12.2 - 8/19/98 Add Host based Send Ring

Rev 12.2.1 - 8/24/98 Add mailbox receive ring replenish, extended multicast commands, new rupt control bits, eliminate receive return consumer index.

Rev 12.3 - 9/23/98 Add mini receive ring, extended receive buffer descriptors, transmit buffer ratio, and 802.3 checksum offload support documentation

Rev 12.3.3 - 1/15/99 Allow sizing of Receive Return Ring

Rev 12.3.9 - Better numbering scheme and fixed description of tcp\_udp\_cksum field in receive buffer descriptor

Rev 12.3.11 - Indicate Min DMA field must be zero due to hardware bug.

Rev 12.4.0 - Add API for 1000BaseT card. Change company name. Long overdue spell check.

I

| 1 | Introduction                                                   |      |

|---|----------------------------------------------------------------|------|

|   | 1.1 TIGON                                                      | . 13 |

|   | 1.2 Feature Set                                                | . 13 |

|   | 1.3 Foundation Data Structures                                 | . 14 |

|   | 1.3.1 Host Addresses                                           | . 14 |

|   | 1.3.2 NIC Addresses                                            | . 14 |

|   | 1.3.3 MAC Addresses                                            | . 14 |

|   | 1.3.4 Endianness                                               | . 14 |

|   | 1.4 LED Meanings                                               | . 15 |

| _ |                                                                |      |

| 2 | Architecture                                                   | 1.7  |

|   | 2.1 Memory Model                                               |      |

|   | 2.1.1 Shared Configuration Block                               |      |

|   | 2.1.1.1 PCI Configuration Region                               |      |

|   | 2.1.1.1.1 PCI Configuration Region Setup for SBus Cards        |      |

|   | 2.1.1.2 Tigon Configuration/Control Region                     |      |

|   | 2.1.1.2.1 Tigon Miscellaneous Host Control Register            |      |

|   | 2.1.1.2.3 Tigon Miscellaneous Configuration Register           |      |

|   | 2.1.1.2.4 Tigon PCI State Register                             |      |

|   | 2.1.1.2.4 Figori FCI State Register                            |      |

|   | 2.1.1.2.6 Tigon Window Data Register                           |      |

|   | 2.1.1.2.7 Tigon DMA Assist State Register                      |      |

|   | 2.1.1.2.8 Tigon CPU State Register                             |      |

|   | 2.1.1.2.9 Tigon CPU Program Counter Register                   |      |

|   | 2.1.1.2.10 Tigon Internal SRAM Address Register                |      |

|   | 2.1.1.2.11 Tigon Internal SRAM Data Register                   |      |

|   | 2.1.1.2.12 Tigon General Purpose Registers                     |      |

|   | 2.1.1.2.13 Tigon MAC RX State Register                         |      |

|   | 2.1.1.3 Mailboxes                                              |      |

|   | 2.1.1.3.1 Host In Interrupt Handler                            |      |

|   | 2.1.1.4 General Communications Region                          |      |

|   | 2.1.1.4.1 MAC Address                                          |      |

|   | 2.1.1.4.2 General Information Pointer                          |      |

|   | 2.1.1.4.3 Multicast MAC Address Transfer Buffer (OBSOLETE)     | . 26 |

|   | 2.1.1.4.4 Operating Mode                                       | . 27 |

|   | 2.1.1.4.5 DMA Read Configuration                               |      |

|   | 2.1.1.4.6 DMA Write Configuration                              | . 28 |

|   | 2.1.1.4.7 Transmit Buffer Ratio                                | . 28 |

|   | 2.1.1.4.8 Event Consumer Index                                 | . 28 |

|   | 2.1.1.4.9 Command Consumer Index                               | . 29 |

|   | 2.1.1.4.10 Tuning Parameters                                   |      |

|   | 2.1.1.4.11 NIC Trace Pointer                                   |      |

|   | 2.1.1.4.12 NIC Trace Start                                     | . 32 |

|   | 2.1.1.4.13 NIC Trace Length                                    |      |

|   | 2.1.1.4.14 ifIndex                                             |      |

|   | 2.1.1.4.15 ifMtu                                               |      |

|   | 2.1.1.4.16 Mask Interrupts                                     |      |

|   | 2.1.1.4.17 Gigabit Link State                                  |      |

|   | 2.1.1.4.18 10/100 Link State                                   |      |

|   | 2.1.1.4.19 Receive Return Consumer Index (OBSOLETE on Tigon 2) |      |

|   | 2.1.1.4.20 Command Ring                                        | 33   |

| 2.1.1.5 Local Memory Window                                      | 33 |

|------------------------------------------------------------------|----|

| 2.1.2 General Information Block                                  |    |

| 2.1.2.1 Statistics                                               |    |

| 2.1.2.1.1 MAC Statistics                                         | 34 |

| 2.1.2.1.2 Interface Statistics                                   | 35 |

| 2.1.2.1.3 Alteon Networks Proprietary MIB Statistics for the NIC |    |

| 2.1.2.2 Ring Control Blocks                                      |    |

| 2.1.2.3 Event Producer Pointer                                   | 42 |

| 2.1.2.4 Receive Return Ring Producer Pointer                     | 43 |

| 2.1.2.5 Send Consumer Pointer                                    | 43 |

| 2.1.2.6 Refresh Stats Pointer                                    | 43 |

| 2.2 SBus Memory Model                                            | 44 |

| 2.3 Serial EEPROM                                                | 44 |

| 2.3.1 Reading and Writing the Serial EEPROM                      | 44 |

| 2.3.2 Data fields in the Serial EEPROM                           | 44 |

| 2.3.2.1 MAC Address                                              | 44 |

| 2.3.2.2 Software Key                                             | 44 |

| 2.3.2.3 Customer Data Area                                       | 44 |

| 2.4 Shared Rings                                                 | 45 |

| 2.4.1 Control Rings                                              | 45 |

| 2.4.1.1 Command Ring                                             | 45 |

| 2.4.1.2 Event Ring                                               | 45 |

| 2.4.2 Data Rings                                                 | 46 |

| 2.4.2.1 Send Ring                                                | 46 |

| 2.4.2.2 Extended Send Ring Handling                              | 46 |

| 2.4.2.3 Receive Rings                                            |    |

| 2.5 Interrupts                                                   |    |

| 2.5.1 Interrupt Generation                                       |    |

| 2.5.2 Interrupt Avoidance                                        |    |

| 2.5.3 Masking Interrupts                                         |    |

| 2.6 Checksum Offload                                             |    |

| 2.6.1 Preparing the NIC for Checksum Offload                     |    |

| 2.6.2 Per Packet Settings When Using Checksum Offload            |    |

| 2.6.2.1 The Send Case                                            |    |

| 2.6.2.2 The Send Case for IP Fragmented Packets                  |    |

| 2.6.2.3 Limitations                                              |    |

| 2.6.3 The Receive Case                                           |    |

| 2.7 VLAN Assist                                                  |    |

| 2.7.1 Tag Insertion for Outgoing Frames                          |    |

| 2.7.2 Tag Deletion for Incoming Frames                           |    |

| 2.8 Transmit Flow Diagram                                        |    |

| 2.9 Receive Flow Diagram                                         |    |

| 2.10 Error Processing                                            |    |

| 2.11 Frame Filtering                                             | 55 |

| 3 Data Structures                                                |    |

| 3.1 Buffer Descriptors                                           | 57 |

| 3.1.1 Receive Buffer Descriptors                                 |    |

| 3.1.2 Send Buffer Descriptors                                    |    |

| 3.2 Commands                                                     |    |

| 3.2.1 Extended Commands                                          | 61 |

|   | 3.2.2  | TG_CMD_HOST_STATE                               | 61 |

|---|--------|-------------------------------------------------|----|

|   | 3.2.3  | TG_CMD_FDR_FILTERING                            | 61 |

|   | 3.2.4  | TG_CMD_SET_RECV_PRODUCER_INDEX (OBSOLETE)       | 62 |

|   | 3.2.5  | TG_CMD_UPDATE_GENCOM_STATS                      | 62 |

|   | 3.2.6  | TG_CMD_RESET_JUMBO_RING                         | 62 |

|   | 3.2.7  | TG_CMD_SET_PARTIAL_RECV_COUNT                   | 62 |

|   | 3.2.8  | TG_CMD_ADD_MULTICAST_ADDR (OBSOLETE)            | 63 |

|   | 3.2.9  | TG_CMD_DEL_MULTICAST_ADDR (OBSOLETE)            | 63 |

|   | 3.2.10 | TG_CMD_SET_PROMISC_MODE                         | 63 |

|   | 3.2.11 | TG_CMD_LINK_NEGOTIATION                         | 64 |

|   | 3.2.12 | TG_CMD_SET_MAC_ADDR                             |    |

|   | 3.2.13 | TG_CMD_CLEAR_PROFILE                            |    |

|   | 3.2.14 | TG_CMD_SET_MULTICAST_MODE                       |    |

|   | 3.2.15 | TG_CMD_CLEAR_STATS                              |    |

|   | 3.2.16 | TG_CMD_SET_RECV_JUMBO_PRODUCER_INDEX (OBSOLETE) |    |

|   | 3.2.17 | TG_CMD_REFRESH_STATS                            |    |

|   | 3.2.18 | TG_CMD_EXT_ADD_MULTICAST_ADDR                   |    |

|   | 3.2.19 |                                                 |    |

|   |        | vents                                           |    |

|   | 3.3.1  | TG_EVENT_NIC_FIRMWARE_OPERATIONAL               |    |

|   | 3.3.2  | TG_EVENT_STATS_UPDATED                          |    |

|   | 3.3.3  | TG_EVENT_LINK_STATE_CHANGED                     |    |

|   | 3.3.4  | TG_EVENT_ERROR                                  |    |

|   | 3.3.5  | TG_EVENT_MULTICAST_LIST_UPDATED                 |    |

|   | 3.3.6  | TG_EVENT_RESET_JUMBO_RING                       | 68 |

| 4 | DEDEC  | PRMANCE TUNING                                  |    |

| 4 |        | educing the Host/NIC interaction                | 60 |

|   | 4.1.1  | Information Coalescing                          |    |

|   | 4.1.1  | Interrupt Avoidance                             |    |

|   | 4.1.3  | Receive Ring                                    |    |

|   | 4.1.4  | Send Ring                                       |    |

|   | 4.1.5  | Transmitting Latencies and Buffer Descriptors   |    |

|   | 4.1.6  | NIC Data Buffer Sizes                           |    |

|   | 4.1.7  | PCI Command Memory Write and Invalidate         |    |

|   | 4.1.8  | Memory Write and Invalidate on the Tigon ASIC   |    |

|   | 4.1.9  | Memory Write and Invalidate on the Tigon 2 ASIC |    |

|   |        | PCI Command Memory Read Multiple                |    |

|   |        | PCI Burst Length                                |    |

|   |        | hecksum Offload                                 |    |

|   |        | MA Read Errata on Tigon 2 ASICs                 |    |

|   | 4.3.1  | Problem Description                             |    |

|   | 4.3.2  | Details                                         |    |

|   | 4.3.3  | Work-around Options                             |    |

|   | 4.3.4  | Impact Observations.                            |    |

|   | 1.5.4  |                                                 | 13 |

| 5 | Firmwa | are Initialization                              |    |

|   | 5.1 Po | ower-on Bootstrap Sequence                      | 75 |

|   |        | ard Reset                                       |    |

|   |        |                                                 | 7. |

|   | 5.3 O  | peration at System Reboot                       | /5 |

|   |        | rmware Download                                 |    |

| 5.5. | 1 Runtime Program File |

|------|------------------------|

|      | Link Ready Operation   |

|      |                        |

### 6 Bibliography

## Table of Figures

| MAC Address Format                 | 14                                                                                                                                                                                                                                                                                                  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

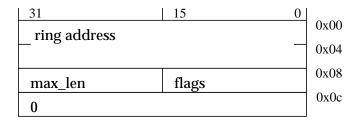

| Ring Control Block                 | 41                                                                                                                                                                                                                                                                                                  |

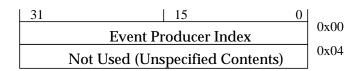

| Event Producer                     | 42                                                                                                                                                                                                                                                                                                  |

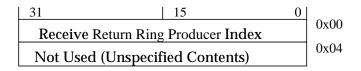

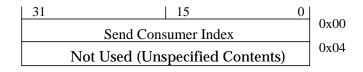

| Receive Return Ring Producer       | 43                                                                                                                                                                                                                                                                                                  |

| Send Consumer                      | 43                                                                                                                                                                                                                                                                                                  |

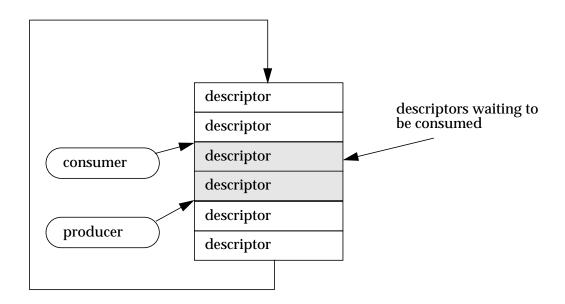

| Producer-Consumer model            | 45                                                                                                                                                                                                                                                                                                  |

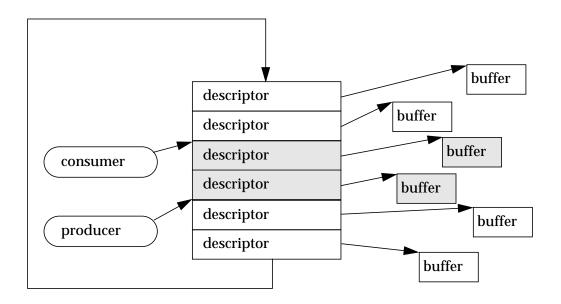

| Producer-Consumer Model with data  | 46                                                                                                                                                                                                                                                                                                  |

| Transmit Flow Diagram              | 51                                                                                                                                                                                                                                                                                                  |

| Receive Flow Diagram               | 53                                                                                                                                                                                                                                                                                                  |

| Receive Buffer Descriptor          |                                                                                                                                                                                                                                                                                                     |

| Extended Receive Buffer Descriptor | 58                                                                                                                                                                                                                                                                                                  |

| Send Buffer Descriptor             | 59                                                                                                                                                                                                                                                                                                  |

| Command Definition                 | 61                                                                                                                                                                                                                                                                                                  |

| Event Definition                   | 66                                                                                                                                                                                                                                                                                                  |

|                                    | Ring Control Block  Event Producer  Receive Return Ring Producer  Send Consumer  Producer-Consumer model  Producer-Consumer Model with data  Transmit Flow Diagram  Receive Flow Diagram  Receive Buffer Descriptor  Extended Receive Buffer Descriptor  Send Buffer Descriptor  Command Definition |

#### **Table of Tables**

| Table 1.  | LED Usage                                  | 15 |

|-----------|--------------------------------------------|----|

| Table 2.  | Shared Configuration Block                 | 18 |

| Table 3.  | PCI Configuration Registers for SBus Cards | 18 |

| Table 4.  | Shared Memory Base Register                | 19 |

| Table 5.  | Tigon Configuration/Control Region         | 19 |

| Table 6.  | Tigon Miscellaneous Host Control Register  | 20 |

| Table 7.  | Tigon Miscellaneous Local Control Register | 20 |

| Table 8.  | Tigon Miscellaneous Configuration Register | 21 |

| Table 9.  | Tigon PCI State Register                   | 21 |

| Table 10. | Tigon DMA Assist State Register            | 23 |

| Table 11. | Tigon CPU State Register                   | 23 |

| Table 12. | Tigon MAC RX State Register                | 24 |

| Table 13. | Mailbox Registers                          | 25 |

| Table 14. | General Communications Registers           | 25 |

| Table 15. | Operating Mode and Status                  | 27 |

| Table 16. | DMA Read Configuration Mode                | 28 |

| Table 17. | DMA Write Configuration Mode               | 28 |

| Table 18. | Tuning Parameters                          | 29 |

| Table 19. | NIC Tracing definitions                    | 30 |

| Table 20. | Link Negotiation Bit Definitions           | 31 |

| Table 21. | Link Negotiation Bit Definitions           | 32 |

| Table 22. | General Information Block                  | 34 |

| Table 23. | RCB Flags                                  | 41 |

| Table 24. | SBus Address Space                         | 44 |

| Table 25. | Errored Frame Flags                        | 59 |

| Table 26. | Buffer Descriptor Flags                    | 60 |

| Table 27. | TG_CMD_HOST_STATE flags                    | 61 |

| Table 28. | TG_CMD_FDR_FILTERING flags                 | 61 |

| Table 29. | TG_CMD_SET_PROMISCUOUS_MODE flags          | 63 |

| Table 30. | TG_CMD_SET_LINK_NEGOTIATION flags          | 64 |

| Table 31. | TG_CMD_SET_MULTICAST_MODE flags            | 65 |

| Table 32. | TG_EVENT_LINK_STATE_CHANGED codes          | 67 |

| Table 33. | ERROR codes                                | 67 |

| Table 34. | TG_EVENT_MULTICAST_LIST_UPDATED codes      | 68 |

| Table 35. | Memory Read Command Usage                  | 72 |

| Table 36. | Firmware Failure Locations                 | 76 |

## 1 Introduction

The Alteon Networks Gigabit Ethernet/PCI Network Interface Card (NIC) provides a full or half duplex Gigabit Ethernet interface compliant with the proposed IEEE 802.3z standard. The NIC is implemented for use in systems that support either the 32 or 64 bit wide PCI Local Bus operating at 33 MHz. The Tigon 2 equipped version of the NIC adds support for 66 MHz buses. This manual also includes documentation for a 32-bit or 64-bit SBus card using the same Tigon technology with a special bridge chip.

The NIC acts as a bus master to DMA data between the Host and the NIC. Host access to the NIC is through a shared memory segment and control structures in Host memory. The NIC has either 1 MB or 512 KB of memory depending on the hardware configuration. The NIC has either a SX fiber connector or 10/100/1000 copper connector.

The NIC performs all the necessary Gigabit Ethernet MAC and PHY layer processing. The Host software provides frames to be sent and accepts received frames. Data is managed using ring buffers. Interrupts are generated based on conditions in the Event, Send or Receive Rings and not necessarily on a per frame basis.

#### 1.1 TIGON

The Alteon Networks Gigabit Ethernet NIC is implemented by utilizing a proprietary custom Application Specific Integrated Circuit (ASIC). This ASIC, known as the Tigon ASIC or Tigon (for short), incorporates dual DMA channels, a Gigabit Ethernet MAC, the PCI Interface, and a RISC based processor. The Tigon 2 ASIC adds a second RISC processor, higher memory throughput, additional hardware offload features, and higher clock rates. Throughout this document the original Tigon chip will be referred to as Tigon or as Version 4 Tigon. The newer Tigon 2 chip will be referred to as Tigon 2 or Version 5 or Version 6 Tigon.

Version 4 (original Tigon ASIC) and Version 5 or 6 (Tigon 2 ASIC) usage are defined in this document. Different firmware for each version of the ASIC is provided in the Open Driver Kit. You can write your driver to support either ASIC or both ASICs. To support only the original version 4 ASIC please ensure that TIGON\_REV is defined to be 1 either through an include file or through your C compiler and your Makefile. To support only Version 5 and 6 of the ASIC please ensure that TIGON\_REV is defined to be 2. To support all of Version 4, Version 5, and Version 6 please ensure that TIGON\_REV is defined to be 3.

#### 1.2 Feature Set

The Alteon NIC and firmware allow a large number of host assistance features. One of these is checksum offload. The NIC can do complete checksum offload for both transmitted and received frames. This checksum offload feature allows full checksum calculation (including pseudo-headers) for IP, TCP, and UDP packets. On the transmit side the host can even set up the buffers in such a way that fragmented frames can have their UDP or TCP checksums calculated over the entire datagram. Detailed discussion of the checksum offload features can be found in section 2.6 of this document.

Other features designed to improve total throughput are available and are built into the API. These features include event coalescing and interrupt avoidance.

#### 1.3 Foundation Data Structures

#### 1.3.1 Host Addresses

The Host/NIC interface views all Host addresses as 64 bit objects, even on 32 bit hosts. On 32 bit Hosts, the upper 32 bits must be zero. These addresses are in big endian byte order.

#### 1.3.2 NIC Addresses

All of the NIC address are 32 bits long and can only be addressed via 32 bit accesses with the exception of PCI Configuration Space and PCI Configuration Registers which can be addressed as 1, 2, 3, or 4 bytes.

NOTE: Alteon Networks personnel have discovered that some PC debuggers while providing a 32 bit write command, actually perform four one-byte writes. This WILL NOT work.

#### 1.3.3 MAC Addresses

The MAC addresses are 48 bit objects which are padded to 64 bits as shown in Figure 1. [3].

| 31      | 23      | 15      | 7 0     |

|---------|---------|---------|---------|

| 0       |         | octet 0 | octet 1 |

| octet 2 | octet 3 | octet 4 | octet 5 |

Figure 1. MAC Address Format

#### 1.3.4 Endianness

The NIC is a big endian machine. The DMA engine can be configured to perform byte swaps while transferring data, control information or both. All data DMAed to and from the NIC should be in Host byte order on the Host; it is byte swapped to the proper endian during DMA. All data in the shared memory space must be big endian since the NIC is big endian. The endian configuration of the control and data DMA transfers is set by the Host in the Operating Mode and Status register (See "Operating Mode", section 2.1.1.4.4). In addition, all data that is placed into the NIC through PIOs needs to be in big endian format. This is controlled through the use of the Miscellaneous Host Control register (See "Tigon Miscellaneous Host Control Register", section 2.1.1.2.1).

There is also the concept of "word endianness" in the NIC. Data is either dealt with as a 32 bit quantity or as a byte stream. In either case, since the memory subsystem of the NIC is a 64 bit memory subsystem, the host must ensure that the words are reversed. This is done by setting the proper word swapping bits in the Miscellaneous Host Control register (See "Tigon Miscellaneous Host Control Register", section 2.1.1.2.1) and the Operating Mode and Status register (See "Operating Mode", section 2.1.1.4.4).

The following is a brief discussion to help you figure out how to set these bytes on your system.

I

Rule 1: Since our basic unit of interaction is a 32 bit quantity the bits show up the same whether they are big-endian or little-endian.

Rule 2: PCI is defined as a little-endian bus.

Given these rules, lets look at what typically happens on little-endian hosts. Since the PCI bus is defined as little-endian and the memory system is defined as little-endian most (all?) little-endian systems pass the bytes through to the bus in the same order that they appear in memory. So for 32 bit quantities (as everything in the data structures is treated) there is no need to byte swap (the Misc Host Control register is set to not swap and the TG\_CFG\_MODE\_SWAP\_BD bit is not set).

For network data (which is defined as a byte stream) the data is presented in little-endian format (byte swapped) so the data must be byte swapped (TG\_CFG\_MODE\_SWAP\_DATA).

Now, let's look at "most" big-endian hosts. Since the PCI bus is defined as little-endian, and the memory system is defined as big-endian, the host is often built to "pre-swap" all the data that travels across the bus so it shows up in the "right order". But this swapping is really "wrong" for 32 bit quantities (we noted in rule 1 that these are always the same). So in this case we have to set byte swapping on for all data structures (the byte swapping bit in the Misc Host Control register and the TG\_CFG\_MODE\_SWAP\_BD bit). Data is still byte oriented, but it is in big-endian format. Since these hosts pre-swap the data we must also byte swap data in order to get it back into the right order (hence the TG\_CFG\_MODE\_SWAP\_DATA bit).

One more endian issue has to do with word swapping. This can effect both addresses in the shared memory region and those in the host. For little endian systems that have no way of doing a 64 bit write to the shared memory put support 64 bit hardware address (e.g. some Intel x86 systems) the high order 32 bits will have to be swapped with the low order 32 bits. This is because the NIC wants all 64 bits in big endian format and the host has them in little endian format. If a 64 bit transfer were done then the words would be swapped by the hardware, but if no 64 bit instruction can be used the host code must explicitly swap them. For little endian systems with 64 bit addresses the two words of addresses in host memory will have to be swapped to create a big endian look in the host.

## 1.4 LED Meanings

There are two LEDs on Gigabit NICs. A "Link" LED and a "Data" LED. In general, the link LED indicates that the link is up and the data LED flashes when there is data movement on the NIC. The NIC enabled means that a TG\_CMD\_HOST\_STATE UP command has been issued to the NIC (See "TG\_CMD\_HOST\_STATE", section 3.2.2).

Table 1. LED Usage

| Link LED solid                 | Data LED with Solid<br>Link LED | Data LED by itself                       | Slow Flashing Link<br>LED                           |

|--------------------------------|---------------------------------|------------------------------------------|-----------------------------------------------------|

| Link is active, NIC is enabled | Data activity on the NIC        | Fault condition, firm-<br>ware is halted | NIC is disabled, but firmware is loaded and running |

## 2 Architecture

## 2.1 Memory Model

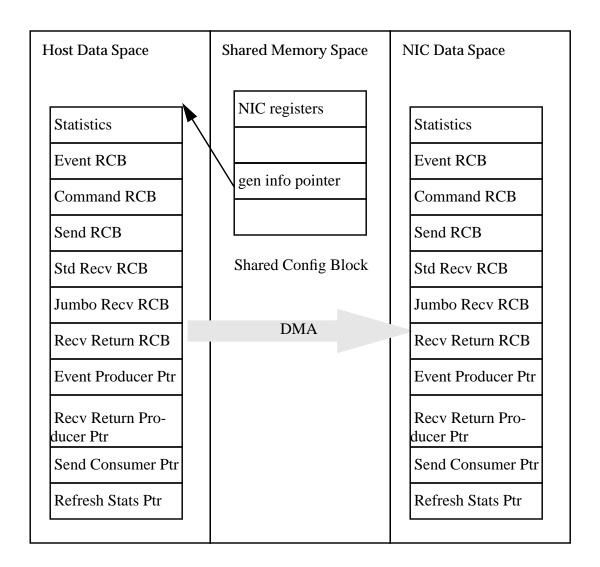

The NIC manages data structures in Host memory using DMA and the following two control blocks:

- the Shared Configuration Block, and

- the General Information Block.

## 2.1.1 Shared Configuration Block

This is a 16K byte shared memory region of Host mapped memory as shown in Table 2.

NOTE: Bits and fields that are meaningful only for Tigon 2 are indicated with the words (Tigon 2 only) and are lightly shaded if described in a Table.

All registers in this block can be shared between the Host and the NIC, however some are used operationally by the Host while others are used operationally by the NIC. All registers are 32 bits long.

Table 2. Shared Configuration Block

| Shared Configuration Block    | Address         |

|-------------------------------|-----------------|

| PCI Configuration Region      | 0x0000 - 0x003F |

| Tigon Configuration Region    | 0x0040 - 0x04FF |

| Mailboxes                     | 0x0500 - 0x05FF |

| General Communications Region | 0x0600 - 0x07FF |

| Local Memory Window           | 0x0800 - 0x0FFF |

| Reserved                      | 0x1000 - 0x3FFF |

#### 2.1.1.1 PCI Configuration Region

Please refer to the PCI Local Bus Specifications[1] for details. Vendor Subsystem IDs are supported only in Tigon 2 (Version 5 or 6) ASICs

#### 2.1.1.1.1 PCI Configuration Region Setup for SBus Cards

Since the SBus card uses a bridge chip, the PCI bus configuration region will not be set up by the system's BIOS. The following registers must be set correctly. The SBus bridge chip only allows accesses in 4 byte quantities. All these registers should be set using the PCI Config region of the SBus address space (See "SBus Memory Model", section 2.2).

Table 3. PCI Configuration Registers for SBus Cards

| PCI Configuration Registers | Address     |  |

|-----------------------------|-------------|--|

| Command/Status Register     | 0x04 - 0x07 |  |

| Latency Timer, etc.         | 0x0C - 0x0F |  |

| Shared Memory Base          | 0x10 - 0x13 |  |

#### 2.1.1.1.1 Command/Status Register

This register is a pair of registers that indicate the Status and the Command registers of the PCI Configuration space. This should be set to the value 0x02000006 in big endian format.

#### 2.1.1.1.2 Latency Timer, etc. Register

This register is really four PCI configuration registers. It should be set to 0xFFFFFFF.

#### 2.1.1.1.3 Shared Memory Base Register

This register specifies the addresses that the SBus - PCI bus chip will generate when data is placed in the 16 KB shared memory region of the SBus address space. It also specifies to the PCI chip where it should respond to shared memory accesses. It is critical that this space not ever be used as a DMA address or the PCI chip will respond to its own DMA requests.

Table 4. Shared Memory Base Register

| Bit        | Name          | Access | Description                                                                                                                                  |

|------------|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000000FF | Reserved      | W/O    | These bits must be set to zero.                                                                                                              |

| 0x00000100 | Chaining      | W/O    | If set the NIC will not perform SBus chaining.                                                                                               |

| 0x00000600 | Transfer Size | W/O    | If '00' do 16 word/dword transfers, if '01' do 8 word/dword transfers, if '10' do 4 word/dword transfers, if '11' do 1 word/dword transfers. |

| 0x00000800 | Reset         | W/O    | If set the bridge chip is held in reset.                                                                                                     |

| 0x00003000 | Reserved      | W/O    | This bits must be set to zero.                                                                                                               |

| 0xFFFFC000 | Base Address  | R/W    | These bits specify the base address used by the bridge chip and the Tigon chip for shared memory accesses.                                   |

#### 2.1.1.2 Tigon Configuration/Control Region

The Tigon Configuration/Control Region is composed of several 32 bit registers. See Table 5 for details.

Table 5. Tigon Configuration/Control Region

| Tigon Configuration Region                             | Address       |

|--------------------------------------------------------|---------------|

| Tigon Miscellaneous Host Control                       | 0x040 - 0x043 |

| Tigon Miscellaneous Local Control                      | 0x044 - 0x047 |

| Tigon Miscellaneous Configuration (Tigon 2 only)       | 0x050 - 0x053 |

| Tigon PCI State                                        | 0x05C - 0x05F |

| Tigon Window Base Address                              | 0x068 - 0x06B |

| Tigon Window Data                                      | 0x06C - 0x06F |

| Tigon DMA Assist State                                 | 0x11C - 0x11F |

| Tigon CPU State                                        | 0x140 - 0x143 |

| Tigon CPU Program Counter                              | 0x144 - 0x147 |

| Tigon Internal SRAM Address                            | 0x154 - 0x157 |

| Tigon Internal SRAM Data                               | 0x158 - 0x15B |

| Tigon General Purpose Registers                        | 0x180 - 0x1FF |

| Tigon MAC RX State                                     | 0x220 - 0x223 |

| Tigon CPU Control (CPU B) (Tigon 2 only)               | 0x240 - 0x243 |

| Tigon CPU Program Counter (CPU B) (Tigon 2 only)       | 0x244 - 0x247 |

| Tigon Internal SRAM Address (CPU B) (Tigon 2 only)     | 0x254 - 0x257 |

| Tigon Internal SRAM Data (CPU B) (Tigon 2 only)        | 0x258 - 0x25B |

| Tigon General Purpose Registers (CPU B) (Tigon 2 only) | 0x280 - 0x2FF |

#### 2.1.1.2.1 Tigon Miscellaneous Host Control Register

The Miscellaneous Host Control register is used to control various functions within the Tigon normally controlled from the host interface.

All bits of the Miscellaneous Host Control register not specified in Table 6 must be set to 0.

Table 6. Tigon Miscellaneous Host Control Register

| Bit        | Name                       | Access | Description                                                                                                                                                                                      |

|------------|----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000001 | Interrupt State            | R/O    | This bit reflects the state of the PCI IntA Output pin                                                                                                                                           |

| 0x00000002 | Clear Interrupt            | W/O    | This bit clears the host PCI Interrupt IntA                                                                                                                                                      |

| 0x00000008 | Reset                      | R/W    | Force a complete hardware reset, except PCI Configuration Registers (0x0 - 0x3F)                                                                                                                 |

| 0x0000010  | Enable Endian Byte<br>Swap | R/W    | Enable endian byte swapping when accessing Tigon through target interface                                                                                                                        |

| 0x00000020 | Enable Endian Word<br>Swap | R/W    | Enable endian word swapping when accessing Tigon through target interface.                                                                                                                       |

| 0x00000040 | Mask Interrupts            | R/W    | Mask interrupts while set. Pending interrupts will be generated when the bit is cleared. If the interrupt line is asserted it will be deasserted when this bit is set. (Tigon 2 Revision 6 only) |

| 0xF0000000 | Chip Version Mask          | R/O    | This is a 4-bit field which carries the Version of the Tigon ASIC. It can contain 4 (Tigon) or 5 or 6 (Tigon 2)                                                                                  |

#### 2.1.1.2.2 Tigon Miscellaneous Local Control Register

The Miscellaneous Local Control register is used to control various functions within the Tigon normally controlled from the internal processor. All bits are set to zero during reset.

Change only the Miscellaneous Local Control register bits specified in Table 7. All other bits must be left unchanged.

Table 7. Tigon Miscellaneous Local Control Register

| Bit        | Name                                | Access | Description                                                                                                                                                                                                          |

|------------|-------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000010  | Enable EEPROM<br>Write              | R/W    | Enables writing to EEPROM Region                                                                                                                                                                                     |

| 0x00000200 | SRAM Bank 256K                      | R/W    | Each bank of SRAM is 256K instead of 1M bytes (Tigon 1 only)                                                                                                                                                         |

| 0x00000300 | SRAM Bank Size                      | R/W    | A two bit field to indicate the size of the SRAM bank. 0 is for a single bank. 1 is for a bank size of 1M. 2 is for a bank size of 512KB. 3 is for a bank size of 256KB.PCI NICs have 512KB per bank. (Tigon 2 only) |

| 0x00004000 | Local Address21                     | R/W    | Used for bank switching flash memory by directly controlling local address bit 21                                                                                                                                    |

| 0x00008000 | Local Address22                     | R/W    | Used for bank switching flash memory by directly controlling local address bit 22                                                                                                                                    |

| 0x00080000 | SBus Write Error                    | R/O    | Indicates there was an SBus Write Error                                                                                                                                                                              |

| 0x00100000 | Serial EEPROM clock<br>Output       | R/W    | Directly controls the clock output pin                                                                                                                                                                               |

| 0x00200000 | Serial EEPROM Data<br>Output Enable | R/W    | When Asserted, Tigon drives the value of Serial EEPROM data output.                                                                                                                                                  |

I

Table 7. Tigon Miscellaneous Local Control Register

| Bit        | Name                         | Access | Description                                       |

|------------|------------------------------|--------|---------------------------------------------------|

| 0x00400000 | Serial EEPROM Data<br>Output | R/W    | Value of data to drive out when output enabled    |

| 0x00800000 | Serial EEPROM Data<br>Input  | R/O    | Input from bi-directional serial EEPROM data pin. |

NOTE: Writes to the Tigon Miscellaneous Local Control Register should only be performed when the internal processor is halted.

#### 2.1.1.2.3 Tigon Miscellaneous Configuration Register

The Miscellaneous Configuration register is used to control various functions within the Tigon normally controlled from the internal processor at configuration time. All bits are set to zero during reset. This register is only available on the Tigon 2 ASIC.

Change only the Miscellaneous Configuration register bits specified in Table 7. All other bits must be left unchanged.

Table 8. Tigon Miscellaneous Configuration Register

| Bit        | Name                           | Access | Description                                                         |

|------------|--------------------------------|--------|---------------------------------------------------------------------|

| 0x00100000 | Set Synchronous<br>SRAM timing | R/W    | Must be set for boards that contain synchronous SRAM (Tigon 2 only) |

NOTE: Writes to the Tigon Miscellaneous Configuration Register should only be performed when the internal processor is halted.

#### 2.1.1.2.4 Tigon PCI State Register

The PCI State register is used to control various functions within the Tigon associated with PCI Interface. All bits are set to zero during reset.

All of the PCI State register bits not specified in Table 9 must be set to 0.

Table 9. Tigon PCI State Register

| Bit(s)     | Name           | Access | Description                                                                                                                                                                                                                                            |

|------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000001  | Force Reset    | W/O    | Will force an immediate reset of the PCI Interface. All state information within the PCI Configuration registers will be lost. This bit is self clearing.                                                                                              |

| 0x00000002 | Provide Length | R/W    | Use non-standard PCI interface which provides transfer length indication. On PCI cards there is never any reason to set this bit.                                                                                                                      |

| 0x0000001C | Read Max DMA   | R/W    | This is a 3-bit field. Encoded bits which force termination of PCI read operations at any of the following boundaries: Disable (000), 4 (001), 16 (010), 32 (011), 64 (100), 128 (101), 256 (110), 1K (111). For SBus cards this should be set to 100. |

Table 9. Tigon PCI State Register

| Bit(s)     | Name                                    | Access     | Description                                                                                                                                                                                                                                                                                                |

|------------|-----------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000000E0 | Write Max DMA                           | R/W        | This is a 3-bit field. Encoded bits which force termination of PCI write operations at any of the following boundaries: Disable (000), 4 (001), 16 (010), 32 (011), 64 (100), 128 (101), 256 (110), 1K (111). For SBus cards this should be set to 100.                                                    |

| 0x0000FF00 | Minimum DMA                             | R/W        | This 8 bit field contains the minimum number of PCI words each DMA channel is allowed to keep the PCI bus without allowing accesses by the other DMA channel. This guarantees a minimum PCI usage rather than the usual alternate per burst behavior. Due to hardware bugs this field MUST be set to zero. |

| 0x00010000 | FIFO Retry enable                       | R/W        | Enable PCI retry response to PCI target accesses to FIFO when FIFO cannot complete operation. This bit is not used for normal operation.                                                                                                                                                                   |

| 0x00020000 | Use<br>Mem_Read_Multiple<br>PCI Command | R/W        | Use Memory Read Multiple command in place of Memory Read Line for DMA reads.                                                                                                                                                                                                                               |

| 0x00040000 | No Word Swap (Read)<br>DMA              | R/W        | Disable word swapping for all read DMA Transactions. For Tigon 2 ASICs this controls both the read and the write DMA channels.                                                                                                                                                                             |

| 0x00080000 | No Word Swap Write DMA                  | R/W        | Disable word swapping for all write DMA Transactions. Only for the original Tigon ASIC.                                                                                                                                                                                                                    |

| 0x00080000 | 66 MHz Bus indication                   | R/O        | Set if the card has negotiated for a 66 MHz bus clock speed. Tigon 2 ASIC only.                                                                                                                                                                                                                            |

| 0x00100000 | 32-bit PCI bus                          | R/O or R/W | Current Host is providing only a 32-bit PCI Bus. On Tigon 2 ASICs can be written to override systems where 64 bit operation has been negotiated incorrectly.                                                                                                                                               |

| 0x00800000 | Enable all Byte<br>Enables              | R/W        | This bit must be used with Tigon 2 ASIC SBus cards and must not be set on any other card. It causes all the PCI byte enables to be set on every WRITE DMA.                                                                                                                                                 |

| 0x0F000000 | PCI Read Command                        | R/W        | This is a 4-bit field. The NIC uses this command for all PCI read transactions of <3 words or half the cache line size if set. This field should normally be set to 6 (Memory Read).                                                                                                                       |

| 0xF0000000 | PCI Write Command                       | R/W        | This is a 4-bit field. The NIC uses this command for all PCI write transactions. This field should normally be set to 7 (Memory Write). See "PCI Command Memory Write and Invalidate", section 4.6 for information on using the Memory Write and Invalidate.                                               |

#### 2.1.1.2.5 Tigon Window Base Address Register

The Window Base Address register defines the local memory address (from the point of view of the NIC's internal processor) which is the base for the 2 Kilobyte window provided by the Tigon (See "Shared Configuration Block", section Table 2. and See "Local Memory Window", section 2.1.1.5.) This register may contain any valid local memory address, but the usage of the least

significant 11-bits varies depending on how the local memory is addressed. If the 2 Kilobyte window is used, then the least significant 11-bits are ignored and are substituted with zeros. If Window Data register is referenced, then the entire Window Address register is used to indicate the local memory address of the operation.

I

**NOTE:** The Window Base Address register cannot be used by the host to access registers internal to Tigon. It is only used to access memory internal to Tigon.

The Window Base Address register (in conjunction with the local memory window) is used to download the firmware into the NIC (See "Firmware Download", section 5.4). It is also used to address the Send Ring. (See "Send Ring", section 2.4.2.1.)

#### 2.1.1.2.6 Tigon Window Data Register

The Window Data register is normally used to access locations in the local memory when the actual 2k Byte local memory window provided by the Tigon is unavailable. Only 32-bit operations are supported on this register.

The Window Data register (in conjunction with Window Base Address Register) provides an indirect method to access the entire local memory address space.

#### 2.1.1.2.7 Tigon DMA Assist State Register

The DMA Assist State register is used to control the DMA assist logic within the Tigon. The DMA assist logic allows the NIC to queue DMAs that will then be dequeued and executed by the hardware. Stopping the DMA Assist does not stop the current DMA it only prevents the next queued DMA from starting.

All of the DMA Assist State register bits not specified in Table 10 must be left unchanged.

Table 10. Tigon DMA Assist State Register

| Bit        | Name   | Access | Description                                                                |

|------------|--------|--------|----------------------------------------------------------------------------|

| 0x00000001 | Enable | R/W    | Enable DMA Assist Logic                                                    |

| 0x00000002 | Pause  | R/W    | Stop DMA Assist Logic. Does not affect the DMA Transfers which are active. |

#### 2.1.1.2.8 Tigon CPU State Register

The CPU State register controls miscellaneous functions associated with the CPU in addition to indicating the state of the processor. Alteon Networks uses these bits a great deal to implement a firmware debugger. In general, a driver writer should not need to adjust these bits directly. On the Tigon 2 ASIC there are two CPUs (CPU A and CPU B). There is a CPU State Register for each CPU.

Table 11. Tigon CPU State Register

| Bit        | Name            | Access | Description                                                                                                                                                                                                |

|------------|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000001 | Reset CPU       | R/W    | Self clearing bit which resets the internal CPU.                                                                                                                                                           |

| 0x00000002 | Single Step CPU | R/W    | Advances the CPU's Program Counter one cycle. If the halting condition (e.g. an invalid instruction at the location) still exists then the CPU will again halt, otherwise it will resume normal operation. |

Table 11. Tigon CPU State Register

| Bit        | Name     | Access | Description                                                                                            |

|------------|----------|--------|--------------------------------------------------------------------------------------------------------|

| 0x0000010  | ROM Fail | R/W    | Asserted on reset and cleared by ROM code after successfully loading code from serial EEPROM or Flash. |

| 0x00010000 | Halt CPU | R/W    | Set by the external Host to halt the internal CPU.                                                     |

#### 2.1.1.2.9 Tigon CPU Program Counter Register

The CPU Program Counter register points to the instruction which is being fetched by the internal processor. It normally changes every clock cycle during normal execution. This register can be written by the host only when the processor has been halted. On the Tigon 2 ASIC there are two CPUs (CPU A and CPU B). There is a CPU Program Counter for each CPU.

#### 2.1.1.2.10 Tigon Internal SRAM Address Register

This register is analogous to the Tigon Window Base Register for the accessing the Internal SRAM. One difference is that the memory can only be accessed through the Tigon Internal SRAM Data Register. That is, there is no equivalent to the Local Memory Window. On the Tigon 2 ASIC there are two CPUs (CPU A and CPU B). There is a Tigon Internal SRAM Address Register for each CPU. The size of the Internal SRAM is 2 KB on the original Tigon, 16 KB on CPU A of Tigon 2, and 8 KB on CPU B of Tigon 2. The local memory address of the Internal SRAM begins at 0xC00000.

#### 2.1.1.2.11 Tigon Internal SRAM Data Register

This register is analogous to the Tigon Window Data Register.

#### 2.1.1.2.12 Tigon General Purpose Registers

You can access the internal registers of the Tigon's CPU via the register file. There are 32 registers. On the Tigon 2 ASIC there are two CPUs (CPU A and CPU B). There is a CPU Register File for each CPU.

#### 2.1.1.2.13 Tigon MAC RX State Register

The MAC RX state register is used to control and monitor the Ethernet receive interface of the Tigon.

All of the MAC RX state register bits not specified in Table 12 must be left unchanged.

Table 12. Tigon MAC RX State Register

| Bit        | Name                         | Access | Description                                                                    |

|------------|------------------------------|--------|--------------------------------------------------------------------------------|

| 0x00000004 | Stop RX After Next<br>Packet | R/W    | Setting this bit disables the Receive MAC gracefully at next inter-packet gap. |

#### 2.1.1.3 Mailboxes

This is a 256 byte region which contains 32 sixty-four bit registers. These registers are called Mailbox Registers (or Mailboxes). When a value is stored in the least significant 32 bits of these registers, an event (known as Mailbox Event) is generated to the Tigon Internal Processor.

In the present version of the API, only the first six Mailboxes are used. Others are reserved for future enhancements.

**Table 13. Mailbox Registers**

| Mailboxes                                                  | Address       |

|------------------------------------------------------------|---------------|

| "Host In Interrupt Handler" (Mailbox 0)                    | 0x500 - 0x507 |

| Command Producer Index (Mailbox 1)                         | 0x508 - 0x50F |

| Send Producer Index (Mailbox 2)                            | 0x510 - 0x517 |

| Standard Receive Producer Index (Mailbox 3) (Tigon 2 only) | 0x518 - 0x51F |

| Jumbo Receive Producer Index (Mailbox 4) (Tigon 2 only)    | 0x520 - 0x527 |

| Mini Receive Producer Index (Mailbox 5) (Tigon 2 only)     | 0x528 - 0x52F |

| Reserved (Mailbox 6- 31)                                   | 0x530 - 0x5FF |

#### 2.1.1.3.1 Host In Interrupt Handler

The NIC firmware uses this register to determine if it should interrupt the Host. A value of 1 in this register means the Host is presently handling Events, and should not be interrupted. Every time the Host enters the Interrupt Handler, this register must be set to 1. Once the Host is done processing all the events, it must set this register to 0. This register must be initialized to 0.

**NOTE:** Writing any value into Mailbox Register 0 (the Host In Interrupt Handler mailbox) has a side effect of clearing the PCI Interrupt.

#### 2.1.1.3.1.1 Command Producer Index

The Command Producer Index register (Mailbox 1), contains the index of the next command in the Command Ring that will be produced. Host software writes this register whenever the command ring is updated. This register must be initialized to 0.

#### 2.1.1.3.1.2 Send Producer Index

The Send Producer Index register (Mailbox 2), contains the index of the next buffer descriptor that will be produced. Host software writes this register whenever the send ring is updated. This register must be initialized to 0.

#### 2.1.1.4 General Communications Region

These registers are active when the firmware is loaded and running. The registers are used in communication between the host and the processor internal to the Tigon chip. The area is 512 bytes long. Data in this area must be accessed 32 bits at a time.

Table 14 shows the mapping of registers in this area.

**Table 14. General Communications Registers**

| General Communications Registers      | Address       |

|---------------------------------------|---------------|

| MAC address                           | 0x600 - 0x607 |

| General Information Pointer           | 0x608 - 0x60F |

| Multicast MAC Address Transfer Buffer | 0x610 - 0x617 |

| Operating Mode and Status             | 0x618 - 0x61B |

| DMA Read Configuration                | 0x61C - 0x61F |

**Table 14. General Communications Registers**

| General Communications Registers | Address       |

|----------------------------------|---------------|

| DMA Write Configuration          | 0x620 - 0x623 |

| Transmit Buffer Ratio            | 0x624 - 0x627 |

| Event Consumer Index             | 0x628 - 0x62B |

| Command Consumer Index           | 0x62C - 0x62F |

| Tuning Parameters                | 0x630 - 0x64F |

| NIC Trace Pointer                | 0x650 - 0x653 |

| NIC Trace Start                  | 0x654 - 0x657 |

| NIC Trace Length                 | 0x658 - 0x65B |

| ifIndex                          | 0x65C - 0x65F |

| ifMtu                            | 0x660 - 0x663 |

| Mask Interrupts                  | 0x664 - 0x667 |

| Gigabit Link State               | 0x668 - 0x66B |

| 10/100 Link State                | 0x66C - 0x66F |

| Reserved(4)                      | 0x670 - 0x67F |

| Receive Return Consumer Index    | 0x680 - 0x683 |

| Reserved(31)                     | 0x684-0x6ff   |

| Command Ring                     | 0x700 - 0x7FF |

#### 2.1.1.4.1 MAC Address

The MAC Address register contains the MAC address of the NIC. It is in MAC address format (see Figure 1). This register must be initialized by the Host prior to starting the firmware. It is usually the MAC address extracted by the Host from the NIC's EEPROM.

The MAC address placed here is only read at two times by the NIC firmware. It is read at initialization and it is read when a TG\_CMD\_SET\_MAC\_ADDR command is issued (See "TG\_CMD\_SET\_MAC\_ADDR", section 3.2.12.)

#### 2.1.1.4.2 General Information Pointer

The General Information Pointer register contains the 64 bit Host address of the General Information page in Host memory. This register must be initialized by the Host prior to starting the firmware. Once the firmware has initialized, it does not reference the General Information pointer again.

#### 2.1.1.4.3 Multicast MAC Address Transfer Buffer (OBSOLETE)

The Multicast MAC Address Transfer Buffer is where the host places the multicast MAC Address to be added or deleted from the NIC's multicast list, using the TG\_CMD\_ADD\_MULTICAST\_ADDR or the TG\_CMD\_DEL\_MULTICAST\_ADDR commands. It is in MAC address format (see figure 1).

The use of this buffer has been obsoleted by the new TG\_CMD\_EXT\_ADD\_MULTICAST\_ADDR and the TG\_CMD\_EXT\_DEL\_MULTICAST\_ADDR commands.

#### 2.1.1.4.4 Operating Mode

I

The Operating Mode register sets various operational modes in the firmware.

**Table 15. Operating Mode and Status**

| Bit        | Name             | Description                                                                                                                                                                                                       |

|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000002 | BYTE_SWAP_BD     | Byte swap buffer descriptors and events when DMAing them to and from the Host.                                                                                                                                    |

| 0x00000004 | WORD_SWAP_BD     | This bit is not operational in the current release of firmware, but should be set to one in case it should ever be enabled in future revisions.                                                                   |

| 0x00000008 | WARN             | Enables warnings through events from the firmware. There are no operational differences when setting this bit currently. It is recommended that this bit be set for possible future enhancements to the firmware. |

| 0x0000010  | BYTE_SWAP_DATA   | Byte swap data when DMAing it to and from the Host.                                                                                                                                                               |

| 0x00000040 | 1_DMA_ACTIVE     | Program the interface to activate only one DMA Channel at a time, i.e. either Read or Write at a time, not both. It is recommended that this bit not be set. On SBus drivers, this bit MUST be set to One.        |

| 0x00000100 | SBUS             | Must be set for SBus cards. Must not be set for non-SBus cards.                                                                                                                                                   |

| 0x00000200 | DONT_FRAG_JUMBOS | Don't split received Jumbo frames across multiple standard sized buffer descriptors if no jumbo sized buffer descriptors are available.                                                                           |

| 0x00000400 | INCLUDE_CRC      | Include the CRC on all packets passed to the host and in the length field of the buffer descriptor.                                                                                                               |

| 0x00000800 | ALLOW_BAD_FRAMES | DMA bad frames and associated receive buffer descriptors for frames that have errors. The error is indicated in the receive buffer descriptor. (See See "Receive Buffer Descriptors", section 3.1.1.)             |

| 0x00001000 | DONT_RUPT_EVENTS | Never generate interrupts when the event producer index is updated.                                                                                                                                               |

| 0x00002000 | DONT_RUPT_SENDS  | Never generate interrupts when the send consumer index is updated.                                                                                                                                                |

| 0x00004000 | DONT_RUPT_RECVS  | Never generate interrupts when the receive return producer index is updated.                                                                                                                                      |

| 0x40000000 | FATAL            | Enables fatal error indication through events. There are no operational differences when setting this bit currently. It is recommended that this bit be set for possible future enhancements to the firmware      |

#### 2.1.1.4.5 DMA Read Configuration

The NIC supports both 32-bit and 64-bit interfaces. Some Hosts may want to use 32-bit interface while others may want 64-bit mode. The DMA Read Configuration register allows the Host to program the interface appropriately. Additionally, the this register offers flexibility to control when the DMA engine should make a request for PCI operation.

The DMA read configuration register must be set by the Host based upon the interface it wishes the NIC to use while reading data from the Host Memory. Please refer to Table 16 for the appropriate values.

Table 16. DMA Read Configuration Mode

| Bit(s)     | Name             | Description                                                                                                                                                                                                                                                                        |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000008 | FORCE_32_BIT_PCI | If set, force PCI Operation to be performed as if on a 32-bit PCI Bus. By default the bus will "self detect."                                                                                                                                                                      |

| 0x000001F0 | Threshold        | This is a five bit field and represents the number of empty words in the FIFO before the DMA channel requests a PCI operation. The Host must set a value between 1 - 16. It is recommended to use a value of 8. SBus Driver Note: Use threshold value of 8 bytes for SBus Drivers. |

#### 2.1.1.4.6 DMA Write Configuration

The NIC supports both 32-bit and 64-bit interfaces. Some Hosts may want to use 32-bit interface while others may want 64-bit mode. The DMA Read Configuration register allows the Host to program the interface appropriately. Additionally, the this register offers flexibility to control when the DMA engine should make a request for PCI operation.

The DMA Write Configuration register must be set by the Host based upon the interface it wishes the NIC to use while writing data into the Host Memory. Please refer to Table 17 for appropriate values.

**Table 17. DMA Write Configuration Mode**

| Bit(s)     | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000008 | FORCE_32_BIT_PCI | If set, force PCI Operation to be performed as if on a 32-bit PCI Bus. By default the bus will "self detect."                                                                                                                                                                                                                                                                                                            |

| 0x000001F0 | Threshold        | This is a five bit field and represents the number of empty words in the FIFO before the DMA channel requests a PCI operation. Once the last word to be written to the host has been placed into the FIFO, the host bus will be requested until the FIFO goes empty. The Host must set a value between 1 - 16. It is recommended to use a value of 8. SBus Driver Note: Use threshold value of 8 bytes for SBus Drivers. |

#### 2.1.1.4.7 Transmit Buffer Ratio

This register is used to indicate the ratio of the remaining memory in the NIC that should be devoted to Transmit Buffer vs. Receive Buffer. The bottom 7 bits are used to indicate the ratio in 1/64th increments. For example, setting this value to 16 will set the transmit buffer to 1/4 of the remaining buffer space. In no cases will the Transmit or Receive buffer be reduced below 68 KB. For a 1 MB NIC the approximate total space for data buffers is 800 KB. For a 512 KB NIC that number is 300 KB.

#### 2.1.1.4.8 Event Consumer Index

The Event Consumer Index register contains the index of the next event in the Event Ring that will be consumed. The Host writes this register whenever an event is consumed. This register must be initialized to 0.

#### 2.1.1.4.9 Command Consumer Index

The Command Consumer Index register contains the index of the next command in the Command Ring that will be consumed. The NIC writes this register whenever a command is consumed. This register must be initialized to 0.

#### 2.1.1.4.10 Tuning Parameters

These are the tuning parameters that may be modified by the Host at any time to tune the NIC firmware.

**Table 18. Tuning Parameters**

| Tuning Parameters         | Offset |

|---------------------------|--------|

| Receive coalesced ticks   | 0x00   |

| Send coalesced ticks      | 0x04   |

| Stat ticks                | 0x08   |

| Send max coalesced BDs    | 0x0C   |

| Receive max coalesced BDs | 0x10   |

| NIC tracing               | 0x14   |

| Gigabit Link Negotiation  | 0x18   |

| 10/100 Link Negotiation   | 0x1c   |

#### 2.1.1.4.10.1 Receive Coalesced Ticks

The Receive Coalesced Ticks register contains the number of clock ticks (of 1 microseconds each) that must elapse before the NIC DMAs the receive return producer pointer to the Host and generates an interrupt. This tunable parameter works in conjunction with the Receive Max Coalesced BDs tunable parameter. This NIC will return the receive return producer pointer to the Host when either of the thresholds is exceeded. A value of 0 means that this parameter is ignored and Receive BDs will only be returned when the Receive Max Coalesced BDs value is reached. This register must be initialized by the Host.

#### 2.1.1.4.10.2 Send Coalesced Ticks

The Send Coalesced Ticks register contains the number of clock ticks (of 1 microseconds each) that must elapse before the NIC DMAs the send consumer pointer to the Host and generates an interrupt. This tunable parameter works in conjunction with the Send Max Coalesced BDs tunable parameter. This NIC will return the send consumer pointer to the Host when either of the thresholds is exceeded. A value of 0 means that this parameter is ignored and Send BDs will only be returned when the Send Max Coalesced BDs value is reached. This register must be initialized by the Host. For hosts that need to recover their send buffers this value should be set a value that will allow the Host to recover their send buffers in a reasonable time period. For hosts that do not need to recover their send buffers this value should be set to zero.

#### 2.1.1.4.10.3 Stat Ticks

The Stat Ticks register contains the number of clock ticks (of 1 microseconds each) that must elapse before the NIC DMAs the statistics block to the Host and generates a STATS\_UPDATED event. If set to zero then statistics are never DMAed to the Host. This register must be initialized by the Host. It is recommended that this value be set to a high enough frequency to not mislead someone reading statistics refreshes. Several times a second is enough.

Ţ

**NOTE:** The one microsecond clock tick referenced above is a nominal time and the actual hardware may not provide granularity to this level. For example, on Tigon 2 (Revision 6) cards with release 12.0 the clock granularity is 5 microseconds.

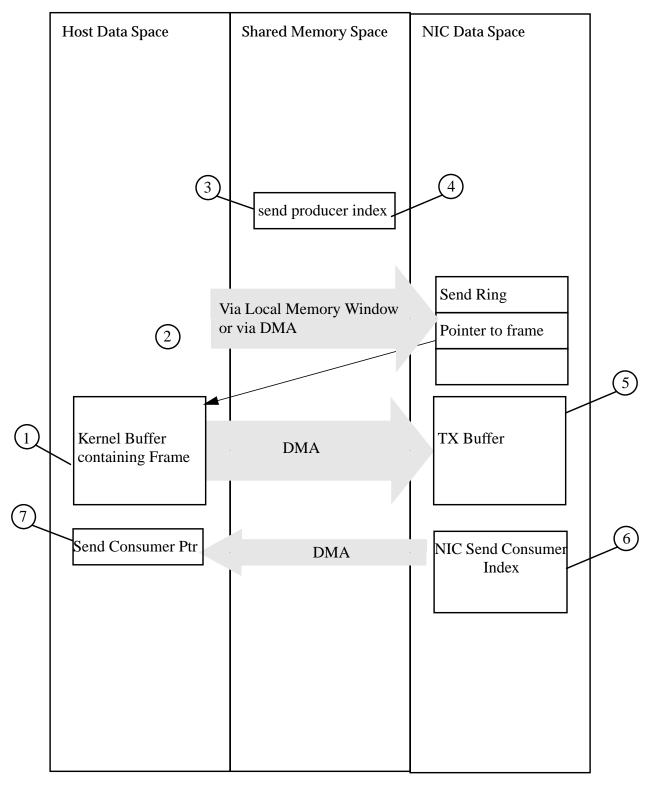

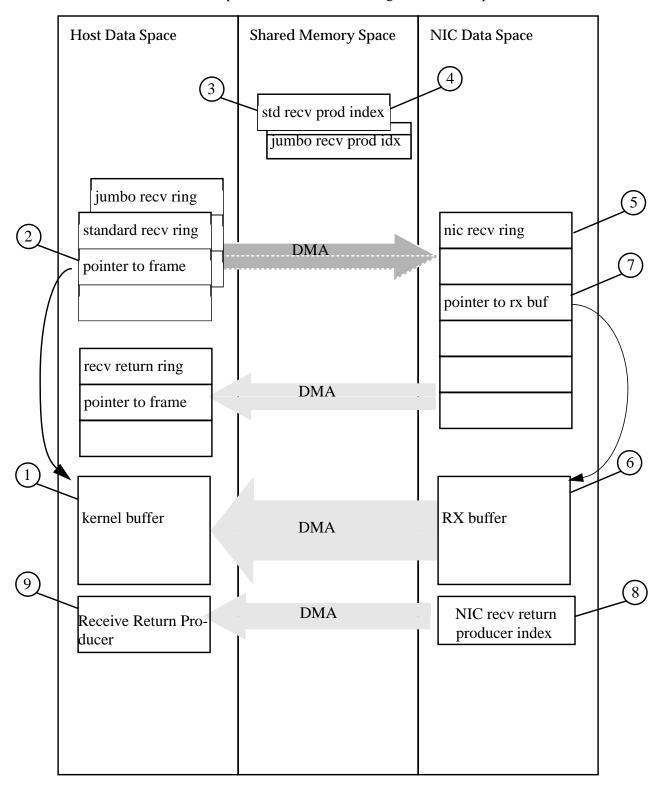

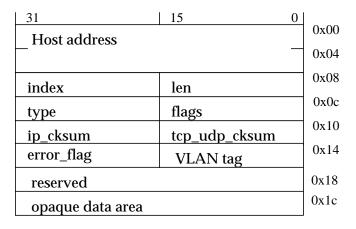

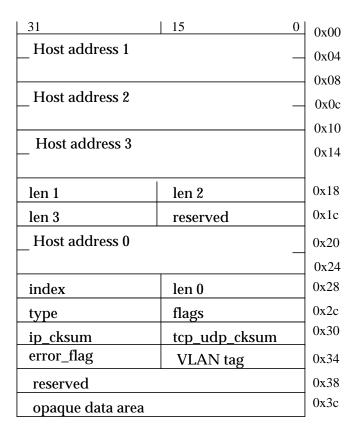

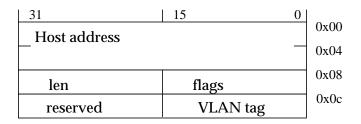

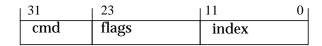

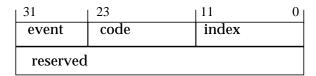

#### 2.1.1.4.10.4 Send Max Coalesced BDs