**Programmer's Manual**

AIC-6915 **Ethernet LAN Controller**

**Gadapte**°

Adaptec, Inc. 691 South Milpitas Boulevard Milpitas, CA 95035

© 1998, Adaptec, Inc. All rights reserved. Adaptec and the Adaptec logo are registered trademarks of Adaptec, Inc.

Printed in Singapore STOCK NO: 512130-00, Rev. A SG 9/98

••••• AIC-6915

Ethernet LAN Controller

**Programmer's Manual**

**Gadapte**c

#### Copyright

© 1998 Adaptec, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Adaptec, Inc., 691 South Milpitas Blvd., Milpitas, CA 95035.

#### Trademarks

Adaptec and the Adaptec logo are trademarks of Adaptec, Inc. which may be registered in some jurisdictions.

All other trademarks are owned by their respective owners.

#### Changes

The material in this document is for information only and is subject to change without notice. While reasonable efforts have been made in the preparation of this document to assure its accuracy, Adaptec, Inc. assumes no liability resulting from errors or omissions in this document, or from the use of the information contained herein.

Adaptec reserves the right to make changes in the product design without reservation and without notification to its users.

#### Adaptec Technical Support and Services

If you have questions about installing or using your Adaptec product, check this programmer's manual first you will find answers to most of your questions here. If you need further assistance, please contact us. We offer the following support and information services:

#### Electronic Support

Technical information, including product literature, answers to commonly asked questions, information on software upgrades and other topics is available electronically through the following:

- Adaptec World Wide Web (WWW) site at http://www.adaptec.com.

- File Transfer Protocol (FTP) server at ftp.adaptec.com.

- Adaptec USA Bulletin Board Service (BBS) at 408-945-7727; supports up to 28,800 bps (bits per second), 8 data bits, 1 stop bit, no parity. No product literature is available on the Adaptec BBS.

- Interactive Fax System at 408-957-7150; available 24 hours a day, 7 days a week.

#### Technical and Product Support

- For technical support and information about many of Adaptec's electronic support services, call 800-959-7274 or 408-945-2550, 24 hours a day, 7 days a week.

- To use the Adaptec Interactive Support System, call 800-959-7274 or 408-945-2550, 24 hours a day, 7 days a week. The system prompts you with questions regarding your problem and then provides step-by-step troubleshooting instructions.

- To speak with a product support representative, call 408-934-7274, M-F, 6:00 A.M. to 5:00 P.M., Pacific Time. After hours, on weekends, and on holidays, product support is also available for a fee at 800-416-8066.

#### Sales and Ordering Information

- For sales information, call 800-959-7274 or 408-945-2550, M-F, 6:00 A.M. to 5:00 P.M., Pacific Time.

- To order Adaptec software and SCSI cables, call 800-442-7274 or 408-957-7274, M-F, 6:00 A.M. to 5:00 P.M., Pacific Time.

- To request additional documentation for Adaptec products, call 800-934-2766 or 510-732-3829, M-F, 6:00 A.M. to 5:00 P.M., Pacific Time.

## •••• Contents

## **1** Introduction

Features 1-2 General 1-2 Ethernet 1-2 DMA 1-2 Internal Buffer Management 1-3 32/64-bit PCI 1-3 Block Diagram 1-5 Modules 1-6

## 2 Receive Architecture

Features 2-1 Host Data Structures 2-2 Producer and Consumer Indices 2-2 Receive DMA Descriptor Queues 2-2 Normal Mode 2-3 Polling Mode 2-3 32-bit Addressing Mode 2-4 64-bit Addressing Mode 2-4 Completion/Status Descriptor Queue 2-4 Accepting frames 2-5 Completion Descriptor 2-5

## **3** Transmit Architecture

Features 3-1

Transmit Data Structure 3-4

Transmit Register Set 3-5

Transmit DMA Buffer Descriptor Queues 3-5

Type 0, 32-bit Addressing Mode (Frame Descriptor) 3-5

Type 1 (Generic), 32-bit Addressing Mode (Buffer Descriptor) 3-8

Type 2 (Generic), 64-bit Addressing Mode (Buffer Descriptor) 3-8

Type 3, 32-bit Addressing Mode (Frame Descriptor) 3-9

Type 4, 32-bit Addressing Mode (Frame Descriptor) 3-9

Transmit Completion Queue Entry 3-10

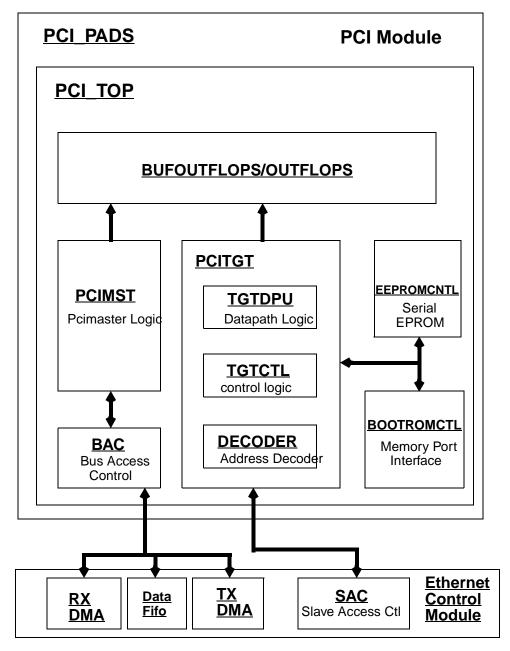

## 4 PCI Module Architecture

Features 4-1 PCI Block Diagram 4-3 PCI Master Module 4-4 64-bit PCI Bus Master 4-5 Arbitration 4-6 PCI Target Module 4-6 Power Management 4-8 CardBus 4-9 **Retry Function 4-9** Response to PCI Commands 4-9 Configuration Address Space 4-11 I/O Address Space (Direct Access) 4-11 I/O Address Space (Indirect Access) 4-11 Expansion ROM Address Space 4-12 Memory Address Space 4-12 Parity 4-12 SERR\_ 4-12 PERR\_ 4-13 The Command And Byte Enable Bits CBE[3:0]\_ 4-13 Illegal Behavior 4-14

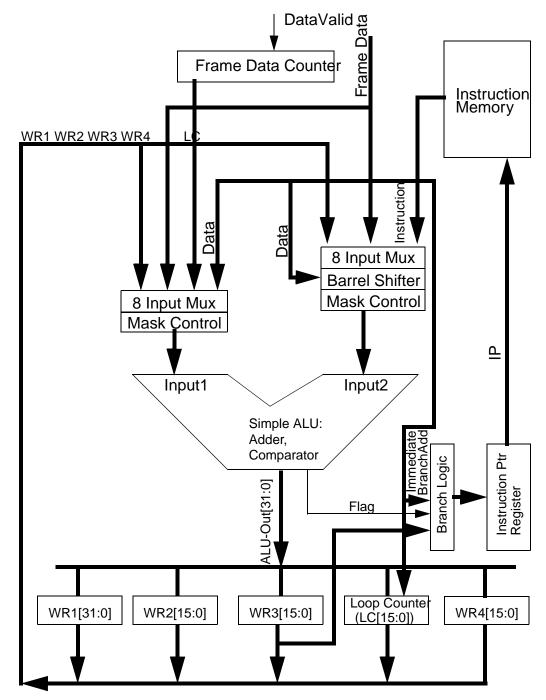

## 5 Frame Processor Architecture

Features 5-1 General Architecture & Operation 5-1 Wake-up Mode 5-2 Transmit Checksum Accelerator 5-2 GFP Address Space 5-3 Internal Registers 5-3 External Registers 5-4 Block Diagram 5-5 Instruction Formats 5-6

## 6 AIC-6915 Internal Registers Summary

PCI Configuration Header Registers Summary 6-1 AIC-6915 Functional Registers Summary 6-2 Additional PCI Registers Summary 6-4 Additional Ethernet Registers Summary 6-4

## 7 Register Descriptions

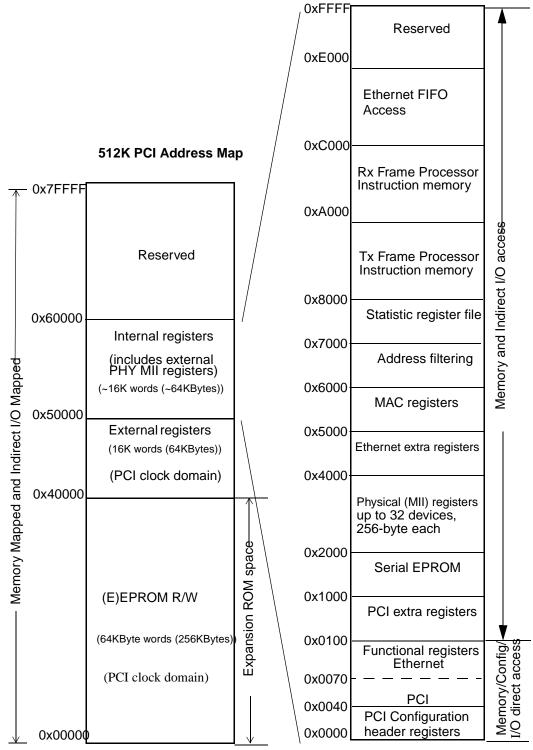

Overview 7-1 AIC-6915 Address Space 7-2 AIC-6915 PCI Address Map 7-2 Terminology 7-4 AIC-6915 Internal Registers 7-4 PCI Registers 7-5 PCI Configuration Header Registers 7-5 PCI Functional Registers Definition 7-17 Ethernet Registers 7-27 General Ethernet Functional Registers 7-27 Transmit Registers 7-37 Completion Queue Registers 7-43 Receive Registers 7-48 PCI Diagnostic Registers 7-59 PCI CardBus Registers 7-66 Additional Ethernet Registers 7-69 Ethernet Physical Device Registers 7-69 MAC Control Registers 7-71 Address Filtering Registers 7-82 MAC Statistic Registers 7-84

### 8 Sample Driver

Code Conventions 8-1 Producer-Consumer Model for the AIC-6915 8-2 Basic Register Initialization and Reset Sequence 8-3 Receive Process 8-7 Receive Completion Descriptor Queue 8-7 Receive Completion Descriptor Types 8-7 Receive Buffer Descriptor Queue 8-8 Receive Buffer Descriptor Types 8-8 Two Receive Queues 8-9 Receive Producer/Consumer Model 8-9 Receive Polling Model 8-9 **Receive Initialization 8-9** Receive Interrupt Handling 8-15 Transmit Process 8-16 Transmit Completion Descriptor Queue 8-16 Transmit Completion Descriptor Types 8-17 Transmit Buffer Descriptor Queue 8-17

Transmit Buffer Descriptor Types 8-18 Two Transmit Queues 8-20 Transmit Producer-Consumer Model 8-20 Transmit Initialization 8-21 Transmit Handling 8-25 Transmit Completion Interrupt Handling 8-27 AIC-6915 DDK Features 8-29 DDK Development Environment 8-30

# •••• Figures

#### Figure

- **1-1** AIC-6915 Block Diagram 1-5

- **2-1** The AIC-6915 Receive Data Structures 2-2

- **3-1** Transmit Host Communication Data Structure 3-4

- **4-1** PCI Block Diagram 4-3

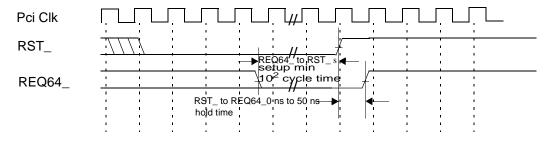

- **4-2** 64-bit PCI Reset Timing 4-5

- **5-1** Data Processing Unit 5-5

- 7-1 AIC-6915 PCI Address Map 7-3

# •••• Tables

### Table

| 2-1                      | Receive Buffer Descriptor (One-size, 32-bit Addressing) 2-4                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2-2                      | Receive Buffer Descriptor (One-size Buffer, 64-bit Addressing) 2-4                                                                    |

| 2-3                      | Short (Type 0) Completion Entry 2-6                                                                                                   |

| 2-4                      | Basic (Type 1) Completion Descriptor 2-6                                                                                              |

| 2-5                      | Checksum (Type 2) Completion Descriptor 2-6                                                                                           |

| 2-6                      | Full (Type 3) Completion Descriptor 2-6                                                                                               |

| 2-7                      | Receive Completion Descriptor (Word 0) 2-7                                                                                            |

| 2-8                      | Receive Completion Descriptor (Word 1) 2-8                                                                                            |

| 2-9                      | Receive Completion Descriptor (Word 2) 2-9                                                                                            |

| 2-10                     | Receive Completion Descriptor (Word 3) 2-9                                                                                            |

| 3-1                      | Type 0 Transmit DMA Descriptor (32-bit Addressing Only) 3-6                                                                           |

| 3-2                      | End Bit Functionality 3-7                                                                                                             |

| 3-3                      | Intr Bit Functionality 3-7                                                                                                            |

| 3-4                      | Type 1 Transmit DMA Descriptor (32-bit Addressing) 3-8                                                                                |

| 3-5                      | Type 2 Transmit DMA Descriptor (64-bit Addressing) 3-9                                                                                |

| 3-6                      | Type 4 Transmit DMA Descriptor (32-bit Addressing only) 3-10                                                                          |

| 3-7                      | Transmit Completion Queue Entry Type = DMA Complete Entry 3-10                                                                        |

| 3-8                      | Transmit Completion Queue Entry Type = Transmit Complete Entry 3-11                                                                   |

| 4-1                      | Power Management States 4-8                                                                                                           |

| 4-2                      | Target Response to PCI Commands 4-10                                                                                                  |

| 4-3                      | Address Phase CBE[3:0] Values 4-13                                                                                                    |

| 5-1<br>5-2<br>6-1<br>6-2 | Status/Control Register5-3Instruction Formats5-6PCI Configuration Header Registers Summary6-1AIC-6915 Functional Registers Summary6-2 |

| 6-3                      | AIC-6915 Additional PCI Registers Summary 6-4                                                                                         |

| 6-4                      | AIC-6915 Additional Ethernet Registers Summary 6-4                                                                                    |

| 7-1                      | Shade Legends 7-1                                                                                                                     |

| 7-2                      | AIC-6915 PCI Address Space 7-2                                                                                                        |

| 7-3                      | PCI Vendor ID Register 7-5                                                                                                            |

| 7-4                      | PCI Device ID Register 7-5                                                                                                            |

| 7-5                      | PCI Command Register 7-6                                                                                                              |

| 7-6                      | PCI Status Register 7-7                                                                                                               |

| 7-7                      | Device Revision ID Register 7-9                                                                                                       |

| 7-8                      | Program Interface Register 7-9                                                                                                        |

| 7-9                      | Subclass Register 7-9                                                                                                                 |

#### Table

- 7-10 BaseClass Register 7-10

- 7-11 Cache Line Size Register 7-10

- **7-12** Latency Timer Register 7-10

- **7-13** Header Type Register 7-11

- **7-14** BIST Register 7-11

- 7-15 Base Address 0 Register 7-11

- 7-16 High Base Address 0 Register 7-12

- 7-17 Base Address 1 Register 7-12

- **7-18** Configuration Card Information Structure Register 7-12

- 7-19 SubSystemVendor ID Register 7-13

- 7-20 SubSystem ID Register 7-13

- 7-21 Expansion ROM Control Register 7-14

- 7-22 Capabilities List Pointer Register 7-14

- 7-23 Interrupt Line Select Register 7-14

- 7-24 Interrupt Pin Select Register 7-15

- **7-25** Minimum Grant Register 7-15

- 7-26 Maximum Latency Register 7-16

- **7-27** PCIDeviceConfig Register 7-17

- 7-28 BacControl Register 7-20

- 7-29 PCI Monitor1 Register 7-21

- **7-30** PCI Monitor2 Register 7-22

- 7-31 Power Management Register 7-22

- 7-32 Power Management Control Status Register 7-23

- 7-33 PME Event Register 7-24

- 7-34 EEPROMControlStatus Register 7-24

- **7-35** EEPROM Memory Definition 7-25

- **7-36** PCIComplianceTesting Register 7-26

- **7-37** IndirectIoAddress Register 7-26

- **7-38** IndirectIoDataPort Register 7-26

- 7-39 GeneralEthernetCtrl Register 7-27

- **7-40** TimersControl Register 7-28

- 7-41 CurrentTime Register 7-30

- 7-42 InterruptStatus Register 7-31

- 7-43 ShadowInterruptStatus Register 7-34

- **7-44** InterruptEn Register 7-35

- **7-45** GPIO Register 7-36

- 7-46 TxDescQueueCtrl Register 7-37

- 7-47 HiPrTxDescQueueBaseAddress Register 7-39

- 7-48 LoPrTxDescQueueBaseAddress Register 7-39

- **7-49** TxDescQueueHighAddr Register 7-40

- **7-50** TxDescQueueProducerIndex Register 7-40

- 7-51 TxDescQueueConsumerIndex Register 7-41

- 7-52 TxDmaStatus1 Register 7-41

#### Table

7-53 TxDmaStatus2 Register 7-42 7-54 TransmitFrameControlStatus Register 7-42 7-55 CompQueueHighAddress Register 7-43 7-56 TxCompletionQueueCtrl Register 7-43 7-57 RxCompletionQueue1Ctrl Register 7-44 7-58 RxCompletionQueue2Ctrl Register 7-45 7-59 CompletionQueueConsumerIndex Register 7-46 7-60 CompletionQueueProducerIndex Register 7-47 7-61 RxHiPrCompletionPtrs Register 7-47 7-62 RxDmaCtrl Register 7-48 7-63 RxDescQueue1Ctrl Register 7-50 7-64 RxDescQueue2Ctrl Register 7-52 7-65 RxDescQueueHighAddress Register 7-52 7-66 RxDescQueue1LowAddress Register 7-52 7-67 RxDescQueue2LowAddress Register 7-53 7-68 RxDescQueue1Ptrs Register 7-53 7-69 RxDescQueue2Ptrs Register 7-54 7-70 RxDmaStatus Register 7-54 7-71 RxAddressFilteringCtrl Register 7-56 7-72 **RxFrameTestOut Register 7-58** 7-73 PCITargetStatus Register 7-59 7-74 PCIMasterStatus1 Register 7-60 7-75 PCIMasterStatus2 Register 7-61 7-76 PCI DMALowHostAddress Register 7-61 7-78 BacDmaDiagnostic1 Register 7-62 7-79 BacDmaDiagnostic2 Register 7-63 7-80 BACDMADiagnostic3 Register 7-64 7-81 MacAddr1 Register 7-65 7-82 MacAddr2 Register 7-65 7-83 FunctionEvent Register 7-66 7-84 FunctionEventMask Register 7-67 7-85 FunctionPresentState Register 7-67 7-86 ForceFunction Register 7-68 7-87 MIIRegistersAccessPort Register 7-69 7-88 TestMode Register 7-70 7-89 Rx General Frame Processor Control Register 7-70 7-90 TxFrameProcessorCtrl Register 7-70 7-91 MacConfig1 Register 7-71 7-92 MacConfig2 Register 7-73 7-93 BkToBkIPG Register 7-74 7-94 NonBkToBkIPG Register 7-75 7-95 ColRetry Register 7-75 7-96 MaxLength Register 7-76

#### Table

- 7-97 TxNibbleCnt Register 7-76

- 7-98 TxByteCnt Register 7-76

- 7-99 ReTxCnt Register 7-77

- 7-100 RandomNumGen Register 7-77

- 7-101 MskRandomNum Register 7-78

- 7-102 TotalTxCnt Register 7-78

- 7-103 RxByteCnt Register 7-79

- 7-104 TxPauseTimer Register 7-79

- 7-105 VLANType Register 7-79

- 7-106 MIIStatus Register 7-80

- 7-107 External PHY Address Examples 7-81

- 7-108 Address Filtering Memory 7-82

- 7-109 MAC Statistic Register 7-84

- 7-110 Transmit Frame Processor Register 7-87

- 7-111 Receive Frame Processor Register 7-87

- 7-112 FifoAccess Register 7-87

- **8-1** AIC-6915 DDK Features 8-29

# ....1

# Introduction

The Adaptec AIC-6915, PCI 10/100 Ethernet LAN Controller provides advanced Ethernet adapter features in a single chip optimized for high-performance and cost effective Ethernet NICs (Network Interface Cards).

The AIC-6915 integrates all the functions necessary for an Ethernet PCI adapter to directly connect (via a Medium Independent Interface (MII) -based PHY and line transformer) to Category 5 unshielded twisted pair (UTP) or shielded twisted pair (STP). The AIC-6915 integrates the following main blocks:

- Full-featured 2.1 PCI compliant, 32/64-bit master and 32-bit slave bus interface

- Powerful DMA engine

- 802.3 compliant 10/100 MAC (Medium Access Control) module

- MII Module

- 100BASE-TX compliant PCS (Physical Signaling) and PMA (Physical Medium Attachment) modules

The PCI Master uses enhanced data transfer commands to transfer data in zero wait state bursts. It supports 32- or 64-bit addressing for host buffers and transfers data at up to the maximum burst rate of 133/266 MBytes/sec with a maximum burst size of up to 2 KBytes. The AIC-6915 provides an External Interface port for access to a ROM/EEPROM (for add-in card local BIOS support, or boot ROM) and general purpose registers. A separate 4-wire Serial EEPROM port allows for downloading configuration information such as the Device ID, Vendor ID, Subsystem ID, Subsystem Device ID and Interrupt line. The AIC-6915 supports VLAN tagging, IEEE 802.1q and Flow Control as defined by the IEEE 802.3x specification. The AIC-6915 also provides an MII.

Throughout this document data sizes are defined as follows:

- Byte = 8-bits

- Halfword = 16-bits

- Word = 32-bits

- Doubleword = 64-bits

## **Features**

#### General

- Supports four general purpose I/Os that can be programmed separately as inputs, outputs, open-drain outputs or, interrupt inputs

- Interface to an external, 8-bit Boot ROM with a maximum size of 256-KByte

- Supports dynamic system bus (PCI) clock where the network can continue to operate at any clock frequency

- Internal loopback on all network ports for testing purposes

- IEEE 1149.1 compliant JTAG Boundary Scan Test Access port

#### Ethernet

- IEEE 802.3 compliant 10/100 MII that supports Category 3 UTP, Category 5 UTP, Type 1 STP and Fiber cables

- IEEE 802.3.x compliant Flow Control mechanism

- Supports Cisco proprietary VLAN ISL frame format

- Supports IEEE 802.1q (VLAN) frame format

- Supports PCI and OnNow power management

- Supports OnNow wakeup function

- Calculates TCP/IP checksum in transmit mode

- Checks TCP/IP checksum in receive mode

- Supports full-duplex operation on all ports (MII, 10/100 Twisted Pair)

- Provides a variety of address filtering modes:

- Promiscuous

- 16 full 48-bit addresses

- 512-bit hash table for multicast address filtering

- Time stamp information of every frame received

#### DMA

- Two transmit DMA queues to prioritize network traffic

- Enhanced interrupt mechanism increases performance and reduces CPU utilization:

- Transmit DMA Complete (Early Transmit)

- Early receive

- Transmit/Receive buffer under/over flow error handling. No software intervention required

- DMA channel arbitration eliminates overrun/underrun of First-In-First-Out (FIFO) buffers

- Supports 32- and 64-bit addressing of Host DMA buffers and DMA descriptor queues

- Big/Little endian support for data and descriptors

- Special output pin to indicate high-priority PCI request

#### Internal Buffer Management

- Large, 8 KByte DMA FIFO (default 4KByte for transmit, 4-KByte for receive)

- Programmable hardware-controlled transmit FIFO thresholds to prevent underrun of transmit FIFO and enhance overall system performance

- Unlimited (limited only by the FIFO size) Receive/Transmit frame queueing in the FIFO to handle long PCI bus latencies

- Hardware support for handling transmit collisions and FIFO underruns without software intervention

#### 32/64-bit PCI

- Compliant with PCI Local Bus Specification revision 2.1

- Compliant with Intel PCI Bus Power Management Interface Specification Rev 1.00 and Microsoft Device Class Power Management Reference Specification (OnNow)

- PC 97 ready. Implements all hardware features required by Microsoft's PC 98 design specification

- Supports 3.3V and 5.0V PCI signaling

- Direct pin out connection to PCI 32/64-bit bus interface

- PCI bus master with zero wait state 32/64-bit memory data transfers at 133/266 MBytes/sec, capable to support leading and trailing byte offset for DMA read and write (32-bit) for DMA write

- Supports 64-bit addressing in master and target modes

- PCI bus master/slave timing referenced to PCI signal **PCLK** (33.3 MHz max)

- PCI bus master programmable Latency Timer, Cache Size, And Interrupt Line Select registers

- Automatically senses if the adapter is plugged into a 32-bit or a 64-bit PCI slot.

- Supports cache line sizes of 16, 32, 64, 128, and 256 bytes

- Supports any combination of active byte enables for all PCI slave accesses

- Supports medium PCI target device-select response time

- Supports, as a bus master, enhanced PCI System memory data read and write commands:

- Memory Read

- Memory Read Line

- Memory Read Multiple

- Memory Write

- Memory Write And Invalidate

- Supports PCI bus address and data parity generation and checking

- Supports PCI **PERR** and **SERR** requirements

- Supports 8-bit, 256-KByte, external Memory port for interface with external Boot ROM or devices/registers

- Supports external Boot ROM access from memory or Expansion ROM address space

- Supports an external serial EEPROM for downloading chip configurations and MAC address

- INTA\_ interrupt generation from hardware, firmware, and software controlled sources

- Supports PCI slave accesses to PCI Configuration Header from configuration (read/write), I/O (indirect, read only) and memory address spaces (read only)

- Supports PCI slave access to AIC-6915 functional registers from configuration, I/O and memory address spaces

- Supports PCI slave access to AIC-6915 debug/buffer/FIFO Ethernet registers (implemented in the Ethernet control module) and external Memory port from indirect I/O and memory address spaces

- PCI target latency of 16 clocks maximum for the first target access cycle. The AIC-6915 initiates a cycle retry when an access requires more than 16 clocks to complete

## **Block Diagram**

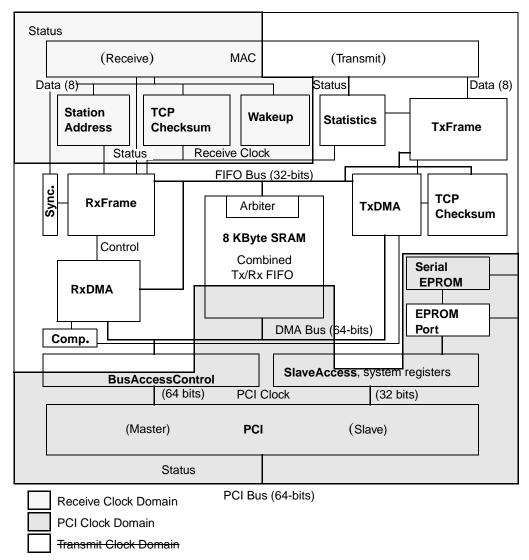

Figure 1-1 is a block diagram of the AIC-6915.

Figure 1-1. AIC-6915 Block Diagram

### **Modules**

The AIC-6915 contains the following major modules:

- PCI Controls access to the PCI bus and contains PCI-specific registers.

- **BusAccessControl** Arbitrates master accesses to the PCI bus from internal modules, and accesses the FIFO from the PCI side.

- SlaveAccess Drives the REGBUS to access the internal modules when AIC-6915 is accessed from the PCI bus.

- **General Registers** Contains general control and status registers, timers, and interrupt control. These registers are located throughout the AIC-6915.

- Memory Port Controls accesses to external EEPROM, FLASH, or other devices.

- Serial EPROM Controls interface to the serial EPROM.

- **TxDMA** Manages reading of the current frame being DMA-transferred for transmit, as well as transmit descriptor lists.

- **TxFrame** Manages the current frame being transmitted, reading the frame from the FIFO.

- **RxDMA** Manages writing of the current frame being DMA-transferred for receive, as well as the receive descriptor lists.

- **RxFrame** Manages the current frame being received, writing the frame to the FIFO.

- Station Address Compares the address of incoming frames with the stored addresses and/or hash table bits, and signals the **RxFrame** module if the addresses do not match.

- **TCP Checksum** Two TCP checksum modules are implemented, one for receive and one for transmit. The Receive TCP checksum module sums all relevant fields and compares them with the checksum value in the frame. The Transmit TCP checksum computes the checksum and places it in the FIFO.

- Wakeup Looks for frames matching a predefined pattern and asserts the PME\_ signal to wake up the system if one is found.

- **Completion** Records the current address for writing completion descriptors and stores the upper 32-bits of the descriptor's address.

- **Statistics** Counts various events from MAC, receive, and transmit.

- **Synchronizer** Synchronizes receive data and control to the transmit clock.

- MAC The MAC layer defined in the Ethernet specification manages many of the details in transmitting and receiving frames.

- **8 KByte SRAM** Dual-port SRAM used for storing transmit and receive data.

# ....2

## **Receive Architecture**

## Features

The host-related Receive Architecture features are

- Interrupts may be delayed so that only one interrupt is generated when a group of frames is received

- Choice of shared or separate completion lists for receive and transmit. An optional second completion list can be used for high-priority traffic

- Two programmable 256-entry or 2048-entry buffer descriptor lists, with optional smaller lists as defined by an "end" bit

- All receive buffers can be either the same size, or have individual sizes

- Early receive interrupt is generated when the DMA-transfer of a programmable number of bytes is complete. Status is not available until the end of the packet is DMA-transferred

- Optional 64-bit addressing for buffers and descriptor lists. All descriptor lists must be in the same 32-bit region in 64-bit space. Buffers can be located anywhere within the space, but an individual buffer must not cross a 4-GByte boundary

The internal Receive Architecture features are

- 4K Byte receive FIFO (The actual 8KByte on-chip SRAM is shared with Transmit)

- The FIFO does not have an arbitrary limit on the number of frames, but can continue receiving frames until it is full, regardless of the frame sizes

- Each frame requires only 8 bytes of overhead in the FIFO

- IEEE 802.3x based flow control

- Cisco's ISL frame support (Implemented in the MAC)

Additional value-added features

- Power management.

- Wakeup frames compliant to Microsoft's OnNow specification

- TCP and UDP checksum support

- VLAN support:

- Address filtering based on VLAN

- Ability to delete VLAN tag and number from frame returned to the host

- Optional second buffer list for allocating two different buffer sizes

## **Host Data Structures**

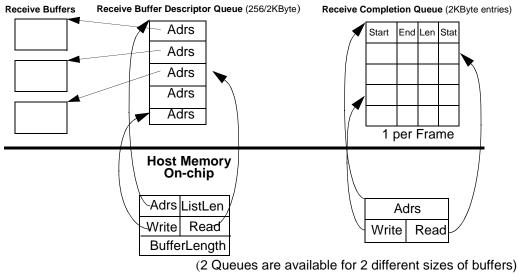

Figure 2-1 illustrates the AIC-6915 receive data structures.

(2 completion Queues allow for 2 priorities)

Figure 2-1. The AIC-6915 Receive Data Structures

#### **Producer and Consumer Indices**

The transmit, receive, and completion descriptors are stored in circular queues. With the descriptor queue, the host writes entries into the queue. The AIC-6915 reads from the descriptor queue and writes to the completion queue, which is in turn read by the host. The AIC-6915 maintains onchip Producer and Consumer indexes to each queue. The first element of any queue has an index of 0.

The Producer Index indicates the next entry of the queue to be written, while the Consumer Index indicates the next entry in the queue to be read.

If Producer and Consumer indices are equal, the queue is empty. If (Producer+1) mod QueueSize is equal to Consumer then the queue is full. The maximum number of entries placed in a queue at one time is the queue size minus one.

#### **Receive DMA Descriptor Queues**

The AIC-6915 contains two Producer/Consumer type DMA Receive Descriptor Queues that contain a maximum of either 256 or 2048 entries. A variable option permits the use of a smaller queue. Host Buffer addresses must be aligned to a word (4-byte) boundary. For best performance, addresses should also be aligned to cacheline boundary.

A programmable number of words can be skipped between buffer descriptors. This allows the driver to store data related to a buffer. When using 64-bit addressing, all descriptor and completion queues must be contained in the same 32-bit address space. Descriptor queues must be aligned to a 256-byte boundary.

When using 64-bit addressing, each receive buffer must fit within one 32-bit address space and must not cross a 4-GByte boundary.

There are two modes available for the host to inform the AIC-6915 that it has placed new buffer on the Buffer Descriptor Queue, Normal And Polling mode.

#### **Normal Mode**

In normal mode, after adding buffers to the buffer queue, the host writes to the onchip producer index. Some normal mode features are

- Fixed size 256- or 2048-entry queue.

- The AIC-6915 tracks the number of receive buffers available and can interrupt the host using the RxQ1LowBuffersInt and RxQ2LowBuffersInt interrupts if the number falls below a programmable threshold. The software driver may use this interrupt status bit to indicate the time it should update the producer index of the receive descriptor queue. This may save some 'expensive' slave cycles used for updating the producer index.

- If the AIC-6915 runs out of descriptors, it generates a RxQ1LowBuffers or RxQ2LowBuffers interrupt.

#### Polling Mode

In polling mode (RxPrefetchDescriptorMode = 1'b1), the host writes the descriptor to its local memory. When the AIC-6915 needs a descriptor, it always reads the next one regardless of the value in the producer pointer. If the valid bit is set, the AIC-6915 uses the descriptor. If not, it waits for the host to place more descriptors in the queue and to write any values to the producer. Some of the features of prefetch mode are

- Variable sized descriptor list with a maximum of 256 or 2048 entries. The host can set an "End" bit in the last descriptor in the list, causing the AIC-6915 to automatically wrap to the start of the list when fetching the next entry. The AIC-6915 automatically wraps after 256 or 2048 entries even if the "End" bit is not set.

- The AIC-6915 cannot track the number of receive buffers available and only interrupts the host requesting more buffers when it is completely out by generating a RxQ1LowBuffersInt or RxQ2LowBuffersInt interrupt. If the host does not respond to this interrupt fast enough, the onchip buffer may overflow and frames may be lost.

- Whenever the number of buffers is zero and the host has posted more buffers to the receive list, it must also write to the producer pointer to inform the AIC-6915 that more buffers have been added. The host can write any value. This causes the AIC-6915 to refetch the descriptor and look at the Valid bit again.

- The AIC-6915 does not reset the 'Valid' bit in the descriptor queue. It is the software driver's responsibility to manage the queue. The software driver can do this by maintaining at least one invalid descriptor right after the group of valid ones.

- In Polling mode, software driver must write to Producer Index (with RxDmaEn) to wake-up the AIC-6915 after reset.

#### 32-bit Addressing Mode

| Table 2-1. Receive E               | Buffer Descriptor ( | One-size  | 32-bit Addressing)  |

|------------------------------------|---------------------|-----------|---------------------|

| $Iable Z^{-1}$ . <b>R</b> eceive L |                     | UIE-SIZE, | JZ-DIL AUUIESSIIIU) |

| 31 | 24 | 23 | 16     | 15 | 8 | 7 | 0  |

|----|----|----|--------|----|---|---|----|

|    |    |    | Addres | S  |   |   | EV |

#### 64-bit Addressing Mode

|    | Table 2-2. F | Receive Buf | fer Descriptor | (One-size B | uffer, 64-bit A | Addressing) |          |   |

|----|--------------|-------------|----------------|-------------|-----------------|-------------|----------|---|

| 31 | 24           | 23          | 16             | 15          | 8               | 7           | 0        |   |

|    |              |             | LowAddr        | ress        |                 |             | E        | V |

|    |              |             | HighA          | ddress      |                 |             | <b>i</b> |   |

**Descriptor Fields:**

- Address The address of the buffer.

- LowAddress Least-significant 32-bits of address.

- HighAddress Most-significant 32-bits of address.

- **E** / **End** This bit is set to indicate the last descriptor. The next descriptor should be taken from the beginning of the list. This bit should only be set when the receive descriptors are in *prefetch* mode. It must be cleared otherwise.

- V / Valid In prefetch mode, this bit should be set if the descriptor is valid.

#### **Completion/Status Descriptor Queue**

There are two receive completion descriptor queues, one for high-priority frames and one for low-priority frames. The completion queues include the following features:

- Producer/Consumer type completion queue.

- Programmable queue contains a separate list for receive, or the queue can be shared between transmit and receive.

- A second list is available for high-priority frames. This cannot be shared with transmit.

- Software can zero the word being read and check for a nonzero value to confirm that new status was written. No valid descriptors will be all zero's.

- Two and four word completion descriptors include full status.

- Completion descriptor queues must be aligned on a 256-byte boundary.

- Completion descriptors may be 1, 2, or 4 words, depending on the amount of information required by the driver. Only 1 or 2 word completion descriptors may be used if the receive and transmit completion queues are shared.

#### Accepting frames

The AIC-6915 uses two criteria when deciding whether to accept a frame: Frame address and frame quality. When receiving a frame, the Station Address block evaluates a frame's address to determine if this station should receive the frame. Address filtering is accomplished by the time 64bytes are received. During this time, the General Frame Processor (GFP) also determines some characteristics about a frame, such as whether it is a TCP frame, whether it should override the descriptor or completion queues used, and the length of the header.

The MAC also determines some characteristics about the frame, such as its length, and whether any errors have occurred. This evaluation completes by the end of the frame, and the frame is assigned a "quality" based on this information. Normally, frames are only accepted if there are no CRC errors, no extra nibbles or bits, and the length is legal (less than or equal to a programmable value, normally 1536, and at least 64 bytes). However, the following control bits can allow additional frames to be accepted:

- RxDmaCrcErrorFrames if set, accept frames with a CRC errors

- RxDmaLongFrames if set, frames longer than a programmable value (normally 1536) are accepted. Otherwise, they are rejected

- RxDmaBadFrames if set, accept frames with a CRC error, nibble or code violation

- RxDmaShortFrames if set, the AIC-6915 accepts frames shorter than 64 bytes.

- RxReportBadFrames if set, the AIC-6915 reports the status for long and bad frames to the host, although it reuses the buffers for the next frame. Otherwise, the AIC-6915 does not report any status when it receives a bad frame, but only updates internal statistics.

Once 64 bytes of a frame have been received successfully, the AIC-6915 can start DMAtransferring the frame to the host. In some operating modes, such as header splitting, it must also wait for the frame processor to process the frame's IP header. If the frame is bad, the AIC-6915 does not inform the host of the buffers it used for that frame. Rather, it backs up its internal pointers and reuses those buffers on the next frame. The receive DMA engine transfers the receive data in amounts equal to the RxBurstSize field specified in RxDmaCtrl register. The DMA operation starts when a number of bytes equal to or greater than *RxBurstSize* is stored in the FIFO. When the number of bytes in the FIFO exceeds a programmable threshold (RxHighPriorityThreshold), the receive DMA engine is granted priority over the transmit engine for DMA services.

#### **Completion Descriptor**

A completion descriptor is normally DMA-transferred to the host when a good frame is received. The frame is DMA-transferred to the host and indicates the frame status, frame length, and the number of buffers used.

Various formats of completion descriptors are available, with RxCompletionQ1Type selecting the type to use the main completion queue, and RxCompletionQ2Type selecting the type to use in the high-priority queue.

If RxCompletionSize is set, the completion descriptor includes only the first word shown. If the bit is cleared, the first two words are shown. The RxCompletionType field controls whether the second word contains the TimeStamp, data from the Frame Processor, or some frame processor data and the VLAN ID.

A valid completion descriptor will never have a length field with a value of 0.

| 31  |         | 24 | 23       | 16 | 15 | 8   | 7    | 0 |

|-----|---------|----|----------|----|----|-----|------|---|

| 0 1 | Status1 |    | EndIndex |    |    | Len | igth |   |

Table 2-3. Short (Type 0) Completion Entry

Table 2-4. Basic (Type 1) Completion Descriptor

|   | 31      |         | 24       | 23 | 16 | 15     | 8    | 7 | 0 |

|---|---------|---------|----------|----|----|--------|------|---|---|

| 0 | 1       | Status1 | EndIndex |    |    | Length |      |   |   |

|   | Status2 |         |          |    |    | VLA    | N ID |   |   |

Table 2-5. Checksum (Type 2) Completion Descriptor

|   | 3       | 31 |         | 24 | 23       | 16            | 15      | 8     | 7 |  | 0 |

|---|---------|----|---------|----|----------|---------------|---------|-------|---|--|---|

| ( | )       | 1  | Status1 |    | EndIndex |               | Length  |       |   |  |   |

|   | Status2 |    |         |    |          | Partial TCP/U | DP Chee | cksum |   |  |   |

Table 2-6. Full (Type 3) Completion Descriptor

|   | 31        |         | 24       | 23          | 16 | 15     | 8       | 7          | 0 |

|---|-----------|---------|----------|-------------|----|--------|---------|------------|---|

| 0 | 1         | Status1 |          | EndIndex    |    | Length |         |            |   |

|   |           |         | Stat     | us2         |    | Status | 3 Start | Index      |   |

|   |           | Parti   | al TCP/U | DP Checksur | n  |        | VLAN ID | + Priority | Į |

|   | Timestamp |         |          |             |    |        |         |            |   |

| Bit(s)      | Description/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Status1 fie | əld                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 29          | <b>OK</b> - The frame is good. There were no CRC errors, dribble nibble, illegal lengths, or receive code violations. In ISL mode, the ISL and Ethernet checksums must both be valid. This does not include the TCP/UDP checksum.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 28          | <b>FifoFull</b> - If set, the frame is incomplete due to FIFO full - no other status bits, except OK, are valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 27          | <b>BufferQueue</b> - If set, the buffer queue 2 was used for the packet. If cleared, buffer queue 1 was used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| EndIndex    | field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 26:16       | EndIndex - Index of the last buffer used in the buffer queue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Length fie  | łd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 15:0        | Length - Total length of data transferred in bytes for good packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|             | This value is generally equal to the length of the packet (including destination and source addresses, type fields, etc.) minus 4 bytes, since the CRC isn't transferred by default. Setting RxDmaCrc to transfer the CRC can increase the length transferred here and reported by 4 bytes. Setting VlanMode=01, which causes the VLAN tag and ID to be stripped will reduce the length transferred and reported by 4 bytes. In header-splitting mode (RxDmaQueueMode=100), two buffer descriptors are transferred for TCP packets. A single receive completion queue is used for this mode. |  |  |  |  |

|             | The Length field of the first completion descriptor contains the length of the header in<br>bytes. The Length field of the second completion descriptor contains the total bytes<br>transferred, including the header, even through the header data is transferred to the<br>first queue, while the rest of the data is transferred to the second queue. This field may<br>not be valid for bad packets.                                                                                                                                                                                     |  |  |  |  |

| Bit(s)      | Description/Function                                                                                                                                     |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Status2 fi  | ield                                                                                                                                                     |  |  |  |  |

| 31          | Perfect - destination address matches one of the 16 predefined "perfect" addresses.                                                                      |  |  |  |  |

| 30          | Hash - hashed destination address matches a bit set in the hash table                                                                                    |  |  |  |  |

| 29          | CRC Error - TRUE if the packet had a CRC error. [PE-15 CRC error]                                                                                        |  |  |  |  |

| 28          | ISL CRC error - TBD                                                                                                                                      |  |  |  |  |

| 27          | <b>Dribble</b> - TRUE if the packet contains a noninteger number of bytes (i.e. extra bits or an extra nibble).                                          |  |  |  |  |

| 26          | <b>Receive Code Violation</b> - An illegal 4B/5B code was received in the packet.                                                                        |  |  |  |  |

| 25          | <b>Vlan Frame</b> - TRUE if the packet's tag matched the tag programmed in the MAC VlanType register.                                                    |  |  |  |  |

| 24          | <b>ChecksumOk</b> - If set, the packet is a TCP or UDP packet, the checksum was checked and is good.                                                     |  |  |  |  |

| 23          | <b>ChecksumBad</b> - If set, the packet is a TCP or UDP packet, the checksum was checked and is bad                                                      |  |  |  |  |

| 22          | PartialChecksumValid - If set, the partial checksum is valid                                                                                             |  |  |  |  |

| 21          | Fragmented - If set, the frame was fragmented                                                                                                            |  |  |  |  |

| 20          | TcpFrame - If set, the frame was a TCP frame                                                                                                             |  |  |  |  |

| 19          | UdpFrame - If set, the frame was a UDP frame                                                                                                             |  |  |  |  |

| 18:16       | FrameType - 0=Unknown, 1=IPv4, 2=IPv6, 3=IPX, 4=Icmp, 5=Unsupported                                                                                      |  |  |  |  |

| Status3 fie | İd                                                                                                                                                       |  |  |  |  |

| 15          | <b>IslFrame</b> - If set, the frame is an ISL frame, meaning that the first 5 bytes of its destination are 01:00:0C:00:00.                               |  |  |  |  |

| 14          | <b>PauseFrame</b> - If set, the frame is a Pause MAC Control frame as defined in the IEEE 802.3x specification.                                          |  |  |  |  |

| 13          | <b>ControlFrame</b> - If set, the frame is a MAC control frame other than a pause frame as defined in the IEEE 802.3 specification.                      |  |  |  |  |

| 12          | Header - If set, the completion descriptor is for a frame header.                                                                                        |  |  |  |  |

| 11          | <b>Trailer</b> - If set, the completion descriptor is for the remaining data in a frame whose header was transferred.                                    |  |  |  |  |

| StartIndex  | field                                                                                                                                                    |  |  |  |  |

| 10:0        | <b>StartIndex</b> - Index of the first buffer used in the buffer queue. This field is only important when both receive descriptor queues are being used. |  |  |  |  |

Table 2-8. Receive Completion Descriptor (Word 1)

| Bit(s)     | Description/Function                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Partial TC | P/UDP checksum field                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 31:16      | <b>Partial TCP/UDP Checksum</b> - When fragmented TCP/UDP frames are received, the partial TCP/UDP checksum of the first frame is calculated by the TCP/UDP header and data. The partial TCP/UDP checksum for subsequent frames is calculated by the TCP/UDP data only |  |  |  |  |  |  |

| VLan + Pr  | ority field                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 15:0       | <b>VLanID</b> + <b>Priority</b> - This field contains bytes 13 and 14 of the IEEE 802.1Q compliant frame.                                                                                                                                                              |  |  |  |  |  |  |

| Table 2-9. Receive Completion Descriptor (Wor | d 2) |

|-----------------------------------------------|------|

|-----------------------------------------------|------|

| Table 2-10. | <b>Receive Com</b> | oletion Descr | iptor | (Word 3) |  |

|-------------|--------------------|---------------|-------|----------|--|

|             |                    |               |       |          |  |

| Bit(s)                                                                            | Description/Function |  |  |  |  |

|-----------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Timestamp field                                                                   |                      |  |  |  |  |

| 31:0 <b>TimeStamp</b> - Time stamp value at the completion of the received frame. |                      |  |  |  |  |

The AIC-6915 provides address filters that have an effect on which receive frames are accepted and how they are processed. For more information on address filtering, refer to *Address Filtering Registers* on page 7-82.

# .....3

## **Transmit Architecture**

## Features

The main features of Transmit Architecture are

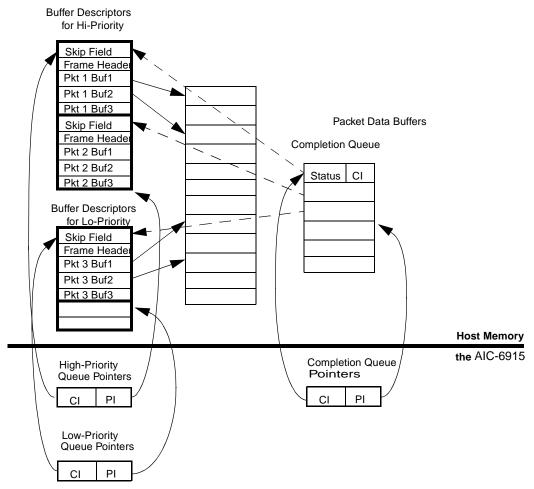

- Two Buffer Descriptor Queues in the Host Memory. One for high-priority packets and one for low-priority packets.

- Driver notifies the transmit block to start transmitting packets by writing the "Producer Index" of descriptor queues to its internal register. Producer and consumer indices are 11-bit pointers to an 8-byte descriptor in the queue. The transmit block does not poll host memory for new packets.

- Five descriptor types are supported. Descriptors can be categorized as "frame descriptors", which contain multiple buffer pointers in one descriptor format, and as "buffer descriptors", which contain one buffer pointer in one descriptor format. The driver must program the descriptor type at initialization time.

- Buffer descriptors (type 1 and 2) are multiples of either 8- or 16-bytes depending on whether the address is 32-bit or 64-bit. Frame descriptors (types 0, 3, and 4) can be either fixed size or variable size. In fixed-size mode, the frame size is defined in the "MinFrameDescSpacing" register, regardless of the number of buffer segments in the frame. In variable size mode, frame descriptors' size is the sum of total buffer segments. There is a "Skip field" defined in front of each descriptor to reserve space for the driver to store information. The "Skip field" size varies from 0 bytes to 128 bytes and is programmed by the driver at initialization time. The AIC-6915 does not read or write to the "Skip field".

- The descriptor queue size has a maximum size of 16KBytes. The actual length is variable with the end of queue defined by the "End" bit. The definition of the "End" bit is described in the Descriptor Queue section. Both high-priority and low-priority queues have base addresses aligned on a 256-byte boundary.

- The transmit DMA module returns buffers to the host by DMA-transferring the "Completion Descriptors" to the completion queue in the host memory. As soon as the DMA transfer completes, the packet is considered "done" and returned to the host.

- There are three kinds of interrupts generated by the transmit DMA engine. A "TxDmaDoneInt" is generated when the entire packet is DMA-transferred. A "TxFrameCompleteInterrupt" is generated when an entire packet is transmitted. There are two control bits, DisableTxDmaCompletion and DmaCompletionAfterTransmitComplete defined in the TxDescQueueCtrl and TxFrameControl registers to enable and disable each one of them. Setting these interrupt status bits is also conditioned with the INTR control bit in the transmit descriptor. A third interrupt, "TxQueueDoneInterrupt", is generated only when the descriptor queue is empty.

- Completion queue address control is centralized in the Completion Module for both receive and transmit. There are separate Completion Queues for receive and transmit. However, extra logic is built in the Completion Module to handle one Completion Queue for both receive and transmit. The Completion Queue size is 1024 entries. Each entry is either one word or two words, defined by driver at initialization time. The Completion Queue is aligned at 256-byte boundary. There is a Completion Queue Threshold defined in the register. When the free entries in the Completion Queue fall below this threshold, an interrupt is generated. The software driver should update the consumer index of the completion queue when it detects that the interrupt status bit is set.

- A Transmit DMA operation is triggered when there are frames in the descriptor queues and when the FIFO has room for "DMA Burst Size", a register defined by the software driver during initialization. The transmit DMA module dynamically adjusts DMA burst size so that DMA operations end on cache line boundaries. This can improve bus utilization on DMA data transfers.

- The "Frame Processor (FP) FIFO Engine" in the transmit DMA block works with FP to calculate TCP/UDP checksum for transmit packets. The checksum calculation starts when the DMA engine fetches the first burst of transmit data from Bus Access Control (BAC) and works in parallel during the DMA-transfer of the packet. Actual transmission to the MAC is not enabled until the checksum calculation is finished. For non-TCP/UDP packets, the driver can set the CALTCP bit to zero in the descriptor to disable checksum calculation and the transmission to the MAC can start without waiting for the end of packet. After the Transmit DMA fetches the first burst of transmit data, it signals the FP FIFO engine to begin reading packet data from the FIFO bus and passes that data to FP 16-bits at a time. The FP FIFO Engine decodes the write pointer of the FIFO to make sure that it does not read past the valid data of transfer. At the end of the packet, the DMA-transfer terminates and the FP FIFO Engine waits for the checksum and address of checksum returned by the FP. The FP FIFO engine writes the checksum to the FIFO, signals the transmit frame to start transmitting the packet, and signals the transmit DMA engine to start reading the next packet.

- Internal 4 KByte dedicated transmit FIFO. The FIFO is implemented by a dual-port SRAM. Once the port is written by the BAC, the other port is shared by the transmit and receive blocks.

- Packets in the internal FIFO are handled by link-lists. Transmit DMA block can DMA as many packets as possible into the FIFO as long as there is enough space.

- When the amount of packet data in the FIFO exceeds the "Transmit Threshold," or when the end of packet is already in the FIFO, the "Transmit Frame" state machine signals the MAC to start transmitting the packet. The transmit frame block handles reading packets from the FIFO, MAC interface and FIFO link list management. It also handles "retries" in case collision occurs and handles "aborts" when MAC signals errors.

- Built-in decode logic in the transmit frame block dynamically adjusts the priority of BAC arbitration. When the valid data in the FIFO drops below the "High-Priority Transmit FIFO Threshold" during transmission, the priority of transmit DMA is asserted and subsequent Transmit DMA operations are allotted a higher priority in BAC arbitration. Note that this only happens when the Transmit DMA engine and Transmit Frame are working on the same packet. This algorithm is designed to help prevent FIFO underrun.

- When the MAC is transmitting a packet, it may encounter network errors such as late collision, excessive deferral, excess collisions, or long packets. The MAC signals the transmit frame, which in turn aborts the current transmission. For normal collisions during the collision window, the MAC signals a "retry" to the Transmit Frame, which in turn retries transmission of these packets.

- Error handling routines are implemented in the Transmit Frame to retransmit a packet when transmit FIFO underrun error occurs. The Transmit Frame attempts to retransmit the packet if the start\_of\_packet data has not been overwritten by a subsequent DMA operation. If the Transmit Frame block cannot re-transmit the packet after three tries, the packet is aborted. The start\_of\_packet "Producer Index" of the error packet is DMA-transferred back to the host through the "Completion Queue".

- As the MAC completes each packet transmission, it advertises the transmit status of this packet. The Statistic Block collects both transmit and receive status and stores them in a local register file. When the mode of "Transmit Complete Interrupt" is on, the transmit status is DMA-transferred to the host.

- 64-bit addressing support on all data buffers. The "Descriptor Queue" and the "Completion Queue" are also 64-bit addressing, but they share the same high-order 32-bit addresses (same 4-GByte page).

- Power Management Mode defined by PCI Bus Power Management Interface Specification. When the transmit block is put to the "Sleep" mode, all the state machines are reset to "Idle" and then the clock is removed.

## **Transmit Data Structure**

#### Figure 3-1 illustrates the Transmit Data Structure

Figure 3-1. Transmit Host Communication Data Structure

#### **Transmit Register Set**

The following is a list of transmit parameters programmed by the driver during initialization.

- Transmit descriptor queue size and base address.

- Completion queue size and base address.

- Descriptor type, minimum spacing, and skip field size.

- FIFO size (4KBytes).

- PCI cache line size.

- DMA burst size.

- Transmit start threshold.

- DMA priority threshold.

The following is a list of transmit registers used during a host to AIC-6915 communication.

- High-priority queue consumer index. (Written by the AIC-6915, read by driver).

- High-priority queue producer index. (Written by the driver, read by the AIC-6915).

- Low-priority queue consumer index. (Written by the AIC-6915, read by the driver).

- Low-priority queue producer index. (Written by the driver, read by the AIC-6915).

- Completion queue consumer index. (Written by the driver, read by the AIC-6915).

- Completion queue producer index. (Written by the AIC-6915, read by the driver).

#### **Transmit DMA Buffer Descriptor Queues**

There are two Buffer Descriptor Queues for transmission. One for high-priority traffic and one for low-priority traffic. Each Descriptor Queue size has a maximum size of 16-KBytes. The actual length is variable with the end-of-queue defined by the "END" bit. The definition of the "END" bit is described in the following sections. Both high-priority and low-priority queues have base addresses aligned on a 256-byte boundary.

Five descriptor types are supported. The driver must program the descriptor type during initialization. Descriptors are in multiples of 8-bytes. The Descriptor Queue is aligned on a 256-byte boundary. There is a "Skip field" defined in front of each packet to reserve space for the driver to store information. The "Skip field" size varies from 0 bytes to 128 bytes and is programmed by the driver during initialization. The AIC-6915 does not read or write to the "Skip field".

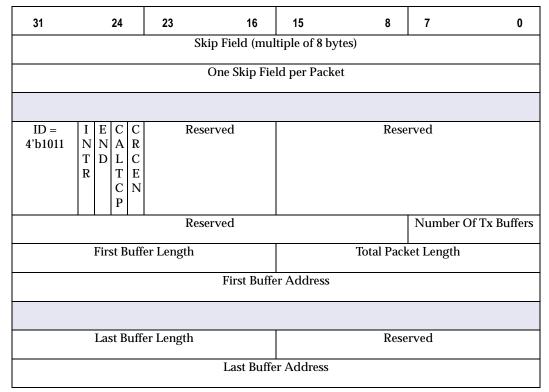

#### Type 0, 32-bit Addressing Mode (Frame Descriptor)

Type 0 enables the driver to execute a simple and fast copy of a TCB data structure (given by the upper layer software as a frame descriptor) to the Descriptor Queue area.

| 31                               | 24                                                                                                                       | 32   | 16                 | 15                  | 8                    | 7 | 0 |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|--------------------|---------------------|----------------------|---|---|--|

| Skip Field (multiple of 8 bytes) |                                                                                                                          |      |                    |                     |                      |   |   |  |

| One Skip Field per Packet        |                                                                                                                          |      |                    |                     |                      |   |   |  |

|                                  |                                                                                                                          |      |                    |                     |                      |   |   |  |

| ID =<br>4'b1011                  | $\begin{array}{c cccc} I & E & C & C \\ N & N & A & R \\ T & D & L & C \\ R & & T & E \\ & & C & N \\ & & P \end{array}$ | Rese | rved               | Reserved            |                      |   |   |  |

|                                  | Reserved                                                                                                                 |      |                    |                     | Number Of Tx Buffers |   |   |  |

|                                  | First Buffer Address                                                                                                     |      |                    |                     |                      |   |   |  |

|                                  | Total Packet Length                                                                                                      |      |                    | First Buffer Length |                      |   |   |  |

|                                  |                                                                                                                          |      |                    |                     |                      |   |   |  |

| Last Buffer Address              |                                                                                                                          |      |                    |                     |                      |   |   |  |

| Reserved                         |                                                                                                                          |      | Last Buffer Length |                     |                      |   |   |  |

Table 3-1. Type 0 Transmit DMA Descriptor (32-bit Addressing Only)

- ID: 4 bits. This field is used by the software/debugger to identify the start of a descriptor. If a transmit DMA operation does not see a matched ID in this field, it aborts the DMA operation and sets an interrupt status bit.

- Number of Fragments: 8 bits. Defines the number of follow-on segments. This field must be "nonzero".

- **END**: Indicates that the current descriptor is at the end of the queue. The 'End" has different functionality for the following conditions:

| Desc. Type    | Conditions                                                         | Functionality                                                                                                                                                                                                                           |

|---------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame (0,3,4) | MinFrameDescSpacing<br>!=0                                         | The number of bytes between two<br>consecutive frame descriptions is fixed. The<br>queue wraps around at the end of the fixed<br>address. No wrap in the middle of a frame<br>descriptor.                                               |

| Frame (0,3,4) | MinFrameDescSpacing<br>=0                                          | The number of bytes between two<br>consecutive frame descriptions is variable.<br>For type 0/4, the queue wraps after reading<br>16 bytes of descriptor data. For type 1/3, the<br>queue wraps after reading 8 bytes of<br>descriptors. |

| Buffer (1,2)  | MinFrameDescSpacing<br>must be 0.                                  | For type 1, the queue wraps after reading 8 bytes of descriptors data.                                                                                                                                                                  |

|               | 'End' bit is valid only<br>for the first descriptor<br>of a frame. | For type 2, the queue wraps after reading 16 bytes of descriptor data.                                                                                                                                                                  |

Table 3-2. End Bit Functionality

■ INTR: Causes setting of the interrupt status bits (TxDmaDoneInt and/or TxFrameCompleteInt) after complete transmission of the entire packet. The appropriate interrupt status bit is set based on two control bits that the software programs at the initialization phase. Given 'INTR' is set the following table specifies the functionality:

| DisableTxDmaCo<br>mpletion | TxCompletionDescAft<br>erTxComplete | Functionality                                                                                                                             |

|----------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0                          | 0                                   | TxDmaDoneInt is set after complete DMA the whole packet.                                                                                  |

| 0                          | 1                                   | TxDmaDoneInt is set after complete DMA the<br>whole packet, and TxFrameCompleteInt is set<br>after complete transmitting the whole frame. |

| 1                          | 0                                   | None of the two interrupt status bits is set.                                                                                             |

| 1                          | 1                                   | TxFrameCompleteInt is set after complete<br>transmitting the whole frame. 'INTR'                                                          |

Table 3-3. Intr Bit Functionality

**Note:** The software driver may choose to work with another interrupt status bit, TxQueueDoneInt, that is not controlled by '**INTR**'. The AIC-6915 sets this bit after the DMA-transfer of a completion descriptor for the last frame queued for transmit. The last frame is detected when the consumer and producer indices of the queue are equal.

- CRCEN: Setting this bit enables the MAC to calculate and append the CRC value for the current packet. Clearing the bit disables the MACs ability to calculate the CRC value.

- **CALTCP**: Setting this bit enables the F P to calculate TCP/UDP checksum for this packet. Clearing the bit disables the FPs ability to calculate the checksum.

• **Total Packet Length**: This 16-bit field defines the total packet length. If this field is zero, it is ignored and the total packet length is equal to the sum of all the buffers. If this field is nonzero, it is defined as the total packet length.

**Note:** In Novell TCB/ECB blocks, the total packet length is not always equal to the sum of the buffer length. Transmit DMA pads extra bytes to the FIFO if the total packet length is greater than the sum of the buffer length.

- **Buffer Length**: The length of the host buffer in bytes.

- **Buffer Address**: The byte address of the host buffer.

#### Type 1 (Generic), 32-bit Addressing Mode (Buffer Descriptor)

In Type 1 and 2 buffer descriptors, the INTR, END, CALTCP, CRCEN, and Number of Tx Buffers fields are valid for the first buffer of a frame only. The ID, Length, and Address are valid for all buffers of the frame. The software driver must use the 'End' bit only in the first buffer descriptor of a frame. The queue wraps around after reading 8 bytes of descriptor data for Type 1 and 16 bytes of data for Type 2.

| 31      |   |   | 24 |   | 23       | 16            | 15            | 8      | 7       | 0 |

|---------|---|---|----|---|----------|---------------|---------------|--------|---------|---|

|         |   |   |    |   | Sl       | kip Field (mu | ltiple of 8 l | oytes) |         |   |

|         |   |   |    |   |          | One Skip Fie  | eld per Buf   | ffer   |         |   |

|         |   |   |    |   |          |               |               |        |         |   |

| ID =    | Ι | Ε | С  | С | Number C | Of Tx Buffers |               | Length | (bytes) |   |

| 4'b1011 | Ν | Ν | Α  | R | (valid o | nly if first  |               |        |         |   |

|         | Т | D | L  | С | frag     | ment)         |               |        |         |   |

|         | R |   | Т  | Е |          |               |               |        |         |   |

|         |   |   | С  | Ν |          |               |               |        |         |   |

|         |   |   | Р  |   |          |               |               |        |         |   |

|         |   | 1 |    | 1 |          | Ade           | dress         |        |         |   |

Table 3-4. Type 1 Transmit DMA Descriptor (32-bit Addressing)

#### Type 2 (Generic), 64-bit Addressing Mode (Buffer Descriptor)

In Type 1 and 2 buffer descriptors, the INTR, END, CALTCP, CRCEN, and Number of Tx Buffers fields are valid for the first buffer of a frame only. The ID, Length, and Address are valid for all buffers of the frame. The software driver must use the 'END' bit only in the first buffer descriptor of a frame. The queue wraps around after reading 8 bytes of descriptor data for Type 1 and 16 bytes of data for Type 2.

| 31              |    | 24                         | 23       | 16                                     | 15            | 8      | 7       | 0 |

|-----------------|----|----------------------------|----------|----------------------------------------|---------------|--------|---------|---|

|                 |    |                            | Sk       | ip Field (mul                          | tiple of 8 by | vtes)  |         |   |

|                 |    |                            |          | One Skip Fie                           | ld per Buffe  | er     |         |   |

|                 |    |                            |          |                                        |               |        |         |   |

| ID =<br>4'b1011 | Ν  | C<br>A<br>L<br>T<br>C<br>P | (valid o | of Tx Buffers<br>nly if first<br>ment) |               | Length | (bytes) |   |

|                 | 11 |                            |          | Rese                                   | rved          |        |         |   |

|                 |    |                            |          | Low A                                  | ddress        |        |         |   |

|                 |    |                            |          | High A                                 | Address       |        |         |   |

Table 3-5. Type 2 Transmit DMA Descriptor (64-bit Addressing)

#### Type 3, 32-bit Addressing Mode (Frame Descriptor)

This mode is currently not supported in the AIC-6915.

#### Type 4, 32-bit Addressing Mode (Frame Descriptor)

Type 4 enables the driver to execute a simple and fast copy of DOS and OS2 data structure (given by the upper layer software as a frame descriptor) to the descriptor queue area. The only difference is the location of 'Buffer Length' and 'Buffer Address'.

Table 3-6. Type 4 Transmit DMA Descriptor (32-bit Addressing only)

#### **Transmit Completion Queue Entry**

Transmit Completion Queue entries consist of two types: DMA Complete Entry and Transmit Complete Entry, differentiated by the MSB of the entry. Three bits are defined in the "Type" field because the AIC-6915 always returns a nonzero value in the DMA Complete Entry. Each Transmit Completion Queue Entry can be programmed as either 4 bytes or 8 bytes.

Table 3-7. Transmit Completion Queue Entry Type = DMA Complete Entry