**T2 Software Functional Specification**

©2000 3Com Corporation

| 1. | CHA   | NGE HISTORY                                 | 4    |

|----|-------|---------------------------------------------|------|

| 2. | INTR  | RODUCTION                                   | 7    |

| HA | RDWA  | ARE OVERVIEW                                | 8    |

| 2  | 1 (   | 03C Processor                               | 0    |

| -  |       | 95C PROCESSOR<br>PCI Interface              |      |

| -  |       | Memory Controller                           |      |

| -  |       | MEDIA ACCESS CONTROLLER                     |      |

| -  |       | Sootstrap ROM                               |      |

| 4. |       | CTIONAL DESCRIPTION OF FEATURES             |      |

|    |       |                                             |      |

| 4  |       | MANAGEMENT FEATURES                         |      |

|    | 4.1.1 | Statistics                                  |      |

|    | 4.1.2 | Power Management                            |      |

|    | 4.1.3 | Enhanced Remote Wakeup                      |      |

|    | 4.1.4 | Personal Firewall                           |      |

|    | 4.1.5 | I <sup>2</sup> C Serial Port Driver         |      |

|    | 4.1.6 | Heartbeat                                   |      |

|    | 4.1.7 | Off-line Diagnostics                        |      |

| 4  |       | Performance Enhancements                    |      |

|    | 4.2.1 | TCP/IP Checksum Generation and Verification |      |

|    | 4.2.2 | TCP Segmentation                            |      |

|    | 4.2.3 | Dynamic Access 2.0                          |      |

|    | 4.2.4 | IEEE 802.1p/Q Class of Service Priorities   |      |

|    | 4.2.5 | IPSec                                       | . 21 |

| 5. | THE   | ORY OF OPERATION                            | 27   |

| 5  | .1 I  | HOST ADAPTER INTERFACE                      | 27   |

|    | 5.1.1 | Packet Type                                 | 27   |

|    | 5.1.2 | Data Format and Alignment Convention        | 27   |

| 5  | .2 I  | HOST ADAPTER INTERFACE RING BUFFER          | 28   |

| 5  | .3 I  | PACKET FLOW CONVENTION                      | 31   |

|    | 5.3.1 | Host-to-adapter Packet Flow                 | . 31 |

|    | 5.3.2 | De-allocating Transmit Frames               | . 40 |

|    | 5.3.3 | Adapter-to-Host (Rx) Interface              | . 41 |

|    | 5.3.4 | Receive Priority Processing                 | . 45 |

|    | 5.3.5 | Receive Data Flow                           | . 46 |

| 5  | .4 I  | HOST-TO-ADAPTER COMMAND DESCRIPTIONS        | 46   |

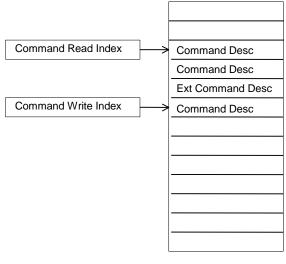

|    | 5.4.1 | Command Ring                                | . 47 |

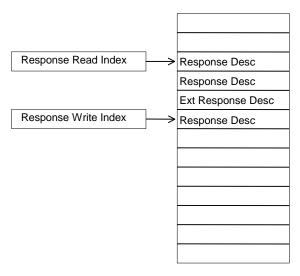

|    | 5.4.2 | Response Ring                               | . 49 |

|    | Respo | mse Descriptor                              |      |

|    | 5.4.3 | Arm to Host Interrupts                      |      |

| 5  | .5 /  | Adapter Boot                                | 53   |

|    | 5.5.1 | Overview                                    |      |

|    | 5.5.2 | ROM Boot Loader                             |      |

|    | 5.5.3 | Boot Command Language for Boot Failure      |      |

|    | 5.5.4 | NVDevice Boot                               | . 59 |

| 5  |       | Adapter Sleep                               |      |

|    | 5.6.1 | Putting Typhoon to sleep                    | . 68 |

|    | 5.6.2 | Wakeup Events                               | . 68 |

©2000 3Com Corporation

|    | 5.6.3 Sleep Events                           | 69    |

|----|----------------------------------------------|-------|

|    | 5.7 Adapter Reset                            | 71    |

|    | 5.8 ANTI-STARVATION DE-QUEUE ALGORITHM:      |       |

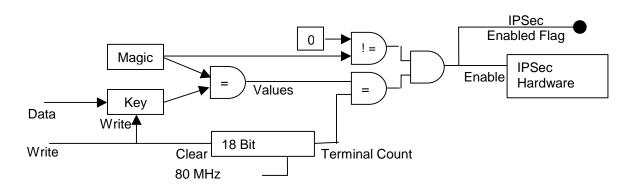

|    | 5.9 ENCRYPTION ENABLE LOGIC                  | 74    |

| 6. | COMMAND DESCRIPTIONS                         | 76    |

|    | 6.1 HOST-TO-ADAPTER COMMAND DESCRIPTIONS     |       |

|    | 6.2 UNSOLICITED RESPONSES                    | 114   |

| 7. | MANUFACTURING SUPPORT                        | 115   |

|    | 7.1 NVDEVICE CONFIGURATION                   |       |

|    | 7.1.1 Memory Layout Example                  |       |

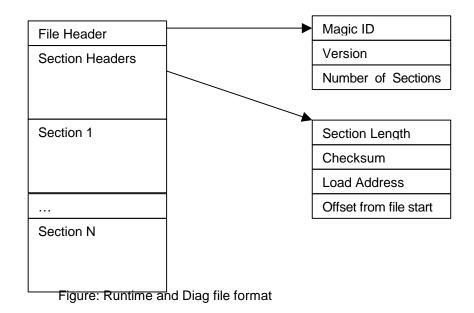

|    | 7.1.2 Magic Id                               | 117   |

|    | 7.1.3 Section Headers                        | 117   |

|    | 7.1.4 Static Section                         | 117   |

|    | 7.1.5 VAR Section                            |       |

|    | 7.1.6 Boot Image Section                     |       |

|    | 7.1.7 Sleep Image Section                    |       |

|    | 7.2 DIAGNOSTICS                              | 125   |

| AI | PPENDIX A –ENUMERATED VALUES                 | 126   |

| 1. | HOST TO ADAPTER COMMANDS                     | 12(   |

| 1. | HOST TO ADAFTER COMMANDS                     |       |

| 2. | TYPHOON STATUS                               | 128   |

| 3. | HOST STATUS                                  | 128   |

| AI | PPENDIX B - PACKET FILTERING                 | 130   |

| 1. | FILTER FEATURES                              | 120   |

|    |                                              |       |

|    | 1.1 FILTERING MANAGEMENT REQUESTS TO TYPHOON |       |

| AI | PPENDIX C - OEM FUNCTION EXTENSION API       |       |

| 1. | OVERVIEW                                     | 132   |

| •  | 00415                                        | 122   |

| 2. | GOALS                                        | 132   |

| 3. | SDK                                          |       |

| AI | PPENDIX D: SLEEP EVENT IMPLEMENTATION        |       |

| 1  |                                              | 100   |

| 1. | INTRODUCTION                                 | 133   |

| 2. | NOVELL WATCHDOG REPLIES                      |       |

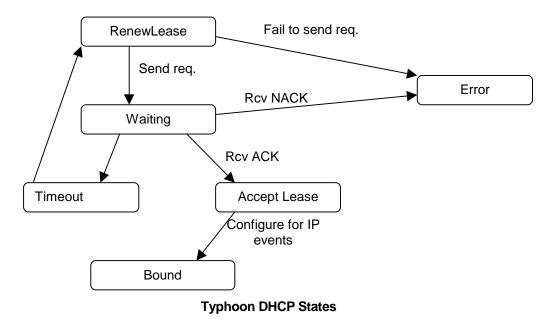

| 3. | DHCP LEASE RENEWAL                           |       |

| AI | PPENDIX E: SOS PINS ON TYPHOON               |       |

| 4  | INDEX                                        | 1 4 1 |

| 4. | INDEX                                        |       |

# 1. Introduction

This document describes the software for Typhoon 2, or **T2**, 3Com's 2nd generation "smart" NIC. It's a 100 MBPS Ethernet adapter. T2 includes all of the Typhoon logic, which borrows some logic from previous 3Com Ethernet Adapter ASICs (Cyclone/Hurricane), such as parts of the PCI interface and the MAC logic. Previous functions that were external to the Typhoon ASIC are integrated into T2, including the 128k external SRAM, and the IPsec encryption engine. Locgic external to T2 includes the serial flash ROM, magnetics, and an optional external SRAM or coprocessor.

The on-board processing engine performs intelligent packet processing and scheduling while reducing the load on the host processor.

Typhoon supports several new or enhanced features that improve network management or lower CPU utilization:

#### Management Features

- MAC Statistics

- Power Management Support for the four PCI power states.

- Enhanced Remote Wakeup support with the added capability to generate keep-alive or heartbeat packets.

- Personal Firewall The ability to throttle or restrict bandwidth on some traffic transmitted or received by the NIC.

- I<sup>2</sup>C Bus Interface This is a supporting feature for off-line diagnostics.

- Off-line diagnostics The ability to gather and report information about the health and state of the host even when the host is not operational.

#### Performance Enhancements

- TCP/IP checksum generation and verification.

- TCP segmentation.

- Acceleration of Dynamic Access 2.0 features.

- Improved Host Interface.

- IPSec

# 2. Functional Description of Features

# 2.1 Management Features

# 2.1.1 Statistics

The processor on the adapter will keep statistics in memory. The Host Driver may view these statistics by:

- Requesting Statistics transfer to host memory.

- Timed update of statistic transfers to host memory.

The sources of the statistics are a combination of MAC registers, status descriptors and software derived statistics from Filter results.

The adapter will keep the following statistics: (dRMON Statistics are not addressed in this section. See dRMON for details.)

# **Transmit Statistics**

| TxPackets             | The number of packets transmitted successfully without critical error.   |

|-----------------------|--------------------------------------------------------------------------|

| TxBytes               | The number of bytes transmitted successfully without critical error (    |

|                       | does not include framing ).                                              |

| TxDeferred            | The number of times that packet transmission had to defer to network     |

|                       | traffic before transmitting successfully.                                |

| TxLateCollisions      | The number of times a transmitted packet has collided after the first 64 |

|                       | bytes were transmitted.                                                  |

| TxCollisions          | The number of packets transmitted successfully after a single collision. |

| TxMultipleCollisions  | The number of packets transmitted successfully after more than one       |

|                       | collision.                                                               |

| TxCarrierLost         | The number of packets transmitted that experienced a loss of carrier.    |

| TxExcessiveCollisions | The number of packets tossed due to more than 16 collisions.             |

| TxFifoUnderruns       | The number of time the transmit FIFO has gone empty while                |

|                       | transmitting before the packet was completed.                            |

| TxBroadcast           | The number of packets transmitted with a destination address of all      |

|                       | one's.                                                                   |

| TxMulticast           | The number of packets transmitted with a destination address having      |

|                       | the multicast bit set.                                                   |

| TxOverflows           | The number of packets tossed by the transmitter due to lack of           |

|                       | Queue or Buffer space.                                                   |

| TxFiltered            | The number of packets tossed by the transmitter due to a Filter          |

|                       | directive.                                                               |

| TxBroadcastBytes      | The number of octets transmitted in packets with a destination           |

|                       | address of all one's.                                                    |

| TxMulticastBytes      | The number of octets transmitted in packets with a destination           |

| · <u> </u>            | address having the multicast bit set.                                    |

| *TxJabbers            | The number of packets transmitted that were aborted because they         |

|                       | were continuously transmitting.                                          |

| Not Supported         |                                                                          |

| TxSqeErrors           | Not Applicable.                                                          |

| TxReclaimErrors       | Not Applicable.                                                          |

# **Receive Statistics**

| RxPacketsGood    | The number of packets received without error.                          |

|------------------|------------------------------------------------------------------------|

| *RxPacketsTotal  | The number of packets received including error packets.                |

|                  |                                                                        |

| RxBytesGood      | The number of bytes received without error (excluding framing).        |

| *RxBytesTotal    | The number of bytes received including error packets (excluding        |

|                  | framing ).                                                             |

| RxFifoOverruns   | The number of packets lost because the receive FIFO was full.          |

| *RxFilteredByMac | The number of packets that are filter at the MAC when filters are set. |

| BadSSD           | The total number of packets received with bad start-of-stream          |

|                  | delimiter. This is only valid for 100BaseTx and 100BaseFx.             |

| *RxRunts         | The number of packets received that were less than 64 bytes.           |

| RxCrcErrors      | The number of packets received that contained a bad CRC.               |

| RxOversize       | The number of packets received that were greater than MTU.             |

| RxBroadcast      | The number of packets received with a destination address of all       |

|                  | one's.                                                                 |

| RxMulticast      | The number of packets received with a destination address having       |

|                  | the multicast bit set.                                                 |

©2000 3Com Corporation

| RxOverflow        | The number of packets received that were lost due to no buffer space available. |

|-------------------|---------------------------------------------------------------------------------|

| RxFiltered        | The number of packets tossed by the receiver due to a Filter directive.         |

| RxAlignmentErrors | The number of packets received that were not octet aligned.                     |

| RxDribbleBits     | The number of packets received that contained dribble bits.                     |

|                   | Software selectable as forward or reject on error.                              |

#### **Statistic Sources**

| The following statistics are read from MAC registers:<br>TxPackets, TxBytes, TxDeferred, TxLateCollisions, TxCollisions, TxMultipleCollisions,<br>TxCarrierLost, RxPacketsGood, *RxPacketsTotal, RxBytesGood, *RxBytesTotal,<br>RxFifoOverruns, RxFilteredByMac, BadSSD |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The following statistics are created from MAC Receive descriptors:<br>*RxRunts, RxCrcErrors, RxOversize, RxDribbleBits, RxAlignmentErrors                                                                                                                               |

| The following statistics are created from software interrupts from the MAC:<br>TxExcessiveCollisions, TxFifoUnderruns, *TxJabbers                                                                                                                                       |

| The following statistics are created from software events or counts:<br>TxBroadcast, TxMulticast, TxOverflows, TxFiltered, RxBroadcast, RxMulticast,<br>RxOverflow, RxFiltered                                                                                          |

| Other Statistics that can be derived from software, such as the outcome of packet classification,                                                                                                                                                                       |

may be added as needed.

\*May or may not be supported by MAC.

# 2.1.2 Power Management

Power Management supports four device states, D0 through D3. These states indicate the functional state of the adapter. Each state has a corresponding PCI bus state B0 though B3. Each bus state indicates the amount of power and functionality of the PCI bus. D0 & B0 are a fully functioning system which we will call the highest state. D3 & B3 are a fully powered down state, where the adapter may not have power, we will call this the lowest state. The transition of states D0 through D3 is performed through the driver. The transfer from B0 though B3 are PCI changes made to the PCI bus. A requirement for changing these states is that the adapter's device state must never be higher than the bus state. This is to say that before the PCI will move from D0 to and other state less than D0, the driver will be told to move the device state to a state that will be less than or equal to the impending bus state. Likewise when moving back toward D0, the bus state will move back toward B0 before the device state.

Typhoon supports all four device states, but D1, D2 and D3 are identical from a software functionality point of view:

<u>D0</u>

• The Adapter is ON, running and fully functional.

D1, D2, D3 Hot & Cold

- Power may be removed, if power is removed, it is expected that the host will assert RESET upon powering up. -B3 only

- No PCI bus transmission B3

- No PCI bus reception B3

- Wakeup events are supported as long as power has not been removed

- Sleep events (Enhanced Remote Wakeup) are supported as long as power has not been removed

- Changes in Power Management State are supported as long as power has not been removed

- The processor will reduce its clock rate to conserve power

- Promiscuous mode packet filtering is not supported.

#### D3 Disabled – ARM Clock Stoped

- PCI configuration state is preserved if power has not been removed

- No PCI bus transmission -B1

- No PCI bus reception B1

- Wakeup Events are supported

- Changes in Power Management State are supported if power has not been removed

- No Wakeup or Sleep events supported

- MAC will be held in reset

Before the bus state is changed from B0 to B1-3, the driver will be told what state we are moving to and what to support while asleep, i.e. wake-up events. Before acknowledging this information, the driver will pass this on to the adapter and the adapter will prepare to go to sleep. Once ready, the adapter will notify the driver and the driver can acknowledge that we are in the appropriate driver state.

### 2.1.3 Enhanced Remote Wakeup

#### Wakeup Events

While the adapter is in any non-D0 state that does include Power to the ARM, it has the ability to tell the host to wake up from its sleep mode based on a network event. A wake-up event is the network indication that we should request the hardware and software external to the adapter to put the system into the power state BO (working) by asserting the PME# signal on the PCI bus. Before being placed in a sleep mode, the driver will tell the adapter what conditions to look for as a wake-up event.

The following wake up events will be supported:

- Change in Network Link State.

- Receipt of Network Wakeup Frame.

- Receipt of Magic Packet.

- Sleep Timer: Typhoon will wake the system at a user-defined time in the future.

- Receipt of an ARP request directed to this host.

- Receipt of an ICMP Echo Request directed to this host.

#### Sleep Events (Deep Sleep)

It may be necessary during adapter sleep to occasionally send out network packets to the keep route tables and windows browse masters updated. This is required so that when the system wakes up the network will be better prepared to begin forwarding packets or to keep devices updated so that the packet required to wake the system will be delivered.

The sleep events that will be supported in Typhoon are:

- MAC keep-alives packets to keep Typhoon's MAC address alive in switches and multicast membership groups.

- ARP replies Typhoon will answer ARP requests for its IP address.

- Ping replies Typhoon will answer ICMP Echo Requests for its IP address

- Master Browser Host Announcements –Typhoon will announce its presence to the local Master Browser to maintain its position in the Network Neighborhood.

- DHCP Lease Renewal Typhoon will maintain the DHCP lease on its IP address while asleep.

- Novell Watchdogs Typhoon will respond to packets sent by a Novell server to maintain the client connection.

No encryption or decryption will be supported in sleep mode

# 2.1.4 Personal Firewall

This feature consists of 2 functions, broadcast throttling and DHCP prevention.

#### **Broadcast Throttling**

Broadcast throttling is implemented on both the transmit and receive data streams. The host can specify a transmit broadcast threshold as a percentage of the transmit bandwidth. The adapter monitors each data stream and discards any broadcast or multicast packets that exceed this limit.

The broadcast limit can be specified to an accuracy of 1%, Zero will discard all broadcast and multicast, 100 will discard none.

The adapter will implement this feature by calculating the broadcast usage over set time periods. For example, assume the adapter has an internal sample time period of 10ms, it is configured with a broadcast limit of 20%, and is transmitting at 100Mbs.

| Total Tx in sample period:           | 1Mbit   |

|--------------------------------------|---------|

| Broadcast Tx limit in sample period: | 200kbit |

In this example the first 20kbits of broadcast or multicast data in any 10ms period is transmitted. Once this threshold is reached all broadcast or multicast packets are discarded until the next period is started.

#### **DHCP Prevention**

This feature prevents the PC from acting like a DHCP server. All receive packets are passed through a DHCP filter and are discarded if they are deemed to be destined for the DHCP process. DHCP packets are recognized as being UDP/IP packets to the well known DHCP port (67).

©2000 3Com Corporation

# 2.1.5 I<sup>2</sup>C Serial Port Driver

An I<sup>2</sup>C interface is supplied by Typhoon for the purpose of connecting support slave devices, such as the National Semiconductor LM78 Microprocessor System Hardware Monitor used for temperature, voltage and fan speed monitoring. Devices such as this are slave only devices that may be written and read by Typhoon for system diagnostic purposes. Software support will need to be added as devices are selected.

This Typhoon I<sup>2</sup>C interface is a single master interface only, where Typhoon is the master. This is currently targeted for chip down applications.

# 2.1.6 Heartbeat

The Typhoon microcode provides a heartbeat signal to the host to indicate that the ARM9 is executing code. The ARM2Host Register 3 is continuously written with an incrementing 32 bit value by the ARM9. The rate of update of this register is on the order of 8ms per write, each write incrementing the value. The host can test for this register incrementing to determine if the ARM9 is not hung.

# 2.1.7 Off-line Diagnostics

Off-line Diagnostics refers to the ability to communicate with the adapter, from the network, for the purpose of running diagnostics. The intent of this communication is to create the ability to query the adapter about the state of the system. Off-line Diagnostics are not used to monitor an operational system. If the system is operational then communication between the network manager and the host can be used for system monitoring.

When the adapter boots it will load an image from non-volatile memory containing functionality to communicate over the network. Because the host may fail POST, the adapter must load this image at power-up rather than having the host download it to the adapter or having the host direct the adapter to load it from non-volatile memory. This will allow a diagnostic query/response even if the host POST fails.

When the adapter intercepts an Off-line Diagnostic request it can report the following:

- Report the current state of host/adapter communication

- Report last host value written to Port 80h

- Report diagnostic information for the adapter

- Report data from the host system memory (blue-screen)

#### Report the current state of host/adapter communication

The adapter can report the current state of host/adapter communication. When the diagnostic request is received, the adapter can send a 'ping' command to the host. If the host does not respond within a defined time period, then the adapter will report that the host is not communicating. The adapter could also determine that the host is not communicating if it is still waiting for the boot record from the host or if the host has not interrupted the adapter within a defined time period.

#### Report last Host value written to Port 80h

If the adapter determines that the host is not communicating then it could report the last value written by the host to Port 80h. When the host performs POST is uses I/O Port 80h to write a test point code value. If the host hangs during POST because of a terminal error condition then Port 80h will indicate the point at which the host halted execution. The Port 80h value will have to be decoded by either the adapter or the external application requesting the diagnostic report. The current proposal is for the external application to decode it because the adapter has limited storage. The main set of POST codes need to be identified which are common to the different BIOS versions and then determine if the adapter will have to report the BIOS vendor/version in the diagnostic report in order for the external application to decode the value.

#### Report diagnostic information for the Adapter

The adapter reports its POST result.

#### Report data from the Host system memory

If the adapter determines that the host is not communicating then it could read pertinent information from host system memory. The adapter could check whether or not the system timer is running and also report contents from the video buffer (blue-screen). The external application would have to interpret the contents.

There are a number of outstanding issues related to Off-line Diagnostics. The network management application (EdgeMonitor?) which will send the diagnostic request and interpret the response needs to be defined. The protocol (SNMP, AMP over UDP?), request and response can then be defined. Other issues can then be addressed such as whether or not the adapter should send unsolicited diagnostic reports (SNMP traps). Unsolicited reports would require the network management application to configure parameters on the adapter. Required parameters would include the destination address for unsolicited reports, an enable/disable diagnostic mode parameter, and an identifier for indicating the type of information which should be reported (i.e., only report host/adapter communication failure). Required parameters such as the destination address would need to be stored in the adapter's NV Device so that they are maintained through a reset. Another issue which needs to be addressed is whether or not the adapter will always intercept the diagnostic request or only look for the diagnostic request when it has detected that the host is no longer communicating? If the adapter ignores the request because the host is operational then who responds, the TDI?

There are no current plans for the following Off-line Diagnostic support:

- Report logged data. The adapter could be used to store data logged by an application. Pertinent

information could be stored in non-volatile memory if it is useful after a power-cycle (the adapter will

restrict the frequency and type of information stored to non-volatile memory). No application has

been identified, maybe EdgeMonitor?

- Report diagnostic information from the devices on the l<sup>2</sup>C interface. No devices are on the adapter's l<sup>2</sup>C interface.

# 2.2 Performance Enhancements

### 2.2.1 TCP/IP Checksum Generation and Verification

#### **IP Checksum**

The processor on the adapter will support an IP checksum insertion and verification for packets using IPv4 for the IP forms of Ethernet Type 0x0800, 802.2 and SNAP.

Reference Microsoft document "Task Offloading in NDIS 5.0 for Windows NT5.0" for more details on IP Checksum Offloading.

#### **TCP Checksum**

The processor on the adapter will support a TCP checksum insertion and verification for packets using TCP/IP. The processor will calculate the checksum using the hardware checksums available through the packet DMA process. The checksums from the DMA will be corrected by software for data not included in the actual checksum calculation.

For transmit packets, the TCP Pseudo Header Checksum should be in the TCP checksum field.

Reference Microsoft document "Task Offloading in NDIS 5.0 for Windows NT5.0" for more details on TCP Checksum Offloading.

**NOTE**: The adapter will not support the insertion or verification of TCP checksums on fragmented IP packets since it will not store the packet for fragmentation or re-assembly.

# 2.2.2 TCP Segmentation

TCP can pass a buffer, containing a "large datagram" bigger than the MTU of the medium and the MSS, to be transmitted. The goal is to reduce host CPU utilization and number of interrupts, and to improve performance and scalability.

A session MSS will be passed down to the adapter along with the datagram, telling Typhoon the segment size of the TCP payload for the packet transmission. The size of the datagram first datagram is specified in the IP Total Length field. From this value the MSS could be extracted through calculations, however, the MSS is pass to the driver through the NDIS\_PER\_PACKET\_INFO\_FROM\_PACKET structure. The total Length of the packet and MSS will be sent to the adapter in a TCP option header.

The typhoon adapter will not support MSS less than 4 bytes. The driver should fail packets with an MSS less than 4 byte without sending to the adapter.

The large datagram will be passed to Typhoon as an oversized MAC frame, with template frame header, IP header and TCP header. TCP protocol can pass down only payload of size within the advertised window of the other side. Typhoon will handle the large datagram as a shorthand request to transmit a series of normal TCP datagrams, with limited protocol handling for each segment of

©2000 3Com Corporation

transmitting. For the handling of large datagram sends interleaving small sends (regular sends), the adapter maintains an order-preserving queue for each session involving large sends.

**NOTE**: The receive ACK, retransmission, and window maintenance will not be handled by Typhoon.

Typhoon takes the incoming datagram and carves it up into fragments based on the MSS passed down. All packets but the last will have a payload exactly MSS bytes in size. The last may be smaller.

The header of outgoing packets is derived from the template header on the incoming datagram as follows:

- 1) Unless otherwise specified, fields are simply copied from the template to the outgoing packet without change.

- 2) The MAC header is used exactly.

- 3) The IPV4 header is copied exactly, except for IP total length, which will be computed correctly for each datagram transmitted, and the IP identification (ID) field, which is advanced for each packet, with the first packet's ID copied from the template.

- 4) The IP header checksum is computed for each datagram transmitted.

- 5) The TCP header is copied exactly, except the sequence number (SEQ), which will be advanced correctly for each datagram transmitted, with the first SEQ copied from the template and succeeding ones advanced by MSS bytes.

- 6) The FIN and PUSH bits are set to zero for all but the last packet. These bit will be set to the value in the template on the last packet in the datagram transmitted.

- 7) The TCP checksum is computed for each datagram transmitted.

- 8) IP and TCP Options will be allowed. The adapter will not alter their value.

Reference Microsoft document "Task Offloading in NDIS 5.0 for Windows NT5.0" for more details on TCP Segmentation Offloading.

# 2.2.3

# 2.2.4 IEEE 802.1p/Q Class of Service Priorities

Transmit priority levels will be supported by the adapter. The current plans are to support 8 priority levels internal to Typhoon. Packets will be transmitted over the wire in priority order, not in the order received from the host. The prioritizing of the packets is specified by the host and contained in the Priority field in the 802.1 Q tagged frame.

In addition to the tagging service on a per-packet basis, Typhoon supports COS (Class of Service) policy negotiation for establishing COS interoperability with remote hosts. Typhoon maintains a table of remote host addresses with which Typhoon has a bilateral understanding of COS tagging. COS tagging is performed only for those packets to or from those hosts which appear in the table.

Typhoon initiates the COS negotiation when an outbound packet with a tagging request is first received that is destined to a remote host which is not listed in the COS table. The negotiation is performed via ICMP Ping messages (Details TBD).

©2000 3Com Corporation

Typhoon forwards all traffic to the remote host without tagging prior to the completion of COS negotiation.

### 2.2.5 IPSec

Typhoon will assist the host in performing various security services for traffic at the IP layer, in the IPv4 environment.

Typhoon provides support for IPSec as a BITS (Bump-in-the-stack) implementation

Typhoon's support for IPSec conforms to the following draft standards:

| draft-ietf-ipsec-arch-sec-02.txt    | Obsoletes RFC 1825 |

|-------------------------------------|--------------------|

| draft-ietf-ipsec-auth-header-03.txt | November 1997      |

| draft-ietf-ipsec-esp-v2-02.txt      | November 1997      |

#### 2.2.5.1 Off-loading IPSec processing to Typhoon

Typhoon provides support only for calculation-intensive part of IPSec, such as ICV (Integrity Check Value) calculation and encryption/decryption. Typhoon expects the host itself to handle all other protocol related tasks, such as key management, Security Policy and Security Association establishment, PMTU discovery, and traffic filtering prior to enforcing various security policies.

Due to its limited buffer capacity, incoming fragmented IP datagrams will not be re-assembled on the adapter unless they are less than 2 fragments. No IPSec processing will be done for the other general cases. However, Typhoon makes no assumption about the fragmentation status of the outbound traffic that is to be processed by the Ipsec logic, which may be fragmented (in tunnel mode) if the host chooses to handle them. Correspondingly it makes no assumption about the fragmentation status of the inbound packets which appear after the Ipsec processing.

To request for Typhoon's assistance in IPSec processing, the requester must provide place holders for all AH headers, ESP headers, and all authentication data, properly embedded within the datagram per IPSec specification. Typhoon also expects all explicit DES padding except in the case of a large TCP datagram that is to be segmented by the adapter.

For outgoing traffic for which IPSec processing is requested, Typhoon expects all the Security Associations have been resolved by the host, which include the key management, Security Association establishment and creation, and the traffic classification to determine the proper Security Association. Typhoon will supply the IV (Initialization Vector, randomly selected per packet. Typhoon will not attempt to extend the CBC across the packets), calculate the Integrity Check Value (ICV), and encrypt data for ESP or BITW request. The SA selector matching and filtering, the assignment of the SPI value, the maintenance of anti-replay sequence number and windows, and all necessary DES padding are the responsibility of the requester.

For incoming traffic for which IPSec processing is requested, the adapter will generate the ICV and decrypt them per Security Association identified by the triplet <protocol-type, destination-address, SPI>. The SA selector matching and filtering and the enforcement of anti-replay policy are the responsibility of the requester. Note also that in Phase I the adapter performs "Crypto-only" functions for IPSec. The

©2000 3Com Corporation

| T2 Software Function | al Description |

|----------------------|----------------|

|----------------------|----------------|

parsed IPSec headers, if nested, may not match the order required by the Security Policy, that must be re-parsed and checked by the host to enforce the relevant Security Policies.

Limited auditing will be provided by Typhoon for traffic on which the on-board IPSec processing is performed. All auditing reports are limited to local node. There is no support for the receiver to transmit any message to the purported transmitter in response to the detection of an auditable event.

#### 2.2.5.2 Combination of Security Associations

Typhoon supports the host both as an IPSec host and/or an IPSec Security Gateway.

For outbound traffic, Typhoon supports the following combination of AH and ESP headers:

- 1. Tunneling of clear-text plain packet.

- 2. Basic IPSec packet: This is a combination of AH and ESP in the following two modes:

| Transport                   | <u>Tunnel</u>                |

|-----------------------------|------------------------------|

| 1. [IP1] [AH] [upper]       | 4. [IP2] [AH] [IP1] [upper]  |

| 2. [IP1] [ESP] [upper]      | 5. [IP2] [ESP] [IP1] [upper] |

| 3. [IP1] [AH] [ESP] [upper] | 6. [IP2] [AH] [ESP] [upper]  |

3. Tunneling of Basic IPSec Packets (defined in 2. above) which have already undergone one level of IPSec processing.

For inbound traffic, Typhoon supports any combination of AH and ESP modes, as long as the Security Association of each triggered IPSec processing is unambiguously defined. However, only one level of nesting is supported per single round of IPSec processing on the adapter.

Additional nesting of Security Associations, for both the inbound and outbound traffic, can be accomplished by utilizing Typhoon as a BITW outboard crypto-processor to create the IPSec header calculation, prior to the transmitting of the IPSec packets.

#### 2.2.5.3 Performance consideration

Typhoon utilizes the on-board hardware (Sidewinder) to do most of the IPSec processing. Sidewinder is capable of performing a combination of HASH and DES in one pass. For example, for outbound traffic in transport mode with an AH and an ESP without ICV, the IPSec processing requires only a single pass through the Sidewinder. However, for multiple level of nesting or combination of an AH and an ESP with ICV, multiple passes through the Sidewinder are required. The performance of the IPSec processing is strictly a function of the number of Sidewinder passes needed to complete the processing.

For properly aligned packets, Sidewinder can deliver around 200 mega-bps per pass at 80 mega-Hz clock.

Examples:

Packet of format [IP1] [ESP with ICV] [Upper] require 1 pass. Packet of format [IP1] [AH] [ESP without ICV] [Upper] require 1 pass. Packet of format [IP2] [ESP with ICV] [IP1] [AH] [ESP with ICV] [Upper] require 3 passes.

#### 2.2.5.4 Conformance requirements

The following mandatory-to-implement algorithms are supported:

HMAC with MD5 [C. Madson & R. Glenn, "The Use of HMAC-MD5-96 within ESP and AH", Internet Draft, 7/2/97.]

- HMAC with SHA-1 [C. Madson & R. Glenn, "The Use of HMAC-SHA-1-96 within ESP and AH", Internet Draft, 7/2/97.]

- DES in CBC mode [C. Madson & N. Doraswamy, "The ESP DES-CBC Cipher Algorithm With Explicit IV", Internet Draft, 07/02/1997."]

#### 2.2.5.5 IPSec datagram flow description

The passing of network packet through the TCP/IP stack, the NDIS driver, and Typhoon can be characterized as follows:

- 1. On initialization, the Typhoon NDIS driver will declare its IPSec capabilities through the NDIS\_TASK\_IPSEC structure as follows:

- ? AH+ESP combinations supported.

- ? IP options supported

- ? Query SPI supported

- ? For AH, MD5, SHA-1 are supported for both the Tunnel and Transport Mode, and for both Send and Receive. Only Ipv4 is supported (Ipv6 is not supported).

- ? For ESP, DES and Triple-DES are supported for both the Tunnel and Transport Mode, and for both Send and Receive. Only Ipv4 is supported (Ipv6 is not supported).

- ? Only CryptoOnly is supported

- 2. Typhoon also has a built-in hardware digital non-deterministic random number generator. When requested, Typhoon can provide a specified set of random numbers to the host, which can be a basis of various key generation and random number seeding.

- 3. Prior to the sending and receiving of IPSec network packets, the Stack must establish its Security Policy Database (SPD) and Security Association Database (SAD). Part of the SAD will be passed down to the NDIS Driver through OIDs, one for the creation of a SA (OID\_TCP\_TASK\_IPSEC\_ADD\_SA) and one for the deletion of a previously created SA (OID\_TCP\_TASK\_IPSEC\_DELECT\_SA). The OIDs will be used to maintain the SAD inside the Driver during the on-line operation.

- 4. The NDIS Driver strips off the Selector part of the SAD (retains only the Destination Address specification) and passes down to Typhoon only information related to the HASH and DES algorithms, which include the algorithm descriptor, the keys, and the padding convention. The adapter produces IPAD keys and OPAD keys in preparation for the HASH operation. For the adapter, a SA is identified either through the SA id on sending, or the triplet <destination address, SPI, ESP or AH> on receiving traffic. Note that as far as the adapter is concerned, the SPI is only meaningful for the inbound traffic. The creation and deletion of SA for Typhoon is typically carried out inband. (For Phase I, the adapter is used as a outboard crypto-engin that does not perform IPSec selector functions. The identification of SA for the outbound traffic is also done through the SPI.)

- 5. Once the SAD is established on both the host side and the Typhoon side, the IPSec traffic is then allowed to flow. In the following example, we use a TCP datagram in Transport mode as an example.

©2000 3Com Corporation

- 6. On sending, the Stack prepares all the headers for IPSec based on its SPD and SAD. Since Typhoon is declared as CryptoOnly, all buffer space for AH, ESP, and trailing padding and HASH value is pre-allocated by the Stack. In addition to the IP header and TCP header, the Stack is also responsible for the following task:

- ? In AH, it fills the Next Header field.

- ? The TCP datagram is encapsulated as an ESP, with the TCP header embedded at offset 8+length-of-IV (8 bytes). The host is responsible for allocating space for all padding bytes in all cases.

- 7. The NDIS Driver accepts the outbound network packet (in clear text), figures out the mode and nesting requirement (Transport, Tunnel, or combination) based on the IP header, AH header, and ESP format, and for each AH or ESP, searches for the SA in its SA Database based on the following Selectors (This is performed per outbound packet):

- ? Source Address

- ? Destination Address

- ? Transport Protocol

- ? Source Port (in TCP header)

- ? Destination Port (in TCP header)

- ? AH or ESP

- ? TOS (Type of Service)

- ? Data Sensitivity Level (IP option, IPSO/CIPSO labels)

- 8. After identifying the proper Security Associations, one per AH or ESP, the Driver then performs the following tasks:

- ? It fills the Payload Length, SPI and Sequence Number Fields in the AH per identified SA.

- ? It fills the SPI, the Sequence Number, Pad Length, all the Padding bytes, and Next Header in ESP per identified SA.

- ? It formulates an *Option Descriptor* containing the identifier of the identified SA's in an array. The multi-fragment frame will then be placed in the Tx Descriptor Ring.

- 9. The adapter will retrieve the IPSec network packet from the Tx Descriptor Ring, walk down the packet to parse the various IP headers and to determine the nesting levels, and based on the information passed in via the *Option Descriptor*, identify all the SA's. Based on the SA's, the adapter formulates a request to Sidewinder with the following data:

- ? IV (Initialization Vector, 64 bits. This is for DES only.) The adapter provides a software random number generator for IV. It initially seeds the IV with a hardware-generated random number produced by the Sidewinder's Randomizer. It then saves the last 64-bit of the DES or HASH output and uses it as the IV for the succeeding round of DES. The adapter periodically re-seeds the generation of IV with new random number produced by the Sidewinder.

- ? DES key (64 bits).

- ? 2-key Triple-DES (128 bits) or 3-key Triple-DES (192 bits).

- ? HMAC IPAD/OPAD keys, four 32-bit words for MD5, five 32-bit words for SHA-1

- ? HASH offset and length.

- ? DES offset and length.

- ? Op code to indicate the algorithm.

- 10. For AH processing, prior to issuing the request to Sidewinder, the adapter must save all the "mutable" fields, plug in the predictable value expected at the receiving side if predictable, and zero out the rest for the HASH processing. It restores those fields after the Sidewinder processing. The mutable fields are:

- ? Destination Address (with loose or strict source routing), mutable but predictable

- ? TOS

- ? Flags

- ? Fragment Offset

- ? TTL

- ? Header Checksum

- ? Options (Each individual options must be check for mutability. If an option is classified as mutable, the entire option is zeroed for ICV computation purposes.)

- 11. For HASH, the Sidewinder outputs a Digest of equal length as the IPAD/OPAD keys. The adapter truncates the Digest to a 96-bit value before placing it into the packet.

- 12. Depending on the depth of nesting, the adapter may feed the same IPSec packet through Sidewinder several times. However, in most common cases, namely the ESP with Authentication data in Transport mode, one round through the Sidewinder will accomplish both the DES and HASH.

- 13. After the IPSec processing, the network packet is put on the wire like all other normal non-IPSec packet. Note that the adapter assumes that the final frame length is within the MTU of the local Ethernet. In other words, the Stack and the Driver is responsible for ensuring the final IPSec packet is within the MTU constraints.

- 14. For inbound traffic, IPSec processing is the reverse of the above logic, with the following exceptions:

- ? The adapter does not have the ability to handle the general case of fragmented IP packet. If the Fragment Offset is non-zero, or the More Fragments bit is set, the packet is considered fragmented. If the number of fragments is not more than 2, then the adapter will attempt to put them together before applying the IPSec processing. All other cases are "punted" to the host. In other words, the host is expected to handle the re-assembly. The host must have a software implementation of IPSec so that the fragmented IP packets can be handled in the host.

- ? For non-fragmented network packet, the adapter uses the triplet <Destination Address, SPI, AH or ESP> within the packet to look up its local copy of SAD. Once the SA is found, the adapter will perform the HASH or DES accordingly. This look-up is performed per packet.

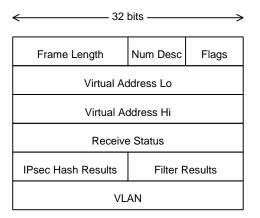

- ? The result of HASH and DES is returned directly via the response frame.

- ? The host is expected to verify the Sequence Number per SA. The NDIS driver is also expected to apply the Selector per SA to further filter out unwanted packets. Note that since the adapter is CryptoOnly and does not handle the IPSec Sequence Number, it can not regulate the traffic to prevent the Denial of Service attack.

# 3. Theory of Operation

# 3.1 Host Adapter Interface

Information is passed between the host and the adapter using shared data structures in the host's memory.

# 3.1.1 Packet Type

There are two types of information passed between the host and the adapter:

| Network Packets | Contains either Transmit or Receive data framed for network transmission. Data in a network packet is formatted in the standard <i>network byte order</i> .                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Packets | Contains meta-information, which is for initializing or setting of operation<br>environment and for maintaining context and state that controls the packet<br>handling. It is either a command, or a response to a previously issued<br>command. |

# 3.1.2 Data Format and Alignment Convention

The adapter card stores data in little endian format as does the Intel based. Therefore there is no need to convert the data structure in the control information package between the two. Control data must be aligned on a 32-bit word boundary on both platforms in order to avoid *endianess* conversion. However, since network byte order is specified as big endian, the adapter must convert any data item in the packet data into the correct byte order if it needs to manipulate it as integers.

©2000 3Com Corporation

For IP packet data, the IP header must also be aligned on a 32-bit word boundary in adapter memory so that all IP header structures can be accessed conveniently (after *endianess* conversion). However, since the MAC header is of size either 14 bytes or 22 bytes, it must be aligned on an *odd* 16-bit boundary so that the IP header can be correctly aligned. Other than the processing of VLAN tag or large TCP packets, the adapter is not expected to break up the packet or move around parts of it.

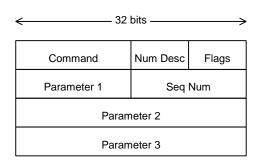

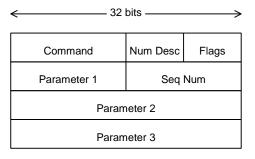

The control data is identified by a *command code*, followed by the Sequence number and one or more parameters. The *command code* indicates the kind of services requested by the command. The *Sequence number* is initialized by the issuer of the command and is carried by the response in responding to the original command. However, it is treated as opaque data to the receiver and must not be altered.

Control data is passed either in-band or out-of-band. In-band control data is synchronized to the packet data stream and must be handled in the order received relevant to the packet data. Its execution sequence within the packet data stream affects the function of the In-band control data. Due to the inband nature of the control data, the processing duration should be reasonably short in order not to delay normal flow of packet data traffic.

# 3.2 Host Adapter Interface Ring Buffer

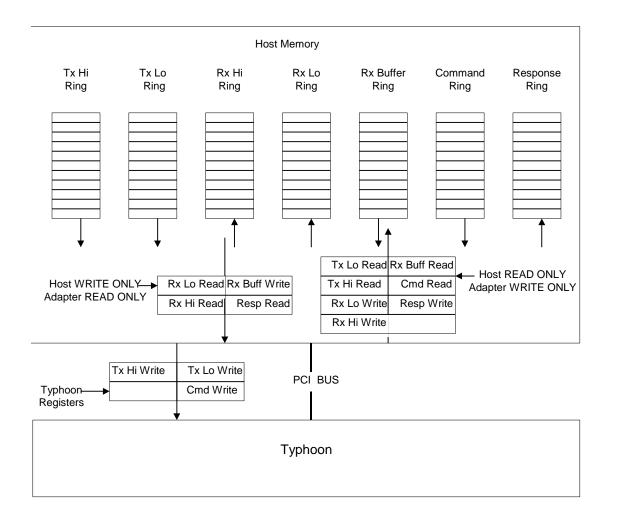

A number of ring buffers are set up in the host memory, which are dedicated for either host-to-adapter or adapter-to-host communication.

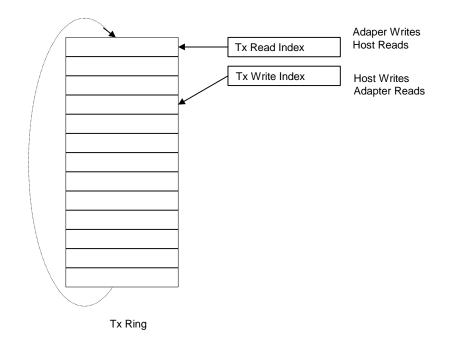

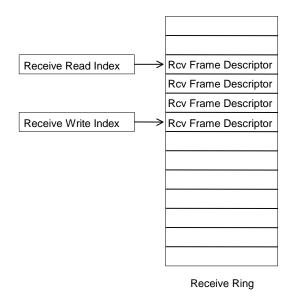

In the case of a ring buffer used for host-to-adapter data transfer, 2 index variables, a write and a read index are used to manage the ring. The host writes data into the ring and updates the write index to inform the adapter of the new data. The adapter reads data from the ring and updates the read index to inform the host that the space is available for re-use.

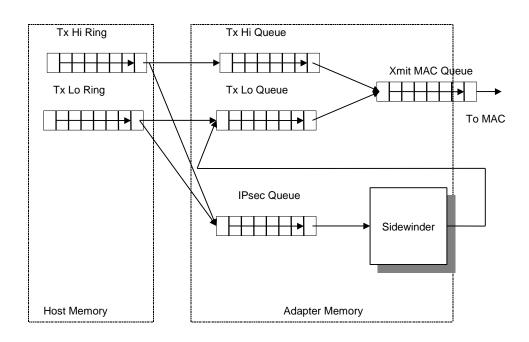

There are 6 ring buffers defined, 2 for transmit, 2 for receive and 2 for control, they are:

| Tx Rings (Hi & Lo priority) | contain packet descriptors for packets to be transmitted or control commands to be executed in-band through the adapter.                                                                                                     |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rx Rings (Hi & Lo priority) | contain rings of descriptors that the adapters writes to give the host access to received packets, to return response data or status for previously issued host command, or to issue a request to the host from the adapter. |

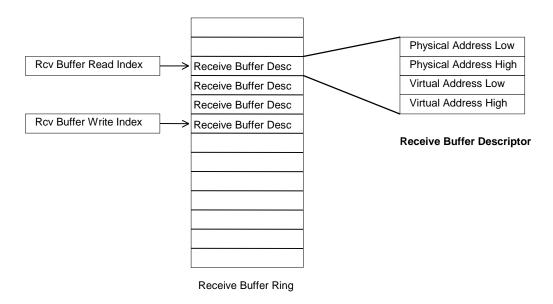

| Rx Buffer Ring              | contains pointers to maximum size empty buffers that the adapter can use to store received packets.                                                                                                                          |

| Command Ring                | contains command descriptors for host-to-adapter control information.                                                                                                                                                        |

| Response Ring               | contains response descriptors for adapter-to-host control information.                                                                                                                                                       |

All 7 rings and the index variables are shown in the following diagram. Note that only 3 of the indexes use registers, the other 11 are part of host resident data structures.

All rings have the following restrictions:

- Rings have base addresses of 64 bits, but no ring can traverse a 32 bit address boundary, i.e. the top 32 bits of the address of any element in a ring is constant.

- The rings must always have at least one empty location. This is due to the fact that when the read and write indexes are equal the ring is empty. The write index must never be incremented such that it equals the read index when the ring is full.

The index variables into the 7 rings are grouped into 2 data structures in host memory, one containing the data that is read-only to the adapter, the other that is write-only to the adapter. All but 3 of the indexes are stored in these structures. The other 3 indexes, *Tx Hi Write Index, Tx Lo Write Index* and *Command Write Index* are stored in a dedicated Host-to-Arm register.

The reason for 2 different forms of storing the indexes is to ensure immediate action on some and more delayed on others. Also host register writes are relatively efficient and can be used to interrupt the adapter, but Arm-to-Host register operations are inefficient and are avoided. The indexes in registers cause interrupts to the ARM when written by the host. The Host-to-Arm indexes stored in host memory are periodically polled (using DMA) by the adapter to determine if they have been updated by the host. The Arm-to-Host indexes are periodically updated by the adapter using DMA writes.

The following register assignments are used (note that since the indexes are 16 bits, each register contains 2 index values).

©2000 3Com Corporation

### Host to Adapter Registers:

| Register                                                                         | •                             | Runtime                                                                                                        |

|----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|

| Register<br>Register<br>Register<br>Register<br>Register<br>Register<br>Register | 1:*<br>2:*<br>3:*<br>4:<br>5: | unused<br>PCI Tx Hi Write Index,<br>PCI Cmd Write Index<br>PCI Tx Lo Write Index<br>unused<br>unused<br>unused |

| Register                                                                         |                               | unused                                                                                                         |

\* These registers cause an ARM interrupt when written by the host.

# Adapter to Host Registers

| Register             | Runtime             |

|----------------------|---------------------|

| Register             | PCI Status Register |

| Register<br>Register | unused<br>unused    |

| Register             | unused              |

The 2 data structures in host memory that contain the ring indexes that are not stored in memory are described below. The **HostToArm** structure is READ ONLY to the Typhoon, the **ArmToHost** structure is WRITE ONLY to the Typhoon.

### ArmToHost data structure

32bit: RxHiRead 32bit: RxLoRead 32bit: RxBuffWrite 32bit: RespRead

#### HostToArm data structure

| 32bit: | TxLoRead   |

|--------|------------|

| 32bit: | TxHiRead   |

| 32bit: | RxLoWrite  |

| 32bit: | RxBuffRead |

| 32bit: | CmdRead    |

| 32bit: | RespWrite  |

| 32bit: | RxHiWrite  |

# 3.3 Packet Flow Convention

Due to its limited storage space, all packet buffers reside in the host memory. The function and structure of those interface ring buffers reflect this asymmetry.

The passing of network packets generally does not expect a response or status return. The transmit buffer will be returned to the host after the adapter has transmitted the packet, to allow the host to free the buffer memory.

On the other hand, the passing of control packets usually follows the request/response pattern. The issuer of the request must properly prepare all the buffers to house both the input parameters and the response (output) data.

The passing of packet through the ring buffers can be characterized as follows:

- Transmit network packets are passed from the host to the adapter through one of the Tx Rings.

- Host-to-adapter control packets can be passed to the adapter either in-band or out-ofband. The general case is to pass control information using the out-of-band data path, which uses the *Command Ring*. Control information that is synchronized to the data stream may be passed in-band through the *Tx Rings*. In either case the response is returned using the *Response Ring*.

- Received network packets are passed from the adapter to the host through the *Receive Ring*. The adapter must acquire a buffer from the host through the *Rx Buffer Ring* before it can send the packet to the host.

- Adapter-to-host control packets are relatively rare and typically do not expect response data to be returned. The adapter uses the *Response Ring* to pass the control packets to the host.

- The response data to an adapter-to-host control packet, if any, will be returned through the *Response Ring*.

# 3.3.1 Host-to-adapter Packet Flow

Packets are transmitted to the adapter by the host writing descriptors into shared ring buffers in host memory. Access to the ring buffer is controlled by two index variables, which are stored in host memory. The *Tx Write Indexes* and the *Tx Read Indexes* are used as follows.

The indexes are initialized to point to the start of an empty ring (initialized to zero). The *Tx Write Indexes* point to the next location in the ring into which the host will write data, they are never written by the adapter. The *Tx Read Indexes* point to the next descriptor to be read by the adapter, they are updated by the adapter after the descriptor has been copied to internal adapter memory and are never by written by the host except during initialization. The 2 indexes being equal indicate the ring is empty. The write index is never incremented to equal the read pointer for a full ring. This implies that the ring can not be completely filled and at least one entry must remain free to prevent the 2 indexes becoming equal.

To transmit a frame the host writes a frame descriptor and multiple fragment descriptors into the ring. It then updates the write index and writes the value to the *PCI Tx Write Index* register. This interrupts the ARM which copies the complete *Packet Descriptor Block* to the adapter.

©2000 3Com Corporation

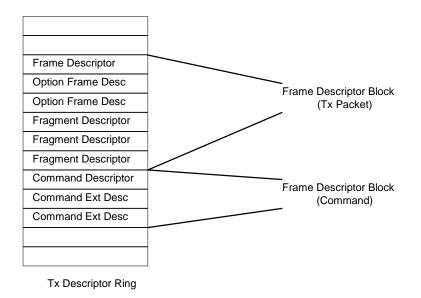

Transmit frames are described by a sequence of descriptors formed into a *Frame Descriptor Block*. A *Frame Descriptor Block* describes a single frame and consists of one *Frame Descriptor* followed by one or more *Option Frame Descriptors* followed by one or more *Fragment Descriptors*.

A *Frame Descriptor Block* may wrap in the *Tx Ring.* The ring will be sized such that individual descriptors will never wrap, i.e. each data structure will always be in contiguous memory. This is achieved by defining all descriptors to be the same size (16 bytes) and ensuring that the ring is a multiple of the descriptor size.

Proprietary & Confidential03/12/0112/03/0103/12/0112/03/0103/12/0112/03/01

#### **Responses To Transmitted Packets**

In the general case for transmitting packets, the following sequence is followed:

- 1. The host transmits a packet to the adapter.

- 2. The adapter transmits the packet over the network and informs the host that the buffer can be freed.

- 3. The host frees the buffer.

There is no positive or negative acknowledge of the result of a packet transmit. If the adapter fails to transmit a packet it may still return the buffer to be freed without informing the host that an error occurred.

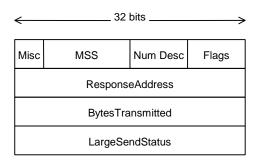

In the case of large transmitted packets that require TCP segmenting by the adapter an acknowledgement for each large packet is required. The more common case of successful transmission requires a positive acknowledgement. This is done implicitly by the freeing of the transmit buffer, i.e. in the case where TCP segmentation occurs, the freeing of the buffer in the normal manner implies a successful transmission of the whole packet. If an error occurs then an error response is returned on the *Response Ring*.

The same mechanism is used when transmitting encrypted packets. If the adapter successfully encrypts and transmits a packet it implicitly returns a positive acknowledge by freeing the buffer. If an error occurs it returns an error response on the *Response Ring*.

#### **Packet Transmit Descriptors**

The main purpose of the *Tx Ring* is to pass data packets to the adapter for transmission. The general case is transmitting non-encrypted, non-segmented packets and the format of the descriptors is tuned for this purpose. In this case a packet is described by a single *Data Frame Descriptor* followed by one or more *Fragment Descriptors*.

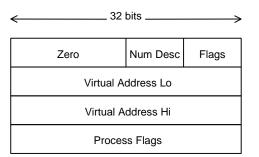

Tx Frame Descriptor

A *Tx Frame Descriptor* is the first descriptor in a *Frame Descriptor Block* and contains information pertinent to the complete frame.

Tx Frame Descriptor

The descriptor has the following fields:

| Flags [0:7]                 | <ul> <li>[0:2] - DescriptorType. (Set to 001 - Tx Frame Descriptor)<br/>000 - Fragment Descriptor</li> <li>001 - Tx Frame Descriptor</li> <li>010 - Command Frame Descriptor</li> <li>011 - Option Descriptor</li> <li>100 - Receive Descriptor</li> <li>101 - Response Descriptor</li> </ul> |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | [3:7] – Reserved. Set to zero.                                                                                                                                                                                                                                                                |

| NumDesc [8:15]              | The number of descriptors following this one in this <i>Frame Descriptor Block</i> . This includes <i>Option Descriptors</i> and <i>Fragment Descriptors</i> . It may be zero, one, or many.                                                                                                  |

| Zero [16:32]                | May be used for the Number of bytes in the complete packet. If zero then this field contains no valid data.                                                                                                                                                                                   |

| Virtual Address Low [0:31]  | The least significant 32 bits of the virtual address in host memory<br>of the packet. This value is passed back from the adapter to the<br>host when the host can free the packet memory. The adapter does<br>not use this field.                                                             |

| Virtual Address High [0:31] | The most significant 32 bits of the virtual address in host memory<br>of the packet. This value is passed back from the adapter to the<br>host when the host can free the packet memory. The adapter does<br>not use this field.                                                              |

| Process Flags [0:31]        | [0] – Do Not Add CRC. If 0 then the adapter adds a frame CRC else the CRC is already included in the packet.                                                                                                                                                                                  |

|                             | [1] – <i>IP Checksum</i> . If 1 then the adapter computes and inserts the IP checksum.                                                                                                                                                                                                        |

|                             | [2] – <i>TCP Checksum</i> . If 1 then the adapter computes and inserts the TCP checksum.                                                                                                                                                                                                      |

|                             | [3] – <i>TCP Segment</i> . If 1 then the adapter must perform TCP segmentation on the frame.                                                                                                                                                                                                  |

|                             | [4] – Insert VLAN. If 1 then the adapter must insert the previously<br>stored VLAN tag into the frame.                                                                                                                                                                                        |

|                             | [5] – IPSec If 1 then the adapter must perform some type of<br>IPSec functionality on the frame. The encryption parameters are<br>specified in an Extension Frame Descriptor.                                                                                                                 |

|                             | [6] – Priority Valid. Set if Priority field is valid                                                                                                                                                                                                                                          |

|                             | [7] – <i>UDP Checksum</i> . If 1 then the adapter computes and inserts the UDP checksum.                                                                                                                                                                                                      |

|                             | [8] – Pad Frame. If 1 then the pads the frame with zeros to the<br>length specified in the Pad Pkt field. This option is only valid is the<br>adapter is appending a MAC CRC.                                                                                                                 |

|                             | [9:11] – Reserved. Set to zero                                                                                                                                                                                                                                                                |

|                             | [12: 27] VLAN and Priority Value. Priority located at bits [20: 22].                                                                                                                                                                                                                          |

|                             |                                                                                                                                                                                                                                                                                               |

©2000 3Com Corporation

[28:31] – *Reserved.* Used internally by Typhoon Software. Set to zero.

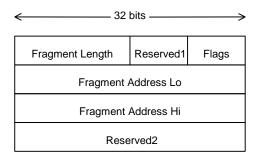

Fragment Descriptor

A number of *Fragment Descriptors* describe the multiple fragments that form the packet data. Each one points to a buffer in host memory and contains any other pertinent information on this single fragment.

Fragment Descriptor

The descriptor has the following fields:

| Flags [0:7]                  | <ul> <li>[0:2] - DescriptorType. (Set to 000 - Fragment Descriptor)</li> <li>000 - Fragment Descriptor</li> <li>001 - Data Frame Descriptor</li> <li>010 - Command Frame Descriptor</li> <li>011 - Option Descriptor</li> <li>100 - Receive Descriptor</li> <li>101 - Response Descriptor</li> <li>[3:15] - Reserved. Set to zero.</li> </ul> |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved1 [0:7]              | Set to zero.                                                                                                                                                                                                                                                                                                                                  |

| Fragment Length [0:15]       | The number of bytes contained in the fragment.                                                                                                                                                                                                                                                                                                |

| Fragment Address Low [0:31]  | The least significant 32 bits of the physical address in host memory of the fragment buffer.                                                                                                                                                                                                                                                  |

| Fragment Address High [0:31] | The most significant 32 bits of the physical address in host memory of the fragment buffer.                                                                                                                                                                                                                                                   |

| Reserved [0:31]              | Set to zero.                                                                                                                                                                                                                                                                                                                                  |

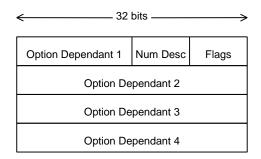

# **Option Frame Descriptor**

An *Option Frame Descriptor* contains information pertinent to a frame in addition to the information in the preceding Tx *Frame Descriptor*. It is used in special cases, such as when the transmitted frame requires IPSec processing or TCP segmentation.

One or more *Option Frame Descriptors* may be included in a *Frame Descriptor Block*. They always follow the Frame Descriptor and precede the *Fragment Descriptors*. It consists of the following fields:

Option Descriptor

| Flags [0:7]               | <ul> <li>[0:2] - DescriptorType. (Set to 011 - Option Frame Descriptor)<br/>000 - Fragment Descriptor<br/>001 - Data Frame Descriptor<br/>010 - Command Frame Descriptor</li> <li>011 - Option Descriptor</li> <li>100 - Receive Descriptor</li> <li>101 - Response Descriptor</li> </ul> |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | [3] – Unused. Set to zero.                                                                                                                                                                                                                                                                |

|                           | <ul> <li>[4:7] – Type. Defines the type of extension descriptor</li> <li>0 – IPSec Type Option Descriptor</li> <li>1 – TCP Segment Type Option Descriptor</li> </ul>                                                                                                                      |

| NumDesc[0:7]              | The number of descriptors describing this option (including this one. It cannot be zero. If multiple options are included in the same <i>Frame Descriptor Block</i> then this value only specifies the number for this particular option.                                                 |

| Option Dependant 1 [0:15] |                                                                                                                                                                                                                                                                                           |

| Option Dependant 2 [0:31] |                                                                                                                                                                                                                                                                                           |

| Option Dependant 3 [0:31] |                                                                                                                                                                                                                                                                                           |

| Option Dependant 4 [0:31] |                                                                                                                                                                                                                                                                                           |

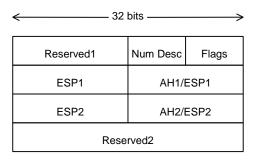

# IPSec Option Frame Descriptor

The only defined type of Option Frame Descriptor at present is used when transmitting packets that are encrypted by the adapter. These are defined as follows:

**IPSec Option Descriptor**

| Flags [0:7]       | <ul> <li>[0:2] - DescriptorType. (Set to 011 - Option Descriptor)<br/>000 - Fragment Descriptor<br/>001 - Data Frame Descriptor<br/>010 - Command Frame Descriptor</li> <li>011 - Option Descriptor<br/>100 - Receive Descriptor<br/>101 - Response Descriptor</li> </ul> |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | [3] – Unused. Set to zero.                                                                                                                                                                                                                                                |

|                   | <ul> <li>[4:7] – OptionType. Set to 0 (IPSec Type Option Descriptor).</li> <li>0 – IPSec Type Option Descriptor</li> <li>1 – TCP Segment Type Option Descriptor</li> </ul>                                                                                                |

| NumDesc[0:7]      | The number of <i>Option Descriptors</i> (including this one) for this option. Equals 1 in this case.                                                                                                                                                                      |

| IPsecFlags [0:15] | <ul> <li>[0] - UseIV.</li> <li>0 - The adapter will calculate a random IV and insert it into the IV field in the packet.</li> <li>1 - The DES algorithm will use the IV value contained in the packet.</li> </ul>                                                         |

|                   | [1:15] – Unused. Set to zero.                                                                                                                                                                                                                                             |

| AH1/ESP1 [0:15]   | Security Association Index for AH hdr 1 or ESP1 hdr (if no AH1).<br>If zero no hdr specified.                                                                                                                                                                             |

| ESP1 [0:15]       | Security Association Index for ESP1 hdr.<br>If zero no hdr specified.                                                                                                                                                                                                     |