## DECchip 21030 PCI Graphics Accelerator

## **Reference Manual**

Order Number: EC-N0683-72

**Revision/Update Information:** This is a new manual.

Digital Equipment Corporation Maynard, Massachusetts

#### September 1994

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1994. All Rights Reserved.

AccuLook, Alpha AXP, AXP, DEC, DECsystem, Digital, OpenVMS, RapiDraw, the DIGITAL logo, and VAX are trademarks of Digital Equipment Corporation.

Brooktree is a registered trademark and RAMDAC is trademark of Brooktree Corporation. Microsoft and Windows NT are registered trademarks and Windows is a trademark of Microsoft Corporation.

Motorola is a registered trademark of Motorola, Inc.

OpenGL is a trademark of Silicon Graphics Inc.

OSF/1 is a registered trademark of Open Software Foundation, Inc.

UNIX is a registered trademark in the United States and other countries licensed exclusively through X/Open Company Ltd.

All other trademarks and registered trademarks are the property of their respective holders.

# Contents

| P | reface . |                                    | xix  |

|---|----------|------------------------------------|------|

| 1 | Introdu  | iction                             |      |

|   | 1.1      | Overview                           | 1—1  |

|   | 1.2      | Features                           | 1–3  |

|   | 1.3      | Basic Programming Model            | 1–6  |

|   | 1.4      | Frame Buffer Configurations        | 1–8  |

| 2 | Memor    | y Space                            |      |

|   | 2.1      | Overview                           | 2–1  |

|   | 2.2      | Core Space                         | 2–1  |

|   | 2.2.1    | Frame Buffer Space                 | 2–2  |

|   | 2.2.2    | Register Space                     | 2–5  |

|   | 2.2.3    | Alternate ROM Space                | 2–9  |

|   | 2.2.3.1  | Reading Alternate ROM Space        | 2–10 |

|   | 2.2.3.2  | Writing Alternate ROM Space        | 2–11 |

| 3 | Interna  | I Architecture                     |      |

|   | 3.1      | PCI Interface                      | 3–1  |

|   | 3.1.1    | PCI Configuration Reads and Writes | 3–3  |

|   | 3.1.2    | Memory Reads and Writes            | 3–3  |

|   | 3.1.2.1  | Memory Write to Core Space         | 3–3  |

|   | 3.1.2.2  |                                    | 3–3  |

|   | 3.1.2.3  |                                    | 3–4  |

|   | 3.1.2.4  | Memory Read of Expansion ROM Space | 3–4  |

|   | 3.1.3    | DMA Transfers                      | 3–4  |

|   | 3.1.3.1  | DMA Read Transfer                  | 3–4  |

|   | 3.1.3.2  |                                    | 3–4  |

|   | 3.2      | DMA Read FIFO                      | 3–5  |

|   | 3.3      | Copy Buffer and DMA Write FIFO     | 3–5  |

| 3.4    | Command FIFO                        | 3–5  |

|--------|-------------------------------------|------|

| 3.5    | Command Parser                      | 3–6  |

| 3.5.1  | Pixel-Processing Pipeline Coherence | 3–6  |

| 3.5.2  | External Device and Register Writes | 3–6  |

| 3.5.3  | Frame Buffer Writes                 | 3–7  |

| 3.5.4  | Bresenham Setup Hardware            | 3–7  |

| 3.6    | Pixel Engine                        | 3–7  |

| 3.7    | Pixel Merge                         | 3–9  |

| 3.8    | Write Buffer                        | 3–10 |

| 3.9    | Memory Controller                   | 3–10 |

| 3.10   | CRTC and Cursor                     | 3–12 |

| 3.10.1 | Monitor Timing                      | 3–12 |

| 3.10.2 | Video Refresh                       | 3–13 |

| 3.10.3 | Cursor Generation                   | 3–13 |

| 3.11   | Frame Buffer and Device Access      | 3–13 |

| 3.12   | PCI Registers                       | 3–14 |

| 3.13   | Core Registers                      | 3–14 |

## 4 Register Descriptions

| 4.1     | Overview                                 | 4–1  |

|---------|------------------------------------------|------|

| 4.2     | PCI Registers                            | 4–2  |

| 4.2.1   | PCI Command and Status Register          | 4–4  |

| 4.2.2   | PCI Device Base Address Register         | 4–7  |

| 4.2.3   | PCI Identification Register              | 4–9  |

| 4.2.4   | PCI Class and Revision Register          | 4–10 |

| 4.2.5   | PCI Latency Timer Register               | 4–11 |

| 4.2.6   | PCI Expansion ROM Base Address Register  | 4–12 |

| 4.2.7   | PCI Line Interrupt Register              | 4–13 |

| 4.2.8   | PCI VGA Redirect Register                | 4–14 |

| 4.3     | Graphics Command Registers               | 4–15 |

| 4.3.1   | Slope Registers                          | 4–16 |

| 4.3.2   | Span Width Register                      | 4–19 |

| 4.3.2.1 |                                          | 4–19 |

| 4.3.2.2 | Read                                     | 4–19 |

| 4.3.3   | Continue Register                        | 4–21 |

| 4.3.3.1 |                                          | 4–21 |

| 4.3.3.2 |                                          | 4–22 |

| 4.3.3.3 | Read                                     | 4–23 |

| 4.3.3.4 | Writes to Alternate ROM Space            | 4–24 |

| 4.3.4   | Copy-64 Source and Destination Registers | 4–25 |

| 4.4     | Graphics Control Registers               | 4–27 |

| 4.4.1    | Mode Register                                       | 4–28 |

|----------|-----------------------------------------------------|------|

| 4.4.1.1  | Write                                               | 4–28 |

| 4.4.1.2  | Read                                                | 4–31 |

| 4.4.2    | Address Register                                    | 4–33 |

| 4.4.3    | Raster Operation Register                           | 4–35 |

| 4.4.4    | Block-Color Registers                               | 4–38 |

| 4.4.5    | Pixel-Shift Register                                | 4–41 |

| 4.4.6    | Copy-Buffer Registers                               | 4–43 |

| 4.4.7    | DMA Base-Address Register                           | 4–45 |

| 4.4.8    | Data Register                                       | 4–46 |

| 4.4.8.1  | Line Mode                                           | 4–46 |

| 4.4.8.2  | Block-Fill, Opaque-Fill, and Transparent-Fill Modes | 4–47 |

| 4.4.8.3  | DMA-Write Copy Mode                                 | 4–48 |

| 4.4.9    | Slope-No-Go Registers                               | 4–49 |

| 4.4.9.1  | Write                                               | 4–49 |

| 4.4.9.2  | Read                                                | 4–50 |

| 4.4.10   | Bresenham 1 Register                                | 4–51 |

| 4.4.11   | Bresenham 2 Register                                | 4–53 |

| 4.4.12   | Bresenham 3 Register                                | 4–54 |

| 4.4.13   | Bresenham Width Register                            | 4–55 |

| 4.4.14   | Stencil Mode Register                               | 4–56 |

| 4.4.15   | Z-Base-Address Register                             | 4–59 |

| 4.4.16   | Z-Value High and Low Registers                      | 4–60 |

| 4.4.17   | Z-Increment High and Low Registers                  | 4–62 |

| 4.4.18   | Foreground Register                                 | 4–64 |

| 4.4.19   | Background Register                                 | 4–66 |

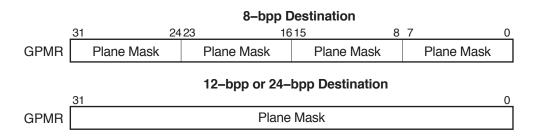

| 4.4.20   | Plane Mask Registers                                | 4–67 |

| 4.4.21   | Pixel Mask Register                                 | 4–69 |

| 4.4.21.1 | Opaque-Stipple Mode                                 | 4–69 |

| 4.4.21.2 | Simple and Simple-Z Modes                           | 4–69 |

| 4.4.21.3 | Any Mode                                            | 4–70 |

| 4.4.22   | Red-Value Register                                  | 4–71 |

| 4.4.22.1 | Color-Interpolated Line Mode                        | 4–71 |

| 4.4.22.2 | Sequential-Interpolated Line Mode                   | 4–72 |

| 4.4.23   | Red-Increment Register                              | 4–74 |

| 4.4.23.1 | Color-Interpolated Line Mode                        | 4–74 |

| 4.4.23.2 | Sequential-Interpolated Line Mode                   | 4–75 |

| 4.4.24   | Green-Value Register                                | 4–77 |

| 4.4.25   | Green-Increment Register                            | 4–78 |

| 4.4.26   | Blue-Value Register                                 | 4–79 |

| 4.4.27   | Blue-Increment Register                             | 4–80 |

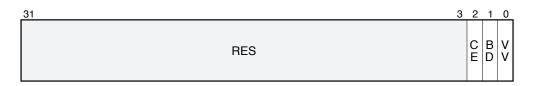

| 4.4.28   | Deep Register                                       | 4–81 |

| 4.5 Vi   | deo Timing Registers                                | 4–84 |

| 4.5.1 | Horizontal Control Register    | 4–84  |

|-------|--------------------------------|-------|

| 4.5.2 | Vertical Control Register      | 4–87  |

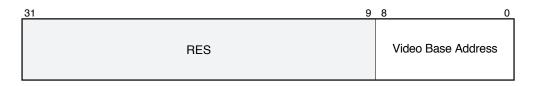

| 4.5.3 | Video Base-Address Register    | 4–89  |

| 4.5.4 | Video Valid Register           | 4–91  |

| 4.5.5 | Video Shift-Address Register   | 4–93  |

| 4.6   | Cursor Registers               | 4–94  |

| 4.6.1 | Cursor XY Register             | 4–95  |

| 4.6.2 | Cursor Base-Address Register   | 4–97  |

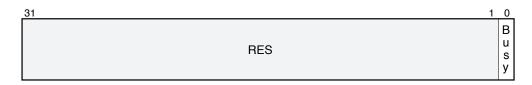

| 4.7   | Status Registers               | 4–99  |

| 4.7.1 | Command Status Register        | 4–99  |

| 4.7.2 | Interrupt Status Register      | 4–101 |

| 4.8   | External Device Registers      | 4–103 |

| 4.8.1 | EEPROM Write Register          | 4–103 |

| 4.8.2 | Palette and DAC Setup Register | 4–104 |

| 4.8.3 | Palette and DAC Data Register  | 4–106 |

| 4.8.4 | Clock Generator Register       | 4–108 |

## 5 PCI Operations

| 5.1   | Configuration Operations            | 5–1 |

|-------|-------------------------------------|-----|

| 5.2   | Target Operations                   | 5–1 |

| 5.2.1 | Access Granularity                  | 5–2 |

| 5.2.2 | Transaction Termination             | 5–2 |

| 5.3   | Master Operation                    | 5–3 |

| 5.3.1 | Transaction Termination             | 5–3 |

| 5.3.2 | Aborted DMA Transaction Termination | 5–4 |

| 5.4   | Parity                              | 5–4 |

| 5.5   | Address and Data Stepping           | 5–4 |

| 5.6   | Bus Parking                         | 5–5 |

| 5.7   | Functions Not Supported             | 5–5 |

## 6 Graphics Operations

| 6.1     | Overview                            | 6–1  |

|---------|-------------------------------------|------|

| 6.1.1   | Frame Buffer Writes                 | 6–1  |

| 6.1.2   | Graphics Command Register Writes    | 6–2  |

| 6.1.3   | Invoking Graphics Operations        | 6–4  |

| 6.1.4   | Register Load Synchronization       | 6–5  |

| 6.1.5   | Visual Bitmap and Buffer Formats    | 6–6  |

| 6.1.5.1 | 8-bpp Frame Buffer                  | 6–6  |

| 6.1.5.2 | 32-bpp Frame Buffer                 | 6–7  |

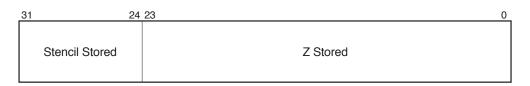

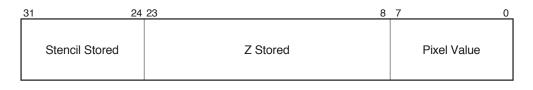

| 6.1.5.3 | Z-Buffer and Stencil-Buffer Formats | 6–10 |

| 6.1.6    | Source and Destination Operands                  | 6–11 |

|----------|--------------------------------------------------|------|

| 6.1.6.1  | Address Alignment Requirements                   | 6–13 |

| 6.1.6.2  | 24-bpp Bitmap Operands                           | 6–13 |

| 6.1.6.3  | 12-bpp Bitmap Operands                           | 6–14 |

| 6.1.6.4  | 8-bpp Bitmap Operands                            | 6–15 |

| 6.2      | Graphics Modes                                   | 6–18 |

| 6.2.1    | Simple Mode                                      | 6–19 |

| 6.2.2    | Simple-Z Mode                                    | 6–21 |

| 6.2.3    | Opaque-Stipple Mode                              | 6–25 |

| 6.2.4    | Transparent-Stipple Mode                         | 6–28 |

| 6.2.5    | Block-Stipple Mode                               | 6–30 |

| 6.2.5.1  | Frame Buffer Address Alignment                   | 6–34 |

| 6.2.5.2  | Stipple Mask Alignment                           | 6–35 |

| 6.2.5.3  | Block Color Pattern Alignment                    | 6–35 |

| 6.2.5.4  | Using Block Stipple Mode                         | 6–35 |

| 6.2.6    | Block-Fill Mode                                  | 6–37 |

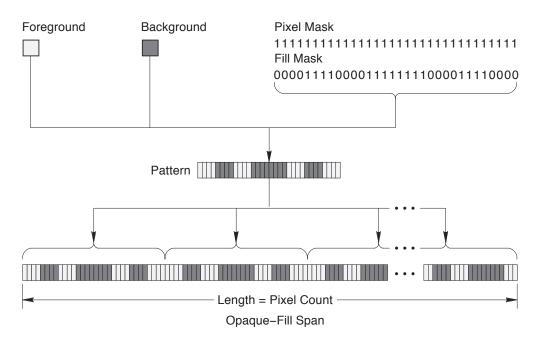

| 6.2.7    | Opaque-Fill Mode                                 | 6–41 |

| 6.2.8    | Transparent-Fill Mode                            | 6–44 |

| 6.2.9    | Copy Mode                                        | 6–45 |

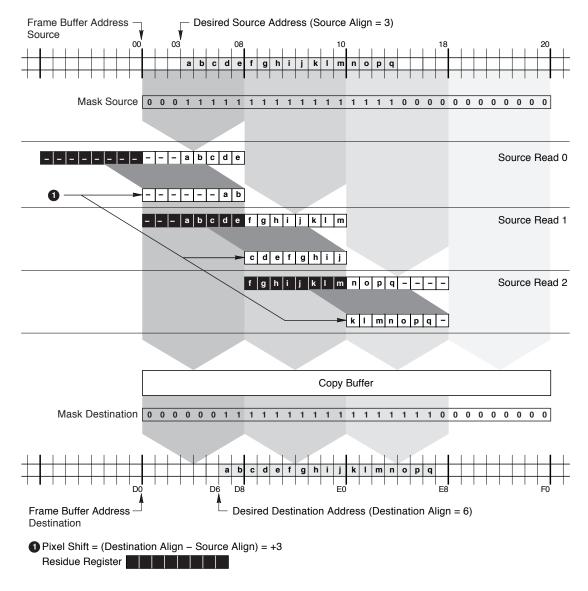

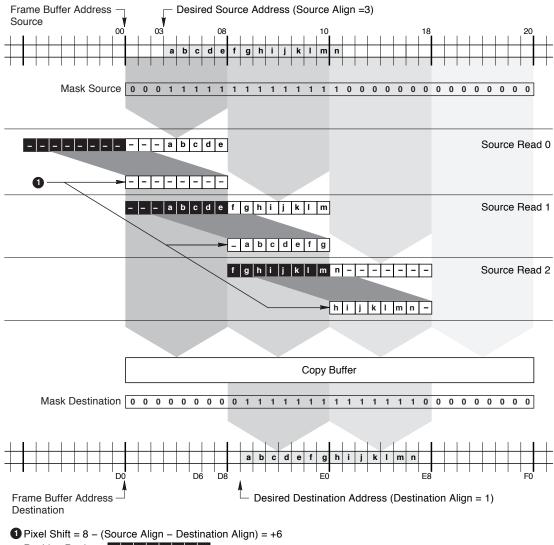

| 6.2.9.1  | Source and Destination Alignment                 | 6–48 |

| 6.2.9.2  | Backward Copies                                  | 6–52 |

| 6.2.9.3  | Priming and Flushing the Residue Register        | 6–53 |

| 6.2.9.4  | Copy Direction Flag                              | 6–55 |

| 6.2.9.5  | 64-Byte Unmasked Span Copies                     | 6–56 |

| 6.2.9.6  | Copy Buffer Operation                            | 6–56 |

| 6.2.9.7  | Fast Frame Buffer Access Using the Copy Buffer   |      |

|          | Registers                                        | 6–59 |

| 6.2.9.8  | Copy Mode Source and Destination Bitmaps         | 6–60 |

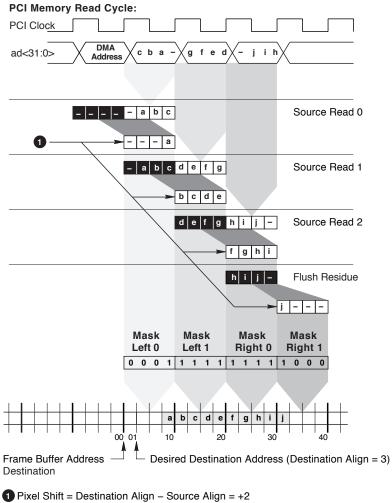

| 6.2.10   | DMA-Read Copy Mode                               | 6–63 |

| 6.2.10.1 | Priming and Flushing the Residue Register        | 6–66 |

| 6.2.10.2 | Bitmap Formats Supported in DMA-Read Copy Mode   | 6–69 |

| 6.2.10.3 | Dithering in DMA-Read Copy Mode                  | 6–69 |

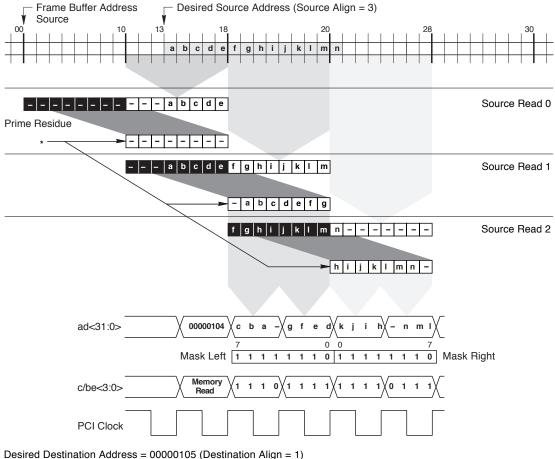

| 6.2.11   | DMA-Write Copy Mode                              | 6–70 |

| 6.2.11.1 | Priming and Flushing the Residue Register        | 6–74 |

| 6.2.11.2 |                                                  | 6–76 |

| 6.2.12   | Opaque-Line Mode                                 | 6–77 |

| 6.2.12.1 | Drawing Lines with the Slope Registers           | 6–80 |

| 6.2.12.2 | 2 Destination Bitmap Support in Opaque-Line Mode | 6–83 |

| 6.2.12.3 |                                                  | 6–83 |

| 6.2.13   | Transparent-Line Mode                            | 6–88 |

| 6.2.14   | 3D Line and Span Modes                | 6–89  |

|----------|---------------------------------------|-------|

| 6.2.14.1 | Color Interpolation                   | 6–92  |

| 6.2.14.2 | Sequential Interpolation              | 6–95  |

| 6.2.14.3 | Z-Buffer and Stencil-Buffer Operation | 6–96  |

| 6.2.14.4 | Extending and Linking 3D Lines        | 6–101 |

|          |                                       |       |

## 7 Programming Guide

| 7.1 PCI ( | Configuration Firmware                        | 7–1  |

|-----------|-----------------------------------------------|------|

| 7.1.1 D   | Device Address Mapping                        | 7–1  |

|           | Bus Mastering                                 | 7–2  |

|           | nterrupt Routing                              | 7–3  |

| 7.1.4 V   | GA Pass-Through                               | 7–3  |

| 7.1.5 E   | Expansion ROM                                 | 7–4  |

| 7.2 Grap  | hics Drivers and Servers                      | 7–4  |

| 7.2.1 B   | Bit-Block Transfers                           | 7–4  |

| 7.2.1.1   | Screen-to-Screen Copy                         | 7–4  |

| 7.2.1.2   | Host-to-Screen Copy                           | 7–7  |

| 7.2.2 F   | 'ills                                         | 7–7  |

| 7.2.2.1   | Solid                                         | 7–7  |

| 7.2.2.2   | Stippling or Filling with a Monochrome Brush  | 7–8  |

| 7.2.2.3   | Tiling or Filling with a Non-Monochrome Brush | 7–9  |

| 7.2.3 2   | D Lines                                       | 7–10 |

| 7.2.3.1   | Line Drawing Under X                          | 7–10 |

| 7.2.3.2   | Line Drawing Under Win32                      | 7–12 |

| 7.2.3.3   | 21030 Turbo Lines                             | 7–14 |

| 7.2.4 T   | ext                                           | 7–15 |

| 7.2.5 3   | D Lines                                       | 7–16 |

| 7.2.5.1   | Software Z-Buffering                          | 7–19 |

| 7.2.6 3   | D Polygons                                    | 7–19 |

|           | nimations                                     | 7–19 |

| 7.2.7.1   | Offscreen-Copy Double-Buffering               | 7–19 |

| 7.2.7.2   | In-Place Double-Buffering                     | 7–20 |

| 7.2.8 C   | Cursor Display                                | 7–21 |

| 7.3 Progr | ramming for Alpha AXP CPUs                    | 7–21 |

| 7.3.1 P   | rogrammed I/O Through the CPU Write Buffer    | 7–21 |

| 7.3.2 A   | ddress and Continue Register Access           | 7–23 |

|           | -                                             |      |

### 8 Hardware Interface

| 8.1 Frame  | Buffer Organization                                 | 8–1  |

|------------|-----------------------------------------------------|------|

|            | Plane Frame Buffer                                  | 8–1  |

| 8.1.2 32   | -Plane Frame Buffer                                 | 8–4  |

| 8.1.2.1    | Horizontal Access Mode                              | 8–4  |

| 8.1.2.2    | Broadcast Access Mode                               | 8–4  |

| 8.1.2.3    | Diagonal Access Mode                                | 8–4  |

| 8.1.3 Su   | pported Memory Devices                              | 8–7  |

| 8.2 System | n Configurations with VGA                           | 8–8  |

| 8.3 Extern | nal Device Interfaces                               | 8–8  |

|            | Descriptions                                        | 8–8  |

| 8.4.1 Fra  | ame Buffer Interface Signals                        | 8–9  |

| 8.4.1.1    | addr<17:0>                                          | 8–9  |

| 8.4.1.2    | addren_l<1:0>                                       | 8–9  |

| 8.4.1.3    | $cas_l < 3:0$ >, $casen < 1:0$ >, $casmode < 1:0$ > | 8–9  |

| 8.4.1.4    | dacc<2:0>, dacce_l<1:0>, dacrw                      | 8–9  |

| 8.4.1.5    | data<63:0>                                          | 8–10 |

| 8.4.1.6    | dsf<1:0>                                            | 8–10 |

| 8.4.1.7    | fbclk                                               | 8–10 |

| 8.4.1.8    | icsce_l                                             | 8–10 |

| 8.4.1.9    | oe_l<1:0>                                           | 8–10 |

| 8.4.1.10   | ras_l<3:0>, rasen_l<3:0>                            | 8–11 |

| 8.4.1.11   | romce_l, romoe_l, romwe_l                           | 8–11 |

| 8.4.1.12   | we_l<7:0>                                           | 8–11 |

| 8.4.2 PC   | CI Signals                                          | 8–11 |

| 8.4.2.1    | ad<31:0>                                            | 8–11 |

| 8.4.2.2    | cbe_l<3:0>                                          | 8–11 |

| 8.4.2.3    | devsel_l                                            | 8–12 |

| 8.4.2.4    | frame_l                                             | 8–12 |

| 8.4.2.5    | gnt_l                                               | 8–12 |

| 8.4.2.6    | idsel                                               | 8–12 |

| 8.4.2.7    | inta_l                                              | 8–12 |

| 8.4.2.8    | irdy_l                                              | 8–12 |

| 8.4.2.9    | par                                                 | 8–13 |

| 8.4.2.10   | pciclk                                              | 8–13 |

| 8.4.2.11   | req_1                                               | 8–13 |

| 8.4.2.12   | rst_l                                               | 8–13 |

| 8.4.2.13   | stop_l                                              | 8–13 |

| 8.4.2.14   | trdy_l                                              | 8–13 |

|            |                                                     |      |

| 8.4.3   | Video Interface Signals | 8–13 |

|---------|-------------------------|------|

| 8.4.3.1 | blank_l                 | 8–14 |

| 8.4.3.2 | cursor<7:0>             | 8–14 |

| 8.4.3.3 | hsync_l                 | 8–14 |

| 8.4.3.4 | hold_l                  | 8–14 |

| 8.4.3.5 | toggle                  | 8–14 |

| 8.4.3.6 | vidclk                  | 8–14 |

| 8.4.3.7 | vsync_l                 | 8–14 |

| 8.4.4   | Test Signals            | 8–15 |

| 8.4.4.1 | testin_l                | 8–15 |

| 8.4.4.2 | toggle                  | 8–15 |

## A DECchip 21030 step A Differences

| A.1     | Memory Space                         | A–1 |

|---------|--------------------------------------|-----|

| A.1.1   | Extending 21030 step A Memory Space  | A–2 |

| A.2     | PCI Registers                        | A–4 |

| A.2.1   | PCI Device Base Address Register     | A–4 |

| A.2.2   | PCI Address Extension Register       | A–6 |

| A.3     | Video Timing Registers               | A–7 |

| A.4     | PCI Operations                       | A–7 |

| A.4.1   | Access Granularity                   | A–7 |

| A.4.2   | Device Address Mapping               | A–7 |

| A.4.2.1 | Address Mapping in Alpha AXP Systems | A–8 |

## **B** Pin Summary

## C Register Summary

## D Technical Support, Ordering, and Associated Literature

## Glossary

## Index

## Figures

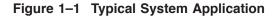

| 1–1  | Typical System Application              | 1–2  |

|------|-----------------------------------------|------|

| 1–2  | Typical 8-bpp Configuration             | 1–10 |

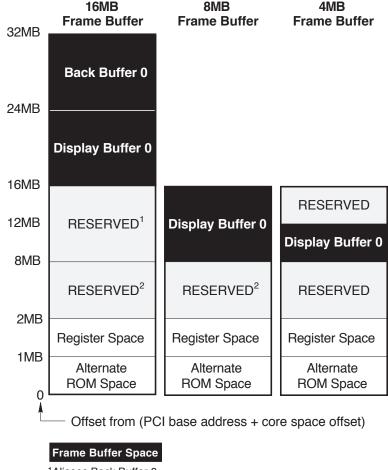

| 2–1  | 21030 step B Memory Space Organization  | 2–3  |

| 2–2  | Core Space Map for 8-bpp Frame Buffers  | 2–4  |

| 2–3  | Core Space Map for 32-bpp Frame Buffers | 2–5  |

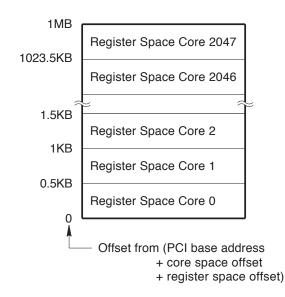

| 2–4  | Register Space Organization             | 2–6  |

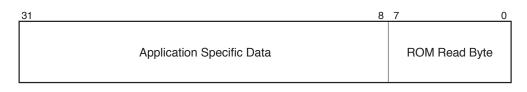

| 2–5  | Alternate ROM Space Read Format         | 2–10 |

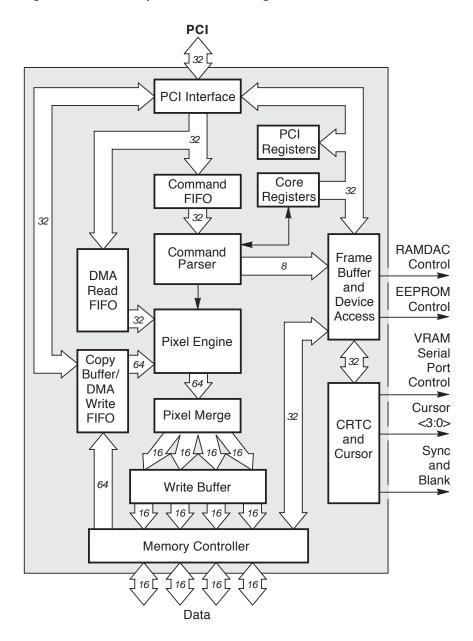

| 3–1  | DECchip 21030 Block Diagram             | 3–2  |

| 4–1  | PCSR Format                             | 4–4  |

| 4–2  | PDBR Format                             | 4–7  |

| 4–3  | PIDR Format                             | 4–9  |

| 4–4  | PCRR Format                             | 4–10 |

| 4–5  | PLTR Format                             | 4–11 |

| 4–6  | PRBR Format                             | 4–12 |

| 4–7  | PLIR Format                             | 4–13 |

| 4–8  | PVRR Format                             | 4–14 |

| 4–9  | GSLR<7:0> Format                        | 4–16 |

| 4–10 | Slope Registers and Drawing Octants     | 4–17 |

| 4–11 | GSWR Read Format                        | 4–19 |

| 4–12 | GCTR Write Format                       | 4–21 |

| 4–13 | GCTR Line-Mode Write Format             | 4–22 |

| 4–14 | GCTR Read Format                        | 4–23 |

| 4–15 | GCSR and GCDR Formats                   | 4–25 |

| 4–16 | GMOR Write Format                       | 4–28 |

| 4–17 | GMOR Read Format                        | 4–31 |

| 4–18 | GADR Format                             | 4–33 |

| 4–19 | GOPR Format                             | 4–35 |

| 4–20 | GBCR<7:0> Format                        | 4–38 |

| 4–21 | GBCR Color Pattern Formats              | 4–40 |

| 4–22 | GPSR Format                             | 4–41 |

| 4–23 | GCBR<7:0> Format                        | 4–43 |

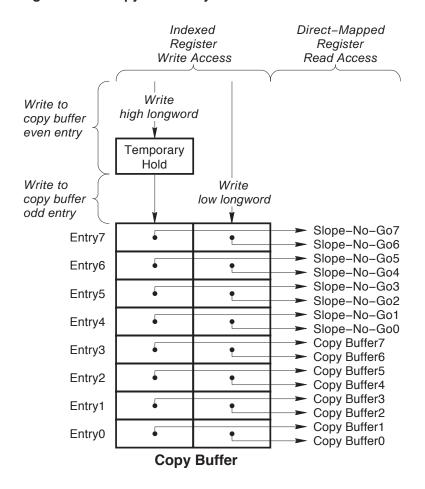

| 4–24 | Copy Buffer Layout                      | 4–44 |

| 4–25 | GDBR Format                             | 4–45 |

| 4–26 | GDAR Line-Mode Format                   | 4–46 |

| 4–27 | GDAR Fill-Mode Format                   | 4–47 |

| 4–28 | GDAR DMA-Write Copy Mode Format                   | 4–48  |

|------|---------------------------------------------------|-------|

| 4–29 | GSNR<7:0> Write Format                            | 4–49  |

| 4–30 | GSNR<7:0> Read Format                             | 4–50  |

| 4–31 | GB1R Format                                       | 4–51  |

| 4–32 | GB2R Format                                       | 4–53  |

| 4–33 | GB3R Format                                       | 4–54  |

| 4–34 | GBWR Format                                       | 4–55  |

| 4–35 | GSMR Format                                       | 4–56  |

| 4–36 | GZBR Format                                       | 4–59  |

| 4–37 | GZVR-H and GZVR-L Formats                         | 4–60  |

| 4–38 | GZIR-H AND GZIR-L Formats                         | 4–62  |

| 4–39 | GFGR Format                                       | 4–64  |

| 4–40 | Foreground and Background as a Function of Bitmap |       |

|      | Depth                                             | 4–65  |

| 4–41 | GBGR Format                                       | 4–66  |

| 4–42 | GPMR Format                                       | 4–67  |

| 4–43 | Plane Mask Formats                                | 4–68  |

| 4–44 | GPXR Opaque-Stipple Mode Format                   | 4–69  |

| 4–45 | GPXR Simple and Simple-Z Modes Format             | 4–70  |

| 4–46 | GRVR Color-Interpolated Line-Mode Format          | 4–71  |

| 4–47 | GRVR Sequential-Interpolated Line-Mode Format     | 4–72  |

| 4–48 | GRIR Color-Interpolated Line-Mode Format          | 4–74  |

| 4–49 | GRIR Sequential-Interpolated Line-Mode Format     | 4–75  |

| 4–50 | GGVR Format                                       | 4–77  |

| 4–51 | GGIR Format                                       | 4–78  |

| 4–52 | GBVR Format                                       | 4–79  |

| 4–53 | GBIR Format                                       | 4–80  |

| 4–54 | GDER Format                                       | 4–81  |

| 4–55 | VHCR Format                                       | 4–84  |

| 4–56 | VVCR Format                                       | 4–87  |

| 4–57 | VVBR Format                                       | 4–89  |

| 4–58 | VVVR Format                                       | 4–91  |

| 4–59 | VSAR Format                                       | 4–93  |

| 4–60 | CXYR Format                                       | 4–95  |

| 4–61 | CCBR Format                                       | 4–97  |

| 4–62 | SCSR Format                                       | 4–99  |

| 4–63 | SISR Format                                       | 4–101 |

| 4–64 | ERWR Format                                     | 4–103 |

|------|-------------------------------------------------|-------|

| 4–65 | EPSR Format                                     | 4–104 |

| 4–66 | EPDR Read Format                                | 4–106 |

| 4–67 | EPDR Write Format                               | 4–107 |

| 4–68 | ECGR Format                                     | 4–108 |

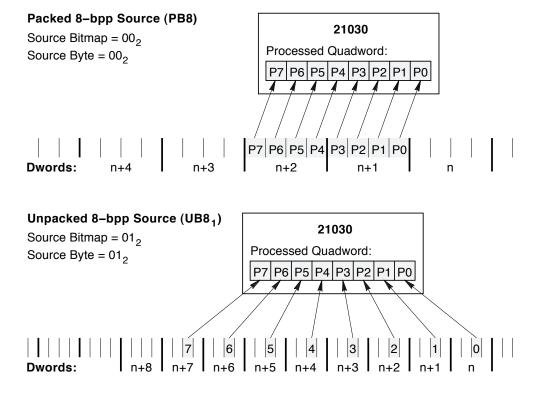

| 6–1  | Packed 8-bpp Bitmap                             | 6–7   |

| 6–2  | 8-bpp Unpacked Bitmap Formats                   | 6–8   |

| 6–3  | 12-bpp Bitmap Formats                           | 6–9   |

| 6–4  | 24-bpp True-Color Bitmap Format                 | 6–9   |

| 6–5  | Z24 Z and Stencil Buffer Format                 | 6–11  |

| 6–6  | Z16 Z and Stencil Buffer Format                 | 6–11  |

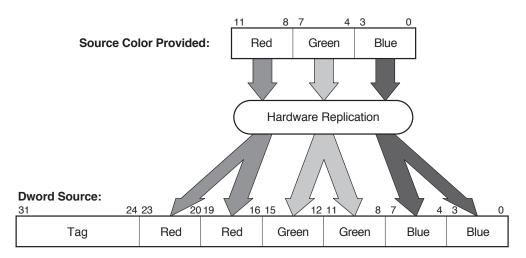

| 6–7  | Hardware Replication of 12-bpp Source Bitmap to |       |

|      | Destination Dword                               | 6–14  |

| 6–8  | 8-bpp Bitmap Access in 32-bpp Frame Buffers     | 6–16  |

| 6–9  | Simple Mode PCI Write-Data Format               | 6–19  |

| 6–10 | Simple-Z Mode PCI Write-Data Format             | 6–22  |

| 6–11 | Opaque-Stipple Mode PCI Write-Data Format       | 6–25  |

| 6–12 | Opaque-Stipple Mode Operation                   | 6–27  |

| 6–13 | Transparent-Stipple Mode PCI Write-Data Format  | 6–28  |

| 6–14 | Transparent-Stipple Mode Operation              | 6–29  |

| 6–15 | Block-Stipple Mode PCI Write-Data Format        | 6–30  |

| 6–16 | Block-Stipple Mode Operation                    | 6–31  |

| 6–17 | Block-Stipple Mode Address and Mask Alignment   | 6–33  |

| 6–18 | Block-Fill Mode PCI Write-Data Format           | 6–37  |

| 6–19 | Block-Fill Mode Operation                       | 6–40  |

| 6–20 | Opaque-Fill Mode PCI Write-Data Format          | 6–41  |

| 6–21 | Opaque-Fill Mode Operation                      | 6–43  |

| 6–22 | Copy Mode PCI Write Data Formats                | 6–46  |

| 6–23 | Forward Span Copy                               | 6–51  |

| 6–24 | Primed Forward Span Copy                        | 6–54  |

| 6–25 | Copy Buffer Layout                              | 6–58  |

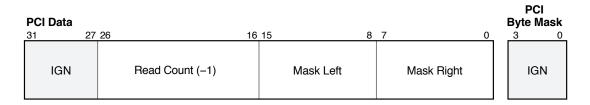

| 6–26 | DMA-Read Copy-Mode PCI Write-Data Format        | 6–64  |

| 6–27 | DMA-Read Copy                                   | 6–68  |

| 6–28 | DMA-Write Copy-Mode PCI Write-Data Format       | 6–71  |

| 6–29 | DMA-Write Copy                                  | 6–75  |

| 6–30 | Opaque-Line Mode PCI Write-Data Format          | 6–78  |

| 6–31 | Opaque Line Drawing                             | 6–83  |

| 6–32 | Opaque-Line Drawing Sequence                          | 6–86  |

|------|-------------------------------------------------------|-------|

| 6–33 | Color Interpolator Output for a 24-bpp Destination    | 6–93  |

| 6–34 | Color Interpolators Output for 12-bpp and 8-bpp       |       |

|      | Destinations                                          | 6–95  |

| 6–35 | Z-Buffered, Color-Interpolated Line Segment           | 6–100 |

| 7–1  | BitBlt Using Copy Mode Example                        | 7–6   |

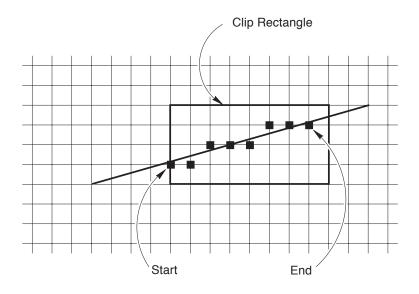

| 7–2  | Drawing Clipped Lines                                 | 7–12  |

| 8–1  | Frame Buffer Option T8-01                             | 8–2   |

| 8–2  | Frame Buffer Option T8-02                             | 8–2   |

| 8–3  | Frame Buffer Option T8-22                             | 8–3   |

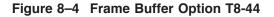

| 8–4  | Frame Buffer Option T8-44                             | 8–3   |

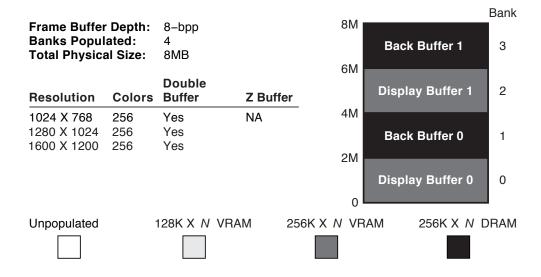

| 8–5  | Frame Buffer Option T32-04                            | 8–5   |

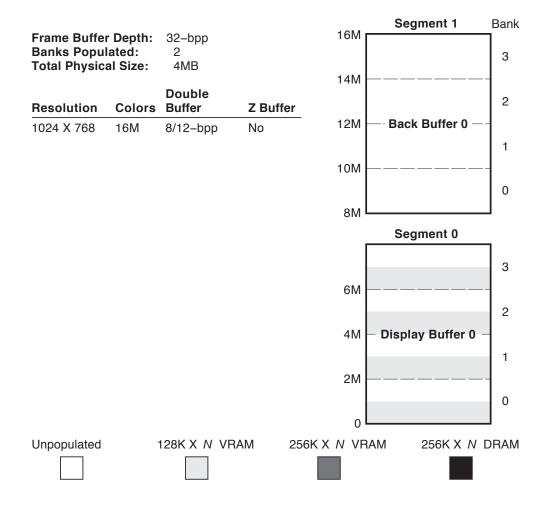

| 8–6  | Frame Buffer Option T32-08                            | 8–6   |

| 8–7  | Frame Buffer Option T32-88                            | 8–6   |

| A–1  | Memory Space Organization                             | A–1   |

| A–2  | Extended 21030 step A Core Space Map for 32-bpp Frame |       |

|      | Buffers                                               | A–3   |

| A–3  | PDBR Format                                           | A-4   |

| A4   | PAER Format                                           | A–6   |

|      |                                                       |       |

## Tables

| 1–1  | Typical Applicable Systems                 | 1–3  |

|------|--------------------------------------------|------|

| 1–2  | Supported Frame Buffer Configurations      | 1–9  |

| 2–1  | Frame Buffer Configuration and Core Space  | 2–2  |

| 2–2  | Core Registers                             | 2–7  |

| 2–3  | Alternate ROM Space Read Field Description | 2–10 |

| 4–1  | 21030 PCI Configuration Space              | 4–3  |

| 4–2  | PCSR Field Description                     | 4–4  |

| 4–3  | PDBR Field Description                     | 4–7  |

| 4–4  | PIDR Field Description                     | 4–9  |

| 4–5  | PCRR Field Description                     | 4–10 |

| 4–6  | PLTR Field Description                     | 4–11 |

| 4–7  | PRBR Field Description                     | 4–12 |

| 4–8  | PLIR Field Description                     | 4–13 |

| 4–9  | PVRR Field Description                     | 4–14 |

| 4–10 | GSLR<7:0> Field Description                | 4–16 |

| 4–11 | GSWR Read-Format Field Description                | 4–19 |

|------|---------------------------------------------------|------|

| 4–12 | GCTR Write-Format Field Description               | 4–21 |

| 4–13 | GCTR Line-Mode Write-Format Field Description     | 4–22 |

| 4–14 | GCTR Read-Format Field Description                | 4–23 |

| 4–15 | GCSR and GCDR Field Description                   | 4–25 |

| 4–16 | GMOR Write-Format Field Description               | 4–28 |

| 4–17 | Graphics Modes                                    | 4–29 |

| 4–18 | GMOR Read-Format Field Description                | 4–31 |

| 4–19 | GADR Field Description                            | 4–33 |

| 4–20 | GOPR Field Description                            | 4–35 |

| 4–21 | Boolean Raster Operations                         | 4–36 |

| 4–22 | GBCR<7:0> Field Description                       | 4–38 |

| 4–23 | GPSR Field Description                            | 4–41 |

| 4–24 | GDBR Field Description                            | 4–45 |

| 4–25 | GDAR Line-Mode Format Field Description           | 4–46 |

| 4–26 | GDAR Fill-Mode Format Field Description           | 4–47 |

| 4–27 | GDAR DMA-Write Copy Mode Format Field Description | 4–48 |

| 4–28 | GSNR<7:0> Write-Format Field Description          | 4–49 |

| 4–29 | GSNR<7:0> Read Format Contents                    | 4–50 |

| 4–30 | GB1R Field Description                            | 4–51 |

| 4–31 | GB2R Field Description                            | 4–53 |

| 4–32 | GB3R Field Description                            | 4–54 |

| 4–33 | GBWR Field Description                            | 4–55 |

| 4–34 | GSMR Field Description                            | 4–56 |

| 4–35 | GSMR Pass and Fail Fields Codes                   | 4–57 |

| 4–36 | GSMR Test Fields Codes                            | 4–57 |

| 4–37 | Stencil Buffer Update Conditions                  | 4–58 |

| 4–38 | GZBR Field Description                            | 4–59 |

| 4–39 | GZVR-H and GZVR-L Field Description               | 4–60 |

| 4–40 | GZIR-H and GZIR-L Field Description               | 4–62 |

| 4–41 | GFGR Field Description                            | 4–64 |

| 4–42 | GBGR Field Description                            | 4–66 |

| 4–43 | GPMR Field Description                            | 4–67 |

| 4–44 | GPXR Opaque-Stipple Mode Format Field Description | 4–69 |

| 4–45 | GPXR Simple and Simple-Z Modes Field Description  | 4–70 |

| 4–46 | GRVR Color-Interpolated Line-Mode Format Field    |      |

|      | Description                                       | 4–71 |

|      |                                                   |      |

| 4–47 | GRVR Sequential-Interpolated Line-Mode Format Field Description | 4–72  |

|------|-----------------------------------------------------------------|-------|

| 4–48 | GRIR Color-Interpolated Line-Mode Format Field                  |       |

|      | Description                                                     | 4–74  |

| 4–49 | GRIR Sequential-Interpolated Line-Mode Format Field             |       |

|      | Description                                                     | 4–75  |

| 4–50 | GGVR Field Description                                          | 4–77  |

| 4–51 | GGIR Field Description                                          | 4–78  |

| 4–52 | GBVR Field Description                                          | 4–79  |

| 4–53 | GBIR Field Description                                          | 4–80  |

| 4–54 | GDER Field Description                                          | 4–81  |

| 4–55 | VHCR Field Description                                          | 4–84  |

| 4–56 | VVCR Field Description                                          | 4–87  |

| 4–57 | VVBR Field Description                                          | 4–89  |

| 4–58 | Video Base-Address Alignment According to VRAM Size             | 4–89  |

| 4–59 | VVVR Field Description                                          | 4–91  |

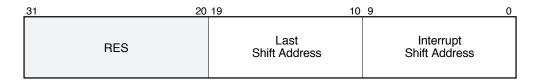

| 4–60 | VSAR Field Description                                          | 4–93  |

| 4–61 | Interrupt Shift-Address to Frame Buffer Byte-Address            |       |

|      | Map                                                             | 4–94  |

| 4–62 | CXYR Field Description                                          | 4–95  |

| 4–63 | Cursor Coordinate Limits                                        | 4–95  |

| 4–64 | CCBR Field Description                                          | 4–97  |

| 4–65 | SCSR Field Description                                          | 4–99  |

| 4–66 | SISR Field Description                                          | 4–101 |

| 4–67 | ERWR Field Description                                          | 4–103 |

| 4–68 | EPSR Field Description                                          | 4–104 |

| 4–69 | EPSR MPU Control Field Mapping                                  | 4–105 |

| 4–70 | EPDR Read-Format Field Description                              | 4–106 |

| 4–71 | EPDR Write-Format Field Description                             | 4–107 |

| 4–72 | ECGR Field Description                                          | 4–108 |

| 6–1  | Mode-Dependent Frame Buffer Write Operations                    | 6–1   |

| 6–2  | Graphics Command Register Write Operations                      | 6–3   |

| 6–3  | Graphics Command Register Write Operations in 3D Line           |       |

|      | Modes                                                           | 6–3   |

| 6–4  | 32-bpp Frame Buffer Supported Bitmaps                           | 6–7   |

| 6–5  | Source and Destination Operands According to Mode               | 6–12  |

| 6–6  | Unsupported Bitmap Formats According to Mode                    | 6–12  |

| 6–7  | Source, Destination, and Plane Mask Fields                      | 6–13  |

| 6–8  | 8-bpp Source and Destination Bitmap and Byte Field Values | 6–17 |

|------|-----------------------------------------------------------|------|

| 6–9  | Simple Mode Parameters                                    | 6–19 |

| 6–10 | Simple-Z Mode Parameters                                  | 6–21 |

| 6–11 | Opaque-Stipple Mode Parameters                            | 6–25 |

| 6–12 | Transparent-Stipple Mode Parameters                       | 6–28 |

| 6–13 | Block-Stipple Mode Parameters                             | 6–30 |

| 6–14 | Block-Fill Mode Parameters                                | 6–37 |

| 6–15 | Opaque-Fill Mode Parameters                               | 6–41 |

| 6–16 | Transparent-Fill Mode Parameters                          | 6–44 |

| 6–17 | Copy Mode Parameters                                      | 6–45 |

| 6–18 | Copy Mode Span Limits                                     | 6–47 |

| 6–19 | Assigning the Pixel Shift Value                           | 6–52 |

| 6–20 | Format Parameters for 12-bpp Bitmaps                      | 6–61 |

| 6–21 | Format Parameters for 8-bpp Bitmaps in a 32-bpp Frame     |      |

|      | Buffer                                                    | 6–62 |

| 6–22 | DMA-Read Copy-Mode Parameters                             | 6–63 |

| 6–23 | Edge Mask Settings in DMA-Read Copy Mode                  | 6–67 |

| 6–24 | Edge Mask for Short Spans in DMA-Read Copy Mode           | 6–67 |

| 6–25 | DMA-Write Copy-Mode Parameters                            | 6–70 |

| 6–26 | Edge Mask for Short Spans in DMA-Write Copy Mode          | 6–74 |

| 6–27 | Opaque-Line Mode Parameters                               | 6–77 |

| 6–28 | Opaque-Line Mode Parameters Using Slope Registers         | 6–80 |

| 6–29 | Transparent-Line Mode Parameters                          | 6–88 |

| 6–30 | 3D Line Mode Parameters                                   | 6–90 |

| 6–31 | Reduced Color Interpolator Output for 8-bpp and 12-bpp    |      |

|      | Destinations                                              | 6–94 |

| 7–1  | 21030 Base Address and Memory Space Enable Fields         | 7–1  |

| 7–2  | PCI Latency Timer and Master Enable Fields                | 7–2  |

| 7–3  | VGA Redirect Register Fields                              | 7–3  |

| 8–1  | RAMDAC MPU Interface Connection                           | 8–10 |

| A–1  | PDBR Field Description                                    | A-4  |

| A–2  | PAER Field Description                                    | A–6  |

| A–3  | 21030 Base Address and Memory Space Enable Fields         | A–8  |

| A–4  | PCI Address Space Requirements in Alpha AXP Systems       | A–9  |

| B–1  | Frame Buffer Interface Pin Summary                        | B–1  |

| B–2  | PCI Interface Pin Summary                                 | B–2  |

| B–3 | Video Interface Pin Summary       | B–3 |

|-----|-----------------------------------|-----|

| B–4 | Test Pin Summary                  | B–3 |

| C–1 | PCI Configuration Registers       | C–1 |

| C–2 | Graphics Command Register Summary | C–2 |

| C–3 | Graphics Control Register Summary | C–3 |

| C–4 | Video Timing Register Summary     | C–5 |

| C–5 | Cursor Control Register Summary   | C–5 |

| C–6 | Status Register Summary           | C–5 |

| C–7 | External Device Register Summary  | C–6 |

|     |                                   |     |

## Preface

This manual describes the architecture, internal design, and external interface of the DECchip 21030 PCI Graphics Accelerator. It includes register descriptions, an overview of the chip's microarchitecture, descriptions of the the graphics processing algorithms, and programming information.

Note

The DECchip 21030 step A and DECchip 21030 step B are nearly identical. Differences between the two are noted as they occur in this manual, and the description "defaults" to functionality that is specific to the 21030 step B; the equivalent 21030 step A functionality is described in Appendix A.

### Audience

This manual is for system designers, software developers, and hardware engineers who use the DECchip 21030 PCI Graphics Accelerator.

## **Manual Organization**

This manual contains the following chapters and appendices as well as a glossary and an index.

- Chapter 1, Introduction

- Chapter 2, Memory Space

- Chapter 3, Internal Architecture

- Chapter 4, Register Descriptions

- Chapter 5, PCI Operations

- Chapter 6, Graphics Operations

- Chapter 7, Programming Guide

- Chapter 8, Hardware Interface

- Appendix A, DECchip 21030 step A Differences

- Appendix B, Pin Summary

- Appendix C, Register Summary

- Appendix D, Technical Support, Ordering, and Associated Literature

- Glossary

- Index

#### Conventions

The following conventions are used throughout this manual.

#### Abbreviations

• bpp

The terms "bits per pixel" and "bits/pixel" are abbreviated as bpp.

#### • Binary Multiples

The abbreviations K, M, and G (Kilo, Mega, and Giga) represent binary multiples and have the following values.

$\begin{array}{ll} K = & 2^{10} \ (1024) \\ M = & 2^{20} \ (1,048,576) \\ G = & 2^{30} \ (1,073,741,824) \end{array}$

For example:

| 2KB =       | 2 Kilobytes =  | $2 \times 2^{10}$ bytes  |

|-------------|----------------|--------------------------|

| 4MB =       | 4 Megabytes =  | $4 \times 2^{20}$ bytes  |

| 8GB =       | 8 Gigabytes =  | $8 \times 2^{30}$ bytes  |

| 2K pixels = | 2 Kilopixels = | $2 \times 2^{10}$ pixels |

| 4M pixels = | 4 Megapixels = | $4 \times 2^{20}$ pixels |

#### • Register Access

The abbreviations used to indicate the type of access to register fields and bits have the following definitions:

#### IGN — Ignore

Bits and fields specified as IGN are ignored when written.

#### RAZ — Read As Zero

Bits and fields specified as RAZ return a zero when read.

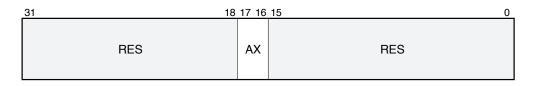

#### **RES** — **Reserved**

Bits and fields specified as RES are reserved by Digital and should not be used.

#### **RO** – Read Only

Bits and fields specified as RO can be read and are ignored (not written) on writes.

#### RW — Read/Write

Bits and fields specified as RW can be read and written.

#### **R/W1C** — **Read/Write** One to Clear

Bits and fields specified as R/W1C can be read. Writing a one clears the bits.

#### WO — Write Only

Bits and fields specified as WO can be written but not read.

#### Aligned and Unaligned

The terms *aligned* and *naturally aligned* are interchangeable and refer to data objects that are powers of two in size. An aligned datum of size  $2^n$  is stored in memory at a byte address that is a multiple of  $2^n$ ; that is, one that has *n* low-order zeros. For example, an aligned 64-byte stack frame has a memory address that is a multiple of 64.

A datum of size  $2^n$  is *unaligned* if it is stored in a byte address that is not a multiple of  $2^n$ .

#### **Bit Notation**

Multiple bit fields are shown as extents (see Ranges and Extents, below).

#### Caution

Cautions indicate potential damage to equipment or loss of data.

#### Core, Core Space, and Core Registers

This manual frequently refers to the 21030 core, core space, and core registers.

- The 21030 core is all of the chip functions except the PCI interface and PCI registers.

- The 21030 memory space consists of one to eight copies of core space. Each copy of core space maps the same frame buffer, external EEPROM, and core registers (see Chapter 2).

• The core registers are all the registers physically implemented in the 21030 except the PCI configuration registers. Note that the block color and plane mask registers are addressed in core space but are physically implemented in the VRAMs.

#### **Data Units**

The following data unit terminology is used throughout this manual.

| Term     | Words | Bytes | Bits | Other    |

|----------|-------|-------|------|----------|

| Nibble   | 1⁄4   | 1⁄2   | 4    |          |

| Byte     | 1⁄2   | 1     | 8    |          |

| Tribyte  | 1½    | 3     | 24   |          |

| Word     | 1     | 2     | 16   |          |

| Dword    | 2     | 4     | 32   | Longword |

| Quadword | 4     | 8     | 64   | 2 Dwords |

| Octaword | 8     | 16    | 128  | 4 Dwords |

| Hexaword | 16    | 32    | 256  | 8 Dwords |

#### External

Unless otherwise stated, throughout this manual the term external means not contained in the DECchip 21030.

#### Note

Notes emphasize particularly important information.

#### Numbering

All numbers are decimal or hexadecimal unless otherwise indicated. In cases of ambiguity, a subscript indicates the radix of nondecimal numbers. For example, 19 is decimal, but  $19_{16}$  and 19A are hexadecimal.

#### **Ranges and Extents**

Ranges are specified by a pair of numbers separated by two periods (..) and are inclusive. For example, a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in angle brackets (<>) separated by a colon (:) and are inclusive. For example, bits <7:3> specifies an extent including bits 7, 6, 5, 4, and 3.

#### **Signal Names**

Signal names are printed in lowercase, bold-faced type. The names of lowasserted signals carry the suffix \_l. The names of high-asserted signals have no suffix. For example, **pll\_clk\_in** is a high-asserted signal, and **pll\_clk\_in\_l** is a low-asserted signal.

# 1 Introduction

This chapter briefly describes the DECchip 21030 PCI Graphics Accelerator and its hardware features, programming model, and supported frame buffer configurations.

#### 1.1 Overview

The 21030 is an application-specific integrated circuit (ASIC) for highperformance 2D and 3D graphics acceleration in systems that use the peripheral component interconnect (PCI). The 21030 accelerates 2D and 3D applications, and enhances X and Win32 windowing system graphics performance. It includes an on-chip glueless PCI interface and is particularly suited for use in high-performance PCs and entry-level workstations.

The 21030 takes advantage of the speed and power of today's microprocessors to provide best-in-class acceleration without the expense and complexity of a separate graphics coprocessor. As a PCI peripheral in systems based on Digital's Alpha AXP architecture or other current microprocessors (see Table 1–1), the 21030 gives desktop products, such as PCs and windows terminals, the graphics performance of a workstation at PC prices.

The 21030 is the latest implementation of Digital's proven graphics architecture, the same architecture that is designed into Digital's Alpha AXP workstations. With the on-chip inclusion of the PCI interface, the 21030 provides a multigenerational plug-and-play graphics system for a variety of current and emerging PCI-based systems. Its high-level of integration provides low-cost and reliable acceleration with the minimum number of additional chips.

The 21030 provides leadership graphics performance for PCI-based desktop workstations and PCs driven by high-performance microprocessors and industry-standard operating systems, graphics user's interfaces (GUIs), and applications programming interfaces (APIs). The 21030 architecture is carefully tuned to work in conjunction with a high-performance CPU, especially an Alpha AXP processor. The 21030 supports the industry-standard 2D graphics APIs Win32 and X and the industry-standard 3D API OpenGL, ported to Windows NT.

Figure 1–1 shows the 21030 in a typical system based on an Alpha AXP microprocessor. The 21030-based graphics subsystem can reside on the motherboard or on a PCI add-in card, possibly opposite the CPU through a PCI-to-PCI bridge.

Table 1–1 lists some of the applicable platforms for the 21030.

ProcessorOperating SystemsAPIsDECchip 21064Windows NTWin32, X, OpenGLDECchip 21066Windows NTWin32, X, OpenGLDECchip 21068Windows NTWin32, X, OpenGL

Table 1–1 Typical Applicable Systems

## **1.2 Features**

The following is a summary of the 21030 hardware features.

• 8-bpp and 32-bpp frame buffers

The 32-bpp frame buffer supports 8-bpp pseudo color, 12-bpp direct color, and 24-bpp true color.

• 64-byte copy buffer

The copy buffer supports high-bandwidth local frame buffer bit-block transfers (BitBlts).

• Bresenham line drawing engine and setup hardware

The on-chip Bresenham line drawing engine and setup hardware performs Bresenham per-pixel line stepping and most of the Bresenham-term setup.

• Faster and simpler line drawing

In many systems, software is responsible for all of the cumbersome line setup calculations, including generating the Bresenham error and address increments for the major and minor axis steps as well as the initial error term.

In the 21030's streamlined interface, software needs to write only the absolute dx and absolute dy values of the line segment to one of eight slope registers, implicitly specifying the drawing octant. The 21030 then automatically generates all of the Bresenham terms, initializes the Bresenham registers, and draws up to 16 pixels. This interface allows software to process more line endpoints, and, combined with 4-way access to the frame buffer, yields 8-bpp line rates in excess of 2,000,000 lines per second.

• Color expansion

The 21030 expands monochrome bitmaps to various pixel depths, for drawing text or filling regions with solid or bitonal brushes.

• Video RAM (VRAM) block-write support

VRAM block-write greatly improves the performance of solid fills and common brushed fills.

• Direct memory access (DMA) engine for image data

The 21030 has DMA-read copy and DMA-write copy modes for fast host-toscreen BitBlts. These modes allow large, contiguous regions to be directly transferred between main memory and the frame buffer. The on-chip PCI interface allows main memory, other PCI graphics devices, or PCI video devices to be the external source or destination.

• High-performance memory controller

The 64-bit memory interface implements Digital's RapiDraw technology (patent pending) to maximize page mode accesses and support 4-way independent addressing to greatly enhance line drawing performance. The memory controller also supports multiple access modes to the frame buffer, which gives 1MB and 2MB frame buffers the same 8-bpp drawing performance as 4MB and 8MB frame buffers.

• 3D support

The 21030 includes hardware to perform color-interpolation for each of three channels (red, green, and blue), Z-buffering, and stencil processing compatible with OpenGL specifications. These functions accelerate typical 3D primitives such as Gouraud-shaded, Z-buffered polygons and depth-cued lines.

• Proprietary dithering

The 21030 implements Digital's AccuLook dithering algorithm (patentpending) to support rendering to 8-bpp and 12-bpp bitmaps. The quality of dithered 8-bpp pseudo-color images surpasses standard 16-bpp direct-color image quality. The quality of the dithered 12-bpp direct-color images is comparable to 24-bpp true-color image quality.

• Support for multiple visual types

Within the context of a 32-bpp frame buffer, the 21030 supports drawing to 8-bpp and 12-bpp bitmaps as well as typical 24-bpp bitmaps. This feature supports independent bitmap depths per window (that is, per application) and high-speed animation.

•  $64 \times 64 \times 2$  on-chip cursor

The 21030 incorporates on-chip cursor control. Optionally, it can retain a cursor image in its off-screen frame buffer memory and pass its control to the RAMDAC.

• High-performance CRT control (CRTC)

The 21030 provides monitor timing and VRAM serial-port control signals to refresh screens up to 1600  $\times$  1280 pixels, 76 Hz, and 16M colors.

• Glueless interface for external RAMDAC and flash ROM

The 21030 can be connected directly to several Brooktree RAMDAC MPU-style interfaces as well as a 256K  $\times$  8 flash ROM.

• Stereo support

The 21030 supports  $2 \times$  reduced-resolution vertical refresh with explicit frame indicator output (that is, *stereo goggle control*).

• PCI-compliant interface

The 21030 is fully electrically compliant with the *PCI Local Bus Specification, Revision 2.0.* The 21030 and its external RAMDAC, EEPROM, and clock generator present only one PCI load.

#### Functions Not Supported

By design, the 21030 generally provides a lower-level hardware interface than typical GUI accelerators. The 21030 does not support the following common GUI accelerator functions, which have little effect on performance.

• The complete Windows set of 256 Boolean raster operations

The Windows manager and most applications typically use only three or four of the 256 Boolean raster operations (ROPs). The most commonly used ROPs are included in the 16 functions supported by the 21030 hardware. For the infrequent cases when the 21030 Windows NT display driver encounters an unsupported ROP, it defaults to the graphics device interface (GDI). This does not affect performance for Windows or the majority of applications (including Windows benchmarks) and has only a negligible effect on the performance of the remaining minority of applications.

On-chip VGA

Windows NT on an Alpha AXP platform does not require VGA compatibility. The 21030 supports external VGA (that is, *palette snooping*) but does not include VGA register-level compatibility. This saves approximately 12,000 unnecessary gates for applications that do not need VGA.

Traditional bit-ordering in Windows monochrome bitmaps

In the 21030 stippling (color expansion) modes, bytes and bits-within-bytes increase from left-to-right across the screen. Traditionally, in Windows monochrome device-independent bitmaps (DIBs), bytes are also mapped from left-to-right, but bits-within-bytes increase from right-to-left with respect to the screen. Although the 21030 hardware does not support such

ordering, the 21030 display driver can use the *lazy realization* paradigm of Windows brush-management to handle this format with negligible degradation in performance.

Under Windows, the driver *realizes* a brush only when the brush is ready to be used. Once realized, the brush can be used indefinitely without being realized again. Therefore, the display driver can reverse the bit order once during the realization process and never again for the life of that brush. Because the most commonly used brushes are stock Windows brushes that can be cached after they are realized, they can be used by multiple applications without being realized multiple times. Consequently, one-time brush preprocessing has little effect on performance.

Advanced rendering

Functions such as antialiasing and texture mapping must be implemented in software, although the 21030 accelerated modes can be used to assist more advanced rendering algorithms; for example, simple-Z mode can be used for texture mapping.

### **1.3 Basic Programming Model**

In the basic 21030 programming model, the processor writes directly to addresses within the 21030's frame buffer address space. The data is interpreted according to the current graphics mode to perform the desired operation. Exceptions to this paradigm are described below.

There are four primary 21030 operating modes: simple, stipple, line, and copy. Each primary mode of operation has an associated plane mask, Boolean raster operation, and destination bitmap depth. The plane mask determines which bits in a pixel can be modified during a write. The raster operation provides one of sixteen 2-operand Boolean function of source (or pattern) and destination, and automatically performs a read-modify-write cycle when necessary. The bitmap depth (and associated byte selection for 8-bpp bitmaps in a 32-bpp frame buffer) specify how pixel data maps to frame buffer Dwords.

• Simple mode

In simple mode, writes to the frame buffer are similar to writes to main memory, except for the optional effects of the pixel mask, plane mask, raster operation, bitmap depth, and bitmap rotation. In this mode, the PCI byte mask and the pixel mask determine which pixels are written.

• Stipple mode

In stipple mode (color expansion mode), data written to the frame buffer is interpreted as a monochrome pattern, in which the following occurs:

- Ones are expanded into foreground pixels.

- Zeros are either expanded into background pixels (opaque stipple mode) or not expanded (transparent stipple mode).

In opaque stipple mode, the pixel mask can be programmed to write fewer than 32 pixels.

• Line mode

In line mode, the processor sets up registers for the Bresenham engine and then writes into the frame buffer at the starting address of the line. The data written by the processor is interpreted as a monochrome pattern, in which the following occurs:

- Ones are expanded into foreground pixels.

- Zeros are either expanded into background pixels (opaque line mode) or have no effect (transparent line mode).

In the 3D line modes, ones are expanded into a shaded, and optionally dithered, color.

Copy mode

In copy mode, the processor writes alternately to the source and destination address within the frame buffer. The data written by the processor is interpreted as a bit mask that specifies which pixels are to be read (source) or written (destination).

#### Extensions to the Basic Programming Model

Several extensions to the basic programming model are available.

• Stipple-fill and block-fill modes

In stipple-fill and block-fill modes, each write causes the 21030 to fill as many as 2K pixels on a scan line, using the 32-bit data as a 32-bit monochrome pattern. The block-fill modes use VRAM block-write cycles for high-bandwidth fills.

Line mode

In line mode, the eight slope registers (one per octant) allow the processor to offload some of the traditional line setup computations. The processor writes the absolute values of the line rise and run to one of the slope registers, implicitly specifying a drawing octant, and causes the 21030 to generate the Bresenham address and error terms and draw up to 16 pixels at one time. Consequently, the processor can specify a short, connected line with one 32-bit write.

• Copy mode

In copy mode, the copy-64 source and copy-64 destination registers allow the processor to read 64 unmasked bytes from the source and write 64 unmasked bytes to the destination with one write to each register. This makes full use of the 64-byte copy buffer for large area copies of 8-bit pixels.

In DMA copy modes, the processor can specify the addresses of the source (DMA-read copy mode) or destination (DMA-write copy mode) in PCI memory space. One write to the frame buffer then causes the 21030 to begin reading from the frame buffer (or PCI) and writing to the PCI (or frame buffer), up to 2K transfers at a time.

Chapter 6 describes all of the 21030 modes and processing algorithms that are implemented in hardware.

### 1.4 Frame Buffer Configurations

While the design-center configurations for the 21030 are 8-bpp and 32-bpp frame buffers, the 21030 supports a variety of 8-, 16-, 24-, and 32-bpp configurations. The supported configurations range from a minimal 8-bpp, 1M-pixel option to a 32-bpp, 2M-pixel option with a full-screen Z-buffer. The 32-bpp frame buffers support 8-bpp, 12-bpp, and 24-bpp bitmap formats. The 21030 supports VRAM-mapped display buffers (that is, the entire visible screen) between 1MB and 16MB. Additional memory for Z-buffers, double-buffers (*back buffers*), or arbitrary off-screen cache and storage can be mapped into DRAM, VRAM, or graphics DRAM (GRAM).

The 21030 normally uses the persistent plane mask and block-write features of advanced VRAMs and GRAMs. However, if these features are not used for drawing off-screen and some performance degradation is acceptable, off-screen memory can be populated with standard DRAMs.

Table 1–2 lists some of the possible frame buffer configurations.

| Size | Resolution<br>@75 Hz NI | Depth | Z-Buffer and<br>Stencil Buffer | Double<br>Buffer     |

|------|-------------------------|-------|--------------------------------|----------------------|

| 1MB  | $1024 \times 768$       | 8     | NA                             | NA                   |

|      | $800 \times 600$        | 16    | NA                             | NA                   |

|      | $640 \times 480$        | 24    | NA                             | NA                   |

| 2MB  | $1600 \times 1280$      | 8     | NA                             | NA                   |

|      | $1024 \times 768$       | 16    | NA                             | NA                   |

|      | $800 \times 600$        | 24    | NA                             | NA                   |

|      | $640 \times 480$        | 32    | NA                             | NA                   |

| 4MB  | $1600 \times 1280$      | 8     | NA                             | NA                   |

|      | $1600 \times 1280$      | 16    | NA                             | NA                   |

|      | $1280 \times 1024$      | 24    | NA                             | NA                   |

|      | $1024\times768$         | 32    | Partial                        | 8/8/8, 12/12 *       |

| 8MB  | $1600 \times 1280$      | 8     | NA                             | NA                   |

|      | $1600 \times 1280$      | 16    | NA                             | NA                   |

|      | $1280 \times 1024$      | 24    | NA                             | NA                   |

|      | $1280 \times 1024$      | 32    | Partial                        | 8/8/8, 12/12 *       |

|      | $1024\times768$         | 32    | Full                           | 8/8/8, 12/12 *       |

| 16MB | $1600 \times 1280$      | 32    | Full                           | 8/8/8, 12/12 *       |

|      | $1280 \times 1024$      | 32    | Full                           | 8/8/8, 12/12, full * |

|      | $1024 \times 768$       | 32    | Full                           | Full <sup>*</sup>    |

Table 1–2 Supported Frame Buffer Configurations

NI — Noninterlaced NA — Not applicable

\* Recommended 3D configurations

Only the 4MB, 8MB, and 16MB 32-bpp configurations provide Z-buffering with stencil support. However, the 21030 can support Z-buffering without a dedicated back buffer to store a full screen of Z data. Any available off-screen space in a 32-bpp frame buffer can be used to perform Z-buffering on a portion of the visible screen (for example, the window for an animation application).

While the 8-bpp frame buffer supports double-buffering only by copy, the 32-bpp frame buffer can support two different types of double-buffering, depending on the configuration of the video back end. A second bank of DRAM can be added as a back buffer to store a full screen of full-depth (24-bit) color. In addition, the 21030 supports multiple formats for 12-bpp and 8-bpp bitmaps within the context of the 32-bpp frame buffer. That is, the 21030 can draw to two 12-bpp bitmaps and three 8-bpp bitmaps at the same pixel locations within 32-bpp buffers. Consequently, in-place double-buffering is possible by coupling the 21030 with either a RAMDAC that can handle images that reside in different planes on a per-window basis (such as the Bt463 RAMDAC) or external multiplexing hardware. By drawing to one 8-bpp or 12-bpp bitmap

while displaying from another bitmap, animation can be performed without copying from off-screen to on-screen memory. In-place double-buffering is possible only on the 32-bpp options at reduced pixel depth.

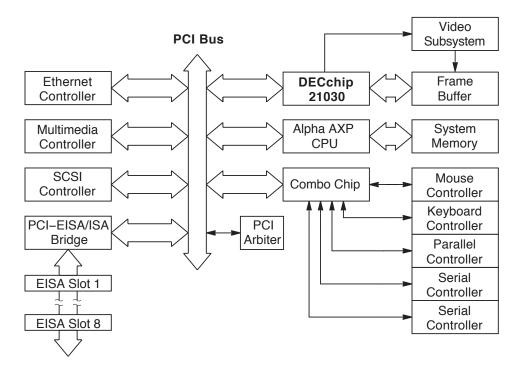

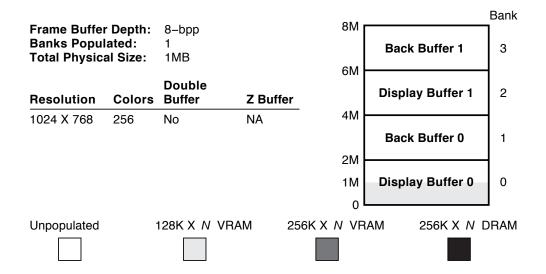

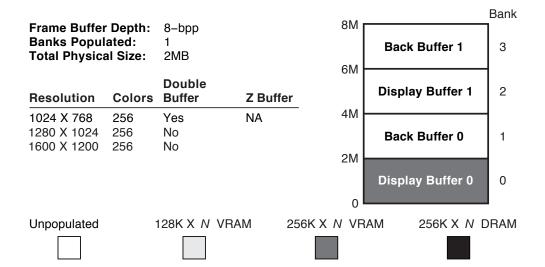

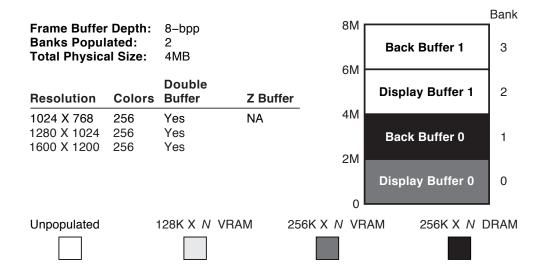

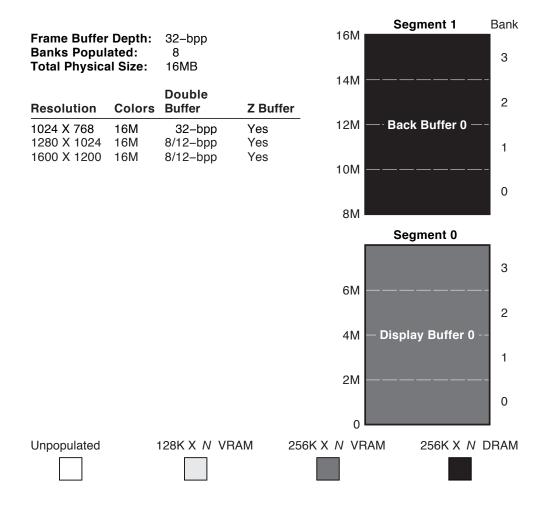

Figure 1–2 shows a typical 8-bpp frame buffer.

Figure 1–2 Typical 8-bpp Configuration

# 2 Memory Space

The 21030 address space consists of three discrete spaces:

- Memory space, described in this chapter

- Configuration space, which includes all of the PCI configuration registers described in Chapter 4

- Expansion ROM space, a 256KB byte-readable address space described in Section 4.2.6

### 2.1 Overview

The 21030 memory space includes the following:

- All 21030 registers except the PCI configuration registers

- The 21030 frame buffer

- Alternate ROM space, an alternate Dword-readable 1MB window into the expansion ROM

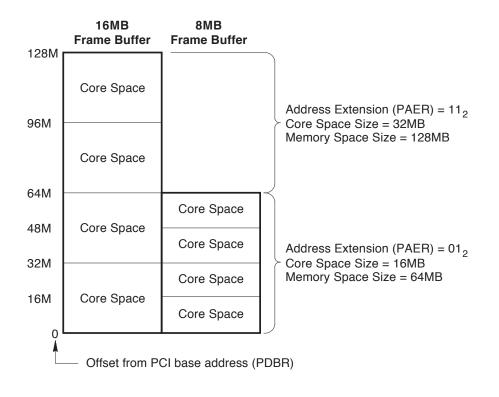

The size of the 21030 step B memory space is 128MB. It is mapped into the PCI memory space at the address specified in the PCI device base address register (PDBR). The memory space consists of 4 to 32 copies of core space. (See Appendix A for 21030 step A differences.)

### 2.2 Core Space

Each copy of core space is identical and maps the same frame buffer (frame buffer space), external EEPROM (alternate ROM space), and core registers (register space). Core space ranges between 4MB and 16MB for an 8-bpp frame buffer and between 16MB and 32MB for a 32-bpp frame buffer, depending on the application (Figure 2–1). The organization and size of each core space is a function of the address-mask and deep fields in the deep register (GDER). These fields are programmed with the values needed to organize the core according to the physical size and depth of the frame buffer in a particular configuration.

Table 2–1 shows the core space size and the deep and address mask field values for some of the supported 21030 frame buffer configurations.

|               | •                       |                    | •              |                  |

|---------------|-------------------------|--------------------|----------------|------------------|

| Configuration | Physical Memory<br>Size | Core Space<br>Size | Deep*<br>Field | Address*<br>Mask |

| 1MB 8-bpp     | 1MB                     | 4MB                | 0              | 000              |

| 2MB 8-bpp     | 2MB                     | 4MB                | 0              | 000              |

| 4MB 8-bpp     | 4MB                     | 8MB                | 0              | 100              |

| 4MB 8-bpp     | 8MB                     | 16MB               | 0              | 110              |

| 4MB 24-bpp    | 4MB                     | 8MB                | 1              | 110              |

| 8MB 24-bpp    | 8MB                     | 16MB               | 1              | 110              |

| 16MB 24-bpp   | 16MB                    | 32MB               | 1              | 111              |

Table 2–1 Frame Buffer Configuration and Core Space

See Table 1–2 and Section 8.1 for the capabilities and physical layout of each configuration.

Figure 2–1 shows memory space mapping as a function of core space size.

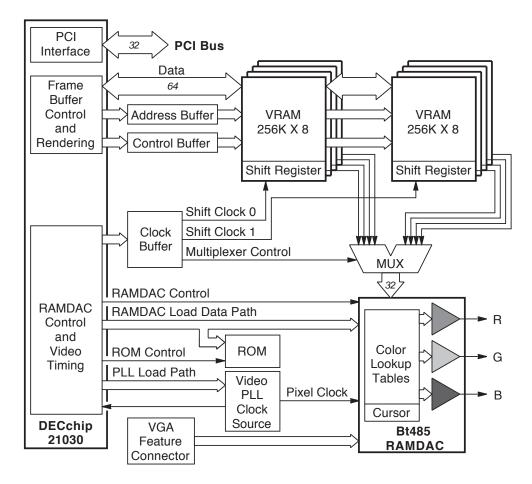

#### 2.2.1 Frame Buffer Space

The frame buffer space consists of one or more buffers, each identified as a *display buffer* or *back buffer*. A display buffer is populated by VRAM and maps to the screen (at least). A back buffer is populated by VRAM, GRAM, or DRAM and maps to such things as a second screen buffer, tiles or brush patterns, and Z and stencil buffers (4MB or 8MB frame buffers only). The block-fill mode, block-stipple mode, and plane-mask feature cannot be used with back buffers populated by DRAMs. The frame buffer space can be accessed through any of the drawing modes described in Chapter 6.

Figures 2–2 and 2–3 show the core space mapping for 8-bpp and 32-bpp frame buffers. Note that some of the reserved regions are aliases for the display and back buffers.

| 128MB 🛛        |                | r                | 1                                   | 1                 |  |  |  |  |

|----------------|----------------|------------------|-------------------------------------|-------------------|--|--|--|--|

| 124MB          | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 120MB          | 4MB Core Space |                  | 16MB Core Space                     |                   |  |  |  |  |

| 116MB          | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 112MB          | 4MB Core Space |                  |                                     | 32MB Core Space   |  |  |  |  |

| 108MB          | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 104MB          | 4MB Core Space |                  | 16MB Core Space                     |                   |  |  |  |  |

| 100MB          | 4MB Core Space | 8MB Core Space   | · ·                                 |                   |  |  |  |  |

| 96MB           | 4MB Core Space |                  |                                     |                   |  |  |  |  |

| 92MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 88MB           | 4MB Core Space | ciniz colo opaco | 16MB Core Space                     |                   |  |  |  |  |

| 84MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 80MB           | 4MB Core Space | child colo opace |                                     | 32MB Core Space   |  |  |  |  |

| 76MB           | 4MB Core Space | 8MB Core Space   |                                     | OZIND COIC OPucc  |  |  |  |  |

| 72MB           | 4MB Core Space | CIVID COIC Opube | – 16MB Core Space                   |                   |  |  |  |  |

| 68MB           | 4MB Core Space | 8MB Core Space   | TOWE COLO OPACC                     |                   |  |  |  |  |

| 64MB           | 4MB Core Space | OND CORE Opace   |                                     |                   |  |  |  |  |

| 60MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 56MB           | 4MB Core Space | OND COLE OPACE   | – 16MB Core Space                   |                   |  |  |  |  |

| 52MB           | 4MB Core Space | 8MB Core Space   | TOME COLE Space                     |                   |  |  |  |  |

| 48MB           | 4MB Core Space | olvid Cole Space |                                     | - 32MB Core Space |  |  |  |  |

| 461VID<br>44MB | 4MB Core Space | 8MB Core Space   |                                     | Szivid Core Space |  |  |  |  |

|                | 4MB Core Space | olvid Cole Space | 16MP Coro Space                     |                   |  |  |  |  |

| 40MB           | 4MB Core Space | 8MB Core Space   | <ul> <li>16MB Core Space</li> </ul> |                   |  |  |  |  |

| 36MB           | 4MB Core Space | olvid Cole Space |                                     |                   |  |  |  |  |

| 32MB           | 4MB Core Space | NAD Core Chase   |                                     |                   |  |  |  |  |

| 28MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 24MB           | 4MB Core Space |                  | <ul> <li>16MB Core Space</li> </ul> |                   |  |  |  |  |

| 20MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 16MB           | 4MB Core Space | OMD Core Oreas   |                                     | 32MB Core Space   |  |  |  |  |

| 12MB           | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

| 8MB            | 4MB Core Space |                  | <ul> <li>16MB Core Space</li> </ul> |                   |  |  |  |  |

| 4MB<br>0       | 4MB Core Space | 8MB Core Space   |                                     |                   |  |  |  |  |

# Figure 2–1 21030 step B Memory Space Organization

Contract from PCI base address (PDBR)

#### Figure 2–2 Core Space Map for 8-bpp Frame Buffers

#### Frame Buffer Space

<sup>1</sup>Aliases Display Buffer 0

<sup>2</sup>Aliases Display Buffer 0 and Back Buffer 0

Figure 2–3 Core Space Map for 32-bpp Frame Buffers

<sup>1</sup>Aliases Back Buffer 0 <sup>2</sup>Aliases portions of Display Buffer 0

# 2.2.2 Register Space

The register space contains the 21030 core registers; that is, the graphics command, graphics control, video timing, cursor, status, and external device registers. It also maps the block-color and plane-mask registers (physically implemented in VRAM). It does not contain the PCI configuration registers. The 1MB register space is divided into 2K 512-byte regions of register space core (Figure 2–4). Each of the 512-byte cores are identical aliases and maps

the registers according to offsets into the 512-byte space (Table 2–2). The register space supports only Dword accesses; individual PCI byte enables are ignored.

#### Note

To avoid a significant performance degradation, drivers can be programmed to use the register aliases rather than memory barrier (MB) instructions with DECchip 21064, 21066, and 21068 processors (Section 7.3). Digital recommends that the drivers be programmed to use aliases separated by 1KB rather than 512 bytes.

Figure 2–4 shows the register space mapping.

#### Figure 2–4 Register Space Organization

Table 2-2 lists the core registers in descending order-of-offset into register space core. See Appendix C for an alphabetical list of the registers.

Table 2–2 Core Registers

| Offset* | Register                                  | Mnemonic | Access |

|---------|-------------------------------------------|----------|--------|

| 1FC     | Reserved                                  | _        |        |

| 1F8     | Command status register‡                  | SCSR     | RW     |

| 1F4     | Reserved                                  | _        | _      |

| 1F0     | Palette and DAC data register‡            | EPDR     | RW     |

| 1EC     | Reserved                                  | _        | _      |

| 1E8     | Clock register                            | ECGR     | WO     |

| 1E4     | Reserved                                  | _        | _      |

| 1E0     | EEPROM write register                     | ERWR     | WO     |

| 1DC180  | Reserved                                  | _        | _      |

| 17C     | Copy 64 destination register <sup>†</sup> | GCDR     | WO     |

| 178     | Copy 64 source register <sup>†</sup>      | GCSR     | WO     |

| 174     | Copy 64 destination register <sup>†</sup> | GCDR     | WO     |

| 170     | Copy 64 source register <sup>†</sup>      | GCSR     | WO     |

| 16C     | Copy 64 destination register <sup>†</sup> | GCDR     | WO     |

| 168     | Copy 64 source register <sup>†</sup>      | GCSR     | WO     |

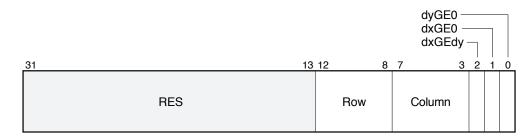

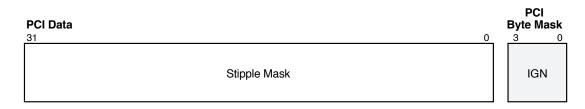

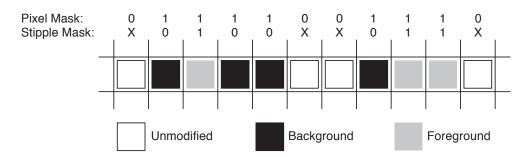

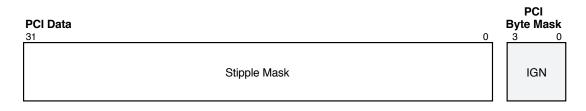

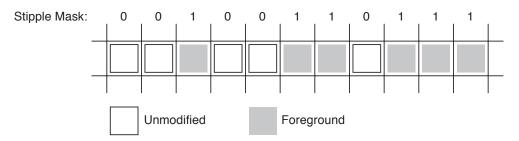

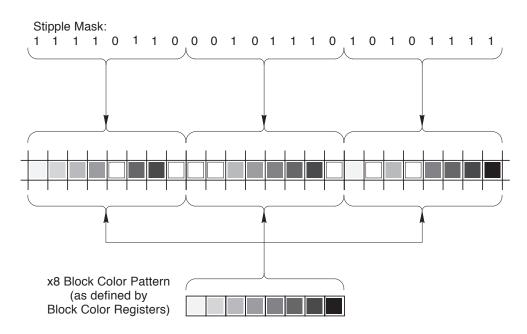

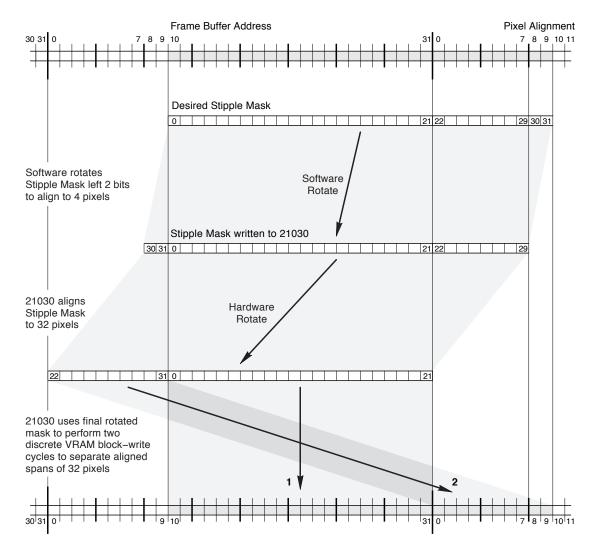

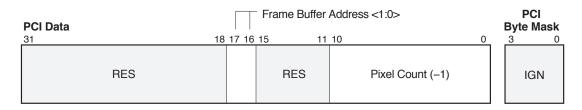

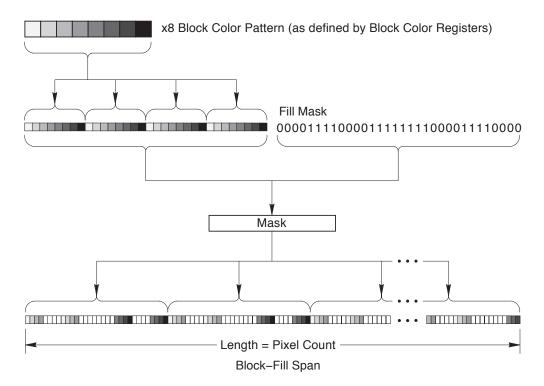

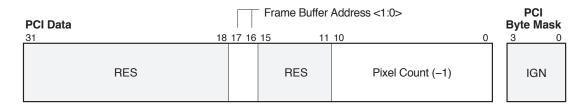

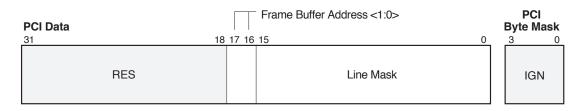

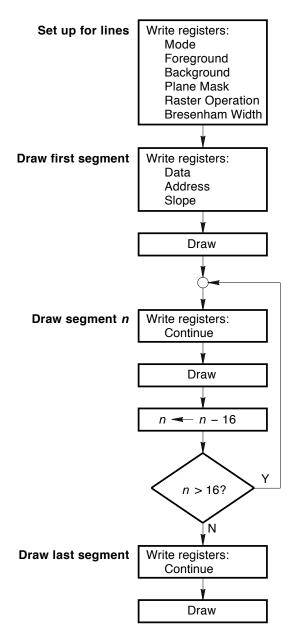

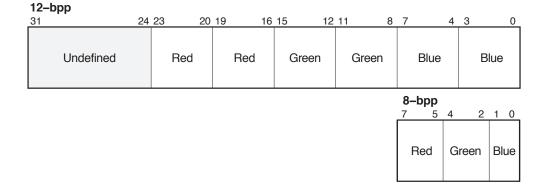

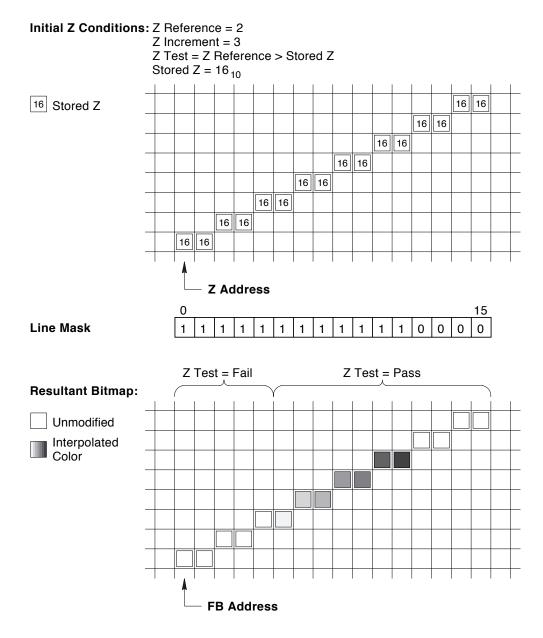

| 164     | Copy 64 destination register              | GCDR     | WO     |