# **Chapter 37 Image Processing Unit (IPU)**

### 37.1 Overview

The IPU is planned to be a part of the video and graphics subsystem in an application processor.

The goal of the IPU is to provide comprehensive support for the flow of data from an image sensor and/or to a display device. This support covers all aspects of these activities:

- Connectivity to relevant devices cameras, displays, graphics accelerators, TV encoders and decoders.

- Related image processing and manipulation: sensor image signal processing, display processing, image conversions, etc.

- Synchronization and control capabilities (to avoid tearing artifacts).

This integrative approach leads to several significant advantages:

- Automation: The involvement of the ARM platform in image management is minimized. In particular, display refresh/update and a camera preview (displaying the input from an image sensor) can be performed completely autonomously. The resulting benefits are reducing the overhead due to SW-HW synchronization, freeing the ARM platform to perform other tasks and reduced power consumption (when the ARM core is idle and can be powered down).

- Optimal data path: Access to system memory is minimized. In particular, significant processing can be performed on-the-fly while receiving data from an image sensor and/or sending data to a display. System memory is used essentially only when a change in pixel order or frame rate is needed. The resulting benefits are reduced load on the system bus and further reduction of power consumption.

- Resource sharing: Maximal HW reuse for different applications, resulting with the support of a wide range of requirements with minimal HW.

The HW reuse mentioned above is enabled by a sophisticated configurability of each HW block. This configurability also allows the support of a wide range of external devices, data formats and operation modes. The resulting flexibility is important also because the support requirements are evolving significantly, so expected future changes need to be anticipated and accounted for.

The following further principles guided the choice of support provided by the IPU:

- For key applications that deserve and need HW support (for acceleration or low power), provide the best support (leading to an optimal implementation).

- For additional applications that can benefit from the HW, consider cost vs. benefit of making minor modifications/extensions to support them.

- For all other relevant applications (to be supported by SW), verify that their support is not degraded.

- Whenever possible, let the operating system (and its windowing system) act as it would without the IPU.

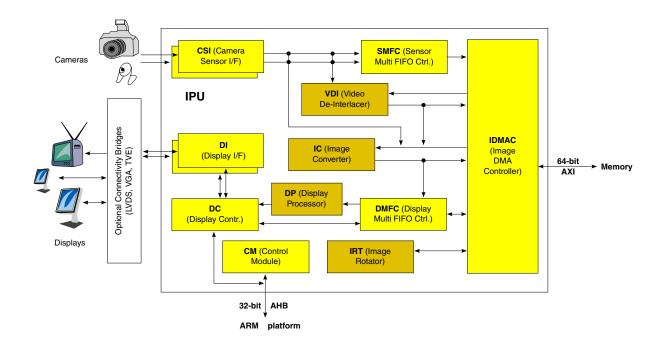

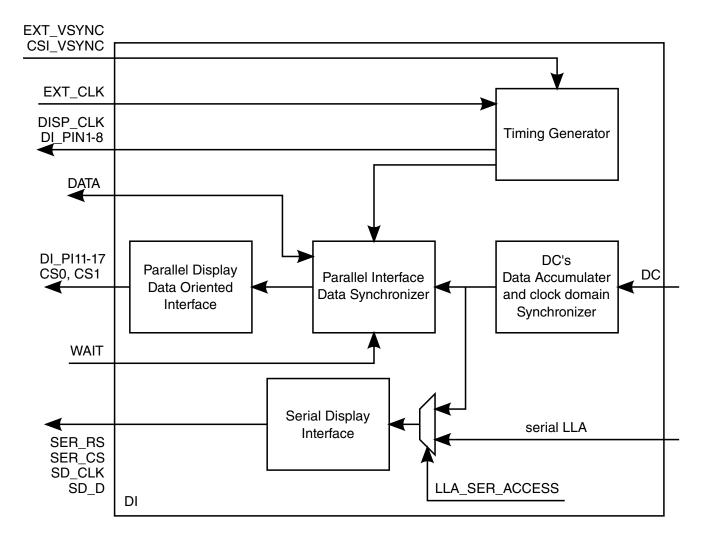

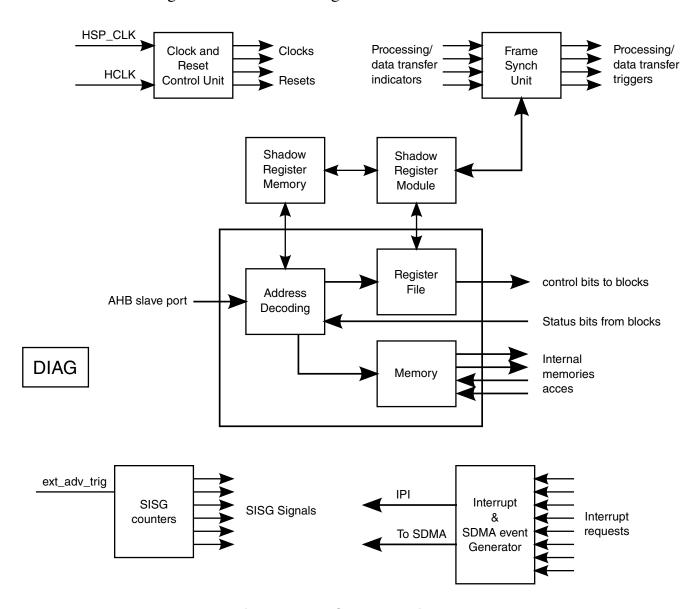

### 37.1.1 Architecture

A simplified block diagram of the IPU can be found here. The role of each block is described in IPU.

Figure 37-1. IPU Block Diagram

Table 37-1. IPU - Block Description

| Block                                | Description                                                                                                    |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|

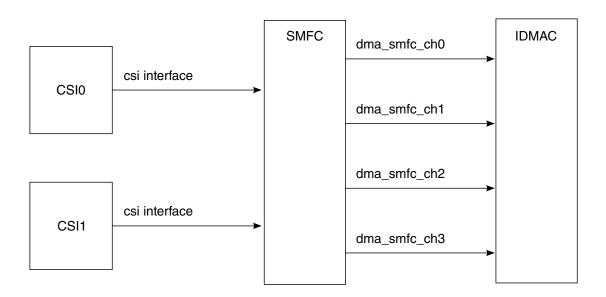

| CSI - Camera Sensor Interface        | Controls a camera port; provides interface to an image sensor or a related device. IPU includes 2 such blocks. |

| DI - Display Interface               | Provides interface to displays, display controllers and related devices.                                       |

|                                      | IPU includes 2 such blocks.                                                                                    |

| DC - Display Controller              | Controls the display ports.                                                                                    |

| DP - Display Processor               | Performs the processing required for data sent to display.                                                     |

| IC - Image Converter                 | Performs resizing, color conversion/correction, combining with graphics, and horizontal inversion.             |

| VDIC - Video De Interlacer           | Performs video de interlacing (Interlaced -> progressive) or combining.                                        |

| IRT - Image Rotator                  | Performs rotation (90 or 180 degrees) and inversion (vertical/horizontal).                                     |

| IDMAC - Image DMA Controller         | Controls the memory port; transfers data to/from system memory.                                                |

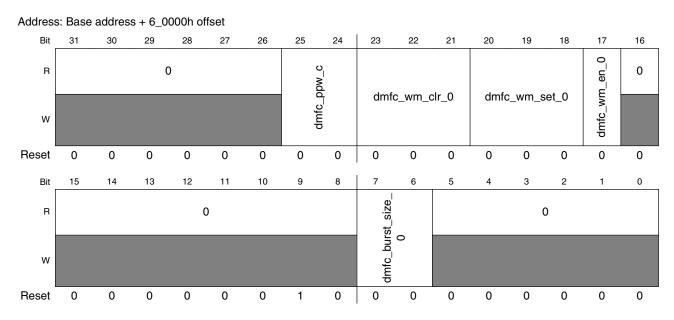

| DMFC - Display Multi FIFO Controller | Controls FIFOs for IDMAC channels related to the display system.                                               |

| CM - Control Module                  | Provides control and synchronization.                                                                          |

# 37.1.2 Features And Functionality

### 37.1.2.1 External Ports

IPU has the following ports:

- Two camera ports each controlled by a CSI sub-block, providing a connection to image sensors and related devices.

- Two display ports each controlled by a DI sub-block, providing a connection to displays and related devices.

- Memory port AXI (AHB V3.0) master, controlled by the IDMAC providing connection to the system memory.

- AHB-lite slave port, providing connection to the ARM Platform (and to any other master connected to the ARM's cross-bar switch).

- Additional ports for control and debug.

### 37.1.2.1.1 Camera Ports

The role of these ports is to receive input from image sensors (or TV decoders) and to provide support for time-sensitive control signals to the camera.

(Non-time-sensitive controls; configuration, reset are performed by the ARM platform through I2C I/F or GPIO signals).

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

Each of the camera ports includes the following features:

- Direct connectivity to most relevant image sensors and to TV decoders.

- Interface types

- Parallel interface

- Up to 20-bit input data bus.

- A single value in each cycle, except for special cases listed in the table below (comments column).

- Programmable polarity.

- High-speed serial interface MIPI (Mobile Industry Processor Interface) CSI-2 (Camera Serial Interface) (implemented partly in the IPU and partly in the HSC).

- Up to four data lanes; up to 800 Mbps per lane

- Class 1 compliancy (supporting all primary formats)

- The data formats

- Interleaved color components, up to 16 bits per value (component).

- The supported formats are listed in the table below.

Table 37-2. Data Formats Supported By The Camera Port

| Format                           | Resolution                                             | On-The-Fly<br>Processing                             | Direct path to memory                                                                                                          | Comments                                                               |

|----------------------------------|--------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Bayer RGB                        | 8 bits/value                                           | No                                                   | 8- or 16-bit values                                                                                                            | MIPI mandatory format                                                  |

|                                  | 9-10 bits/value No Written to the MSB of a 16-bit word |                                                      |                                                                                                                                | 10 bits/value is a MIPI mandatory format                               |

|                                  | 16 bits/value                                          | No                                                   |                                                                                                                                |                                                                        |

| Full RGB or YUV<br>4:4:4         | 444/555 mode                                           | Yes, starting with color extension to 8 bits/ sample | Yes                                                                                                                            | MIPI optional formats In parallel I/F: through an 8-bit or 16-bit bus  |

|                                  | 565 mode                                               |                                                      |                                                                                                                                | MIPI mandatory format                                                  |

|                                  |                                                        |                                                      |                                                                                                                                | In parallel I/F: through an 8-bit or 16-bit bus                        |

|                                  | 8 bits/value<br>(888 mode)                             | Yes                                                  | Yes                                                                                                                            | MIPI mandatory format                                                  |

|                                  | 8-16 bits/value                                        | No                                                   | 8- or 16-bit components<br>are written to the MSB of<br>a 16-bit word 10 bits/<br>value can also be<br>packed in a 32-bit word |                                                                        |

| YUV 4:2:2<br>Component<br>order: | 8 bits/value                                           | Yes                                                  | Yes                                                                                                                            | MIPI mandatory format<br>(UY1VY2)<br>In parallel I/F: through an 8-bit |

| UY1VY2 or<br>Y1UY2V              |                                                        |                                                      |                                                                                                                                | bus (such as BT.656) or 16-bit<br>bus (such as BT.1120)                |

Table 37-2. Data Formats Supported By The Camera Port (continued)

| Format       | Resolution      | On-The-Fly<br>Processing | Direct path to memory                                                                                  | Comments                                                                                     |

|--------------|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|              | 9-10 bits/value | No                       | Written to the MSB of a 16-bit word                                                                    | In parallel I/F: through a 10-bit<br>bus (such as BT.656) or 20-bit<br>bus (such as BT.1120) |

|              | 16 bits/value   | No                       | Written to the MSB of a 16-bit word                                                                    |                                                                                              |

| Gray scale   | 8 bits/value    | No                       | Yes                                                                                                    |                                                                                              |

|              | 16 bits/value   | No                       | Written to the MSB of a 16-bit word                                                                    |                                                                                              |

| Generic data |                 | No                       | Yes                                                                                                    | MIPI mandatory format                                                                        |

|              |                 |                          | In a parallel I/F, if wider<br>than 8 bits, each bus<br>word is written to the<br>MSB of a 16-bit word | May be used for any other formant, such as JPEG/MPEG4                                        |

- Scan order: progressive or interlaced data (expected only for YUV 4:2:2) is sent directly to system memory, where it can be read back for further processing.

- Frame size: up to 8192 x 4096 pixels

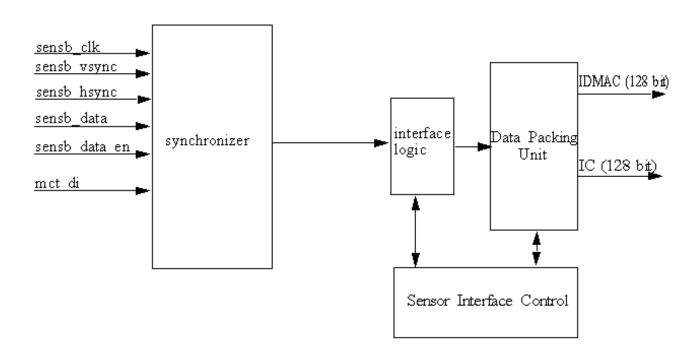

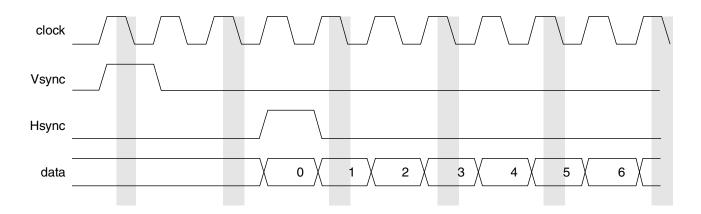

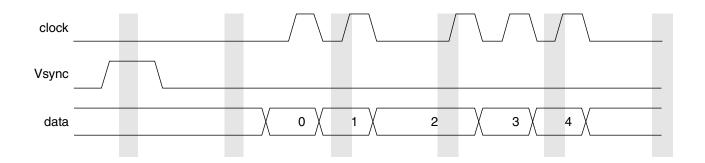

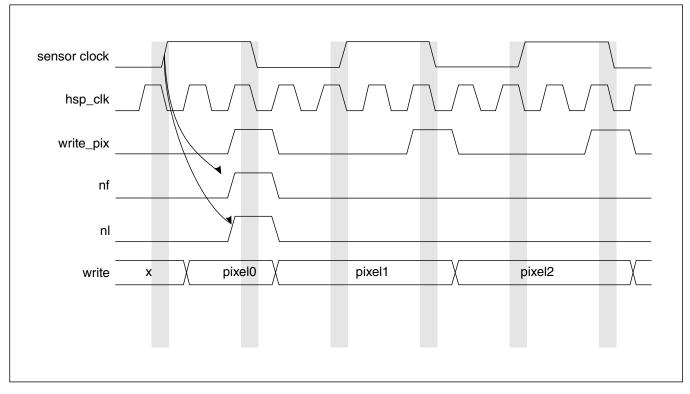

- Synchronization: video mode

- The sensor is the master of the pixel clock (PIXCLK) & synchronization signals

- Synchronization signals are received using either of the following methods:

- Dedicated control signals -VSYNC, HSYNC with programmable pulse width & polarity

- Controls embedded in the data stream, following loosely the BT.656 protocol, with flexibility in code values and location.

- Synchronization : still image capture

- The image capture is triggered by the ARM platform or by an external signal (such as a mechanical shutter).

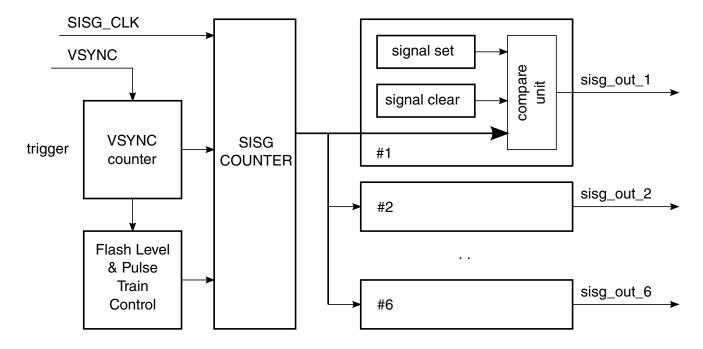

- Synchronized strobes are generated for up to 6 outputs the sensor and camera peripherals (such as flash, mechanical shutter).

- Additional features

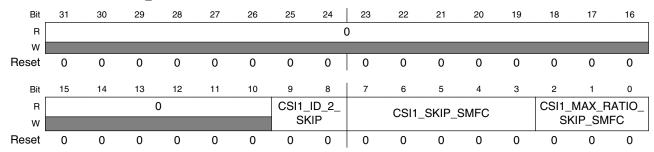

- Frame rate reduction, by the periodic skipping of frames

- The supported reduction ratios are: m:n, where m,n<=5

- This is supported independently for the different destinations IC, SMFC.

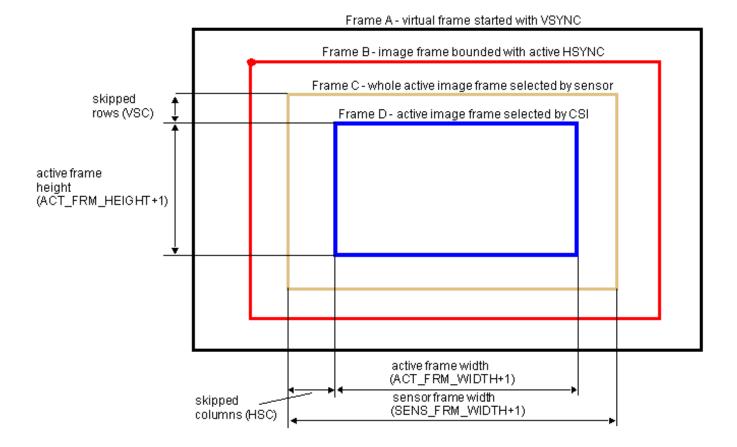

- Window-of-interest selection

- Pre-flash for red-eye reduction and for measurements (such as focus) in lowlight conditions

Several sensors can be connected to each of the CSIs. Simultaneous functionality (sending data) is supported as follows:

- Two sensors can send data independently, each through a different port, each using either parallel or fast serial interface.

- Several sensors can send data to the same port, using the MIPI interface (through a HUB), each sensor being identified by different ID's.

- Unpacking and companding capabilities are provided for up to two streams (either through same or different interfaces), while the other ones are treated as generic data.

- Only one of the (non-generic) streams can be transferred to the VDI C or IC for onthe-fly processing, while the others are sent directly to system memory.

The input rate supported by the camera port is as follows:

For parallel interface, the maximum speed of the interface is 240Mhz. The required operating frequency of the interface is calculated in the following way:

$$F = FH * FW * FPS * BI * DF$$

### Where

- **FH** = frame height (in pixels)

- **FW** = Frame width (in pixels)

- **fps** = frame rate (frames per second)

- **BI** = typically 35% overhead, should be assumed as 1.35. The actual blanking intervals are a parameter of the attached device.

- **DF** = data format, defines the number of cycles needed to send a single pixel.

The number of cycles needed to send a single pixel depends on the interface and the data format.

### Data format examples:

- YUV422 over 16 bit = 1 cycles/pixel

- RGB888 over 8 bit = 3 cycles/pixel

- RGB565 over 16 bit = 2 cycles/pixel

- Bayer/Generic data = 1 cycle/pixel

- YUV422 over 8 bit = 2 cycles/pixel

- BT.656, YUV422 format = 2 cycles/pixel

- BT.1120, YUV422 format = 1 cycle/pixel

# Examples of supported interfaces:

- 3.2MP camera, 15fps, yuv422 format, 8 bit interface

- 1080P30, yuv422, 8 bit interface

Fast serial interface (MIPI-CSI2):

- IPU receives 2 components per cycle from the MIPI-CSI2 interface

- The maximum speed of the interface is:

- 200Mhz for 4 data lanes configuration

- 250Mhz for 2 data lanes configuration

The maximum bandwidth of the interface is as follows:

- 200Mhz for 4 data lanes configuration (800Mbps/lane, 400MByte/sec)

- 187.5Mhz for 3 data lanes configuration (1000Mbps/lane, 375MByte/sec)

- 125Mhz for 2 data lanes configuration (1000Mbps/lane, 250MByte/sec)

- 62.5Mhz for 1 data lane configuration (1000Mbps/lane, 125Mbyte/sec)

The required operating frequency of the interface is calculated in the same way as for parallel interface above. The DF parameter is different.

- YUV422 = 1 cycle/pixel

- RGB888 = 1.5 cycles/pixel

- Generic data = 2 bytes/pixel

Examples of supported interfaces:

- 3.2MP camera, 2 lanes configuration, 15fps, yuv422 format (~65Mhz)

- 6MP camera, 4 lanes configuration, 15fps, RGB888 format (~182Mhz)

# **37.1.2.1.2 Display Ports**

The role of these ports is to communicate with display devices, either directly or through a controller (such as a graphics accelerator) or a bridge (such as a TV encoder or an LVDS interface bridge).

#### 37.1.2.1.2.1 Access Modes

Two access modes are supported.

### 37.1.2.1.2.1.1 Synchronous Access

In this mode, the IPU transfers a two-dimensional block of pixels to the display device, in synchronization with the screen refresh cycle.

It is called "video mode" in the MIPI standards.

This mode has a dual role:

- For a RAM-less display or a TV screen, this mode is used to perform the screen refresh process from a display buffer in system memory.

- For a "smart" display, this mode is used to transfer a rectangular block of pixels to the display's screen and, in some cases, also to the display buffer

- The transferred block may be only part of the screen (the rest of the screen being refreshed by the integrated controller, from the internal buffer). Moreover, a mask can be used to transfer to the display only parts of the block, such as a window partly hidden by other windows.

- If the block is transferred only to the screen, the transfer rate must be equal to the refresh rate. If, however, the transfer is also to the display's memory, the rate can be reduced to the rate at which the input buffer is updated.

In all cases (including the last one), the IPU sends to the display all the synchronization signals controlling the screen refresh and the block transfer is synchronized with these signals. This synchronization means that tearing effects are avoided when using this mode.

### 37.1.2.1.2. Asynchronous Access

This is the main mode used for communicating with an external display controller (possibly in a smart display or a graphics accelerator).

It is called "command mode" in the MIPI standards. In this mode, the IPU performs random access - read/write - to the memory and registers of the controller.

Two types of addressing methods are supported

- Generic linear addressing of pixels and generic data

- 2-dimensional (X/Y) addressing of pixels

The following access types are provided:

- Data transfer to the external device, after on-the-fly processing in the IPU.

- Data transfer (DMA) read/write between the host's system memory and the external device, through the IPU's memory port (controlled by the IDMAC), such as the transfer of a rectangular block of pixels (possibly full screen).

- Host access read/write to an external device, through the AHB-slave port

- Access types

- Direct access emulating a directly-addressed access (see below) This includes burst access (incremental; up to 8 words/burst)

- Low-level access leaving to the host the explicit generation of the access protocol

- The possible accessing modules include the ARM platform and the system DMA controller (as well as any other AHB master connected to the ARM's cross-bar switch).

Transfer of video/graphics data stream to controller's display buffer is performed using one of the first two modes above. Unlike in the synchronous mode, this process is not tightly-synchronized with the screen refresh cycle. However, a loose synchronization - to avoid tearing - is still possible: the appropriate timing for the transfer can be derived from the VSYNC signal of the screen refresh - either generated by the IPU's display controller or received from the external controller.

The asynchronous access requires the specification of an address. The display interface uses "indirect addressing", namely, there is no address bus, and the address, as well as control and configuration commands, are embedded in the data stream. The access procedure - including writing addresses and commands - is managed autonomously by the interface, in one of two ways:

- Automatic emulation of transparent access, following microcode ("access template") generated by the ARM Platform. This mechanism is very flexible, supporting a wide variety of devices.

- Streaming commands/addresses from a buffer stored (by the ARM Platform) in system memory.

Note that direct access requires the use of the first method - automatic emulation.

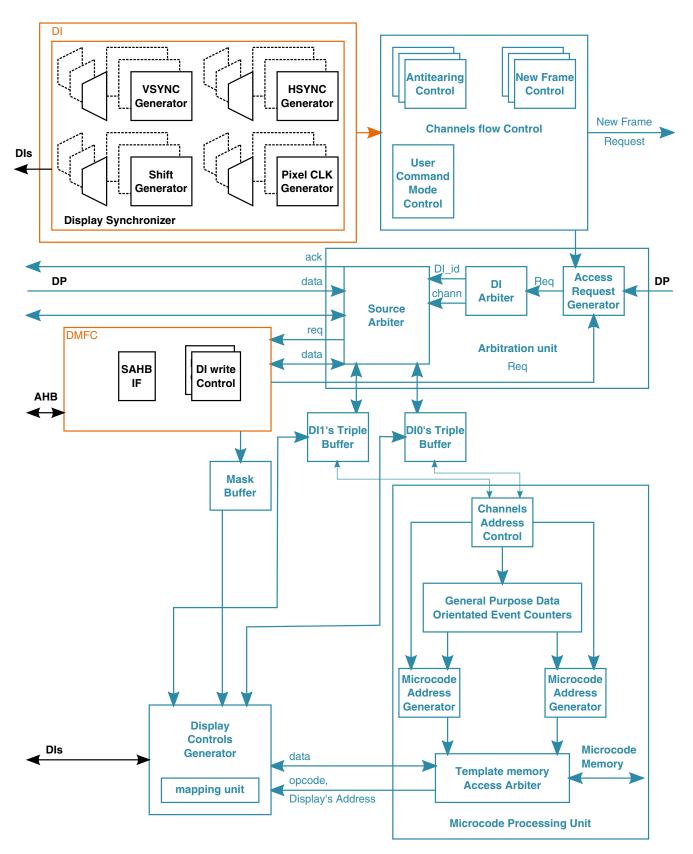

### 37.1.2.1.2.2 Display Interface

The display interface is very flexible and supports a wide variety of devices from major manufacturers. The following interface types are provided (in each of the two display ports)

- Parallel video interface (for synchronous access) up to 24-bit data bus.

- Compatible with MIPI-DPI standard .

- Control protocol follows Sharp HR and generic TFT definitions

- Supports BT.656 (8-bit) and BT.1120 (16-bit) protocols

- Supports HDTV standards SMPTE274 (1080i/p) and SMPTE296 (720p)

- A parallel bidirectional bus interface (for asynchronous access) up to 32-bit data bus.

- Compatible with MIPI-DBI standard.

- Control protocol either system-80 or system-68K The timing and polarity of the signals are programmable.

- Byte-enable optional, for a 16-bit interface

- Burst access for direct access, the burst is determined by the corresponding signal in the AHB interface.

- A serial interface 3-wire, 4-wire and 5-wire (two flavors) (for asynchronous access)

- High-speed serial interface: MIPI (Mobile Industry Processor Interface) DSI (Display Serial Interface) full support, with up to 2 data lanes, up to 4 virtual channels (implemented party in the IPU and partly in the HSC).

The supported formats for pixel data are

- RGB color depth fully configurable; up to 8 bits/value (color component)

- YUV 4:2:2, 8 bits/value (for TV encoder)

- All mandatory formats in MIPI's DBI, DPI and DSI.

In the parallel interfaces, the data bus has up to 32 bits. Non-trivial mapping of pixels to the bus is restricted to the 24 LSB's. This mapping is fully configurable and very flexible. In the serial interfaces, the data is mapped in the same way as in the parallel interfaces and then serialized.

The interface also supports "generic data". Such data is transferred - byte-by-byte, without modification - between the system memory and the display device (through a serial interface or 8/16-bit parallel interface). Non-conventional pixel formats can be supported by considering them as "generic data".

For the interface clock, there are the following options (independently for each port)

- Derived from the IPU internal clock (master mode)

- Provided by an external source (slave mode)

The transfer rate supported:

- For single port (for on-chip interfaces):

- 240 Mega-Accesses/Sec if the DI clock is derived from an external to IPU source (like another PLL)

- 264 Mega-Accesses/Sec if the DI clock is derived from the IPU clock (HSP\_CLK)

- When off-chip interfaces are involved the rate may be limited by IO capabilities. Please refer to the device's data-sheet for exact numbers.

For synchronous access with one cycle/pixel, this enables, e.g (including 35% blanking intervals)

• 1080p (1920x1080) @ 60 fps

- WSXGA+ (1680x1050) @ 60 fps

- The combined rate for the two ports is up to 240 MP/sec

The interface includes the following additional features:

- Screen size: up to 4096 x 2048 pixels, programmable by software.

- Scan Order: progressive or interlaced

- Synchronization

- Programmable horizontal and vertical synchronization output signals (for synchronous access)

- Data enabling output signal

- Software contrast control using 8-bit programmable pulse-width modulation (PWM) Two dedicated PWM outputs are provided

### **Connecting To Display Devices**

IPU allows the connectivity to multiple display devices. In particular, it supports the following setup:

- Primary LCD display; can be smart, dumb (RAM-less) or dual-port; may use fast serial, or the parallel interface or (through an integrated bridge) LVDS interface.

- Second LCD display; can be smart or dumb (RAM-less); may use fast serial, parallel or serial interface or (through an integrated bridge) LVDS interface.

Each of the above connections has independent settings - interface timing, access template, chip-select, etc.

Simultaneous functionality of the above devices is possible in each of the following ways:

- Two devices can be accessed (synchronously or asynchronously) independently, each through a different port: each using any of the available interfaces.

- Two devices can time-share asynchronous accesses through the legacy serial & parallel interfaces, using the CS signals.

- Two devices can be accessed synchronously or asynchronously through the same port, using the MIPI interface (through a HUB), each device being identified by different ID's.

- An asynchronous access can be performed during vertical blanking intervals of a synchronous access (screen refresh; to the same or other device).

The possibilities for simultaneous functionality by time-sharing the legacy interfaces in a single port are summarized in the following table.

Table 37-3. Simultaneous Functionality of Display Port By Time-Sharing Legacy Interfaces

|                                                      | Second/Third Display Type         |                                                                          |                                                                      |  |  |

|------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Primary Display Type                                 | Smart Display<br>Serial Interface | Smart Display Parallel Interface Asynchronous access                     | RAM-less display or TV screen                                        |  |  |

| Smart Display Parallel Interface Asynchronous access | Yes                               | Yes                                                                      | Yes; access to the smart display is restricted to blanking intervals |  |  |

| Dual Port Smart Display<br>Synchronous access        | Yes                               | Yes, access to the secondary display is restricted to blanking intervals | Not Available                                                        |  |  |

| TFT RAM-less Display Or TV screen                    | Yes                               | Yes, access to the smart display is restricted to blanking intervals     | Not Available                                                        |  |  |

| Graphics Accelerator                                 | Yes                               | Yes, if the accelerator supports a chip select functionality             | Not Available                                                        |  |  |

# 37.1.2.1.3 Memory Port

The memory port is an AXI (AHB V3.0) master port, used to read/write data - typically two-dimensional blocks from/to system memory.

The interface supports the following features

- Clock rate up to 264 MHz (equal to the internal clock)

- 64-bit data bus

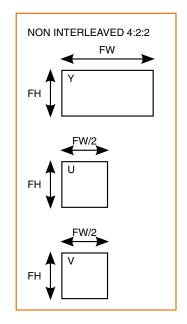

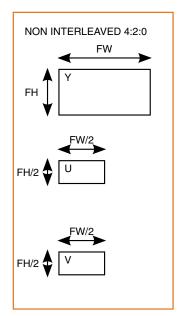

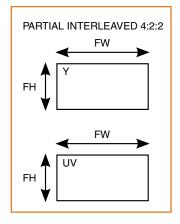

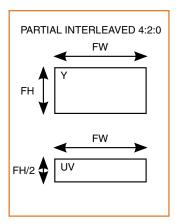

- The supported data formats are listed in the table below.

Table 37-4. Data Formats Supported By The Memory Interface

| Format                                    | Resolution                          | Input/Output | Comments                                           |

|-------------------------------------------|-------------------------------------|--------------|----------------------------------------------------|

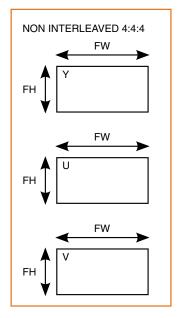

| Non-interleaved YUV                       | 8 bits/value                        | both         | 4:4:4, 4:2:2, 4:2:0 formats                        |

| (in three separate buffers)               |                                     |              |                                                    |

| Partially-interleaved YUV (in             | 8 bits/value                        | both         | 4:2:2, 4:2:0 formats                               |

| two separate buffers)                     |                                     |              | Y buffer and UV buffer                             |

| Interleaved YUV                           | 8 bits/value                        | both         | 4:4:4 format (YUV)                                 |

| (all color components in a single buffer) |                                     |              | 4:2:2 format (UY1VY2 or UY2VY1 or Y1UY2Vor Y2UY1V) |

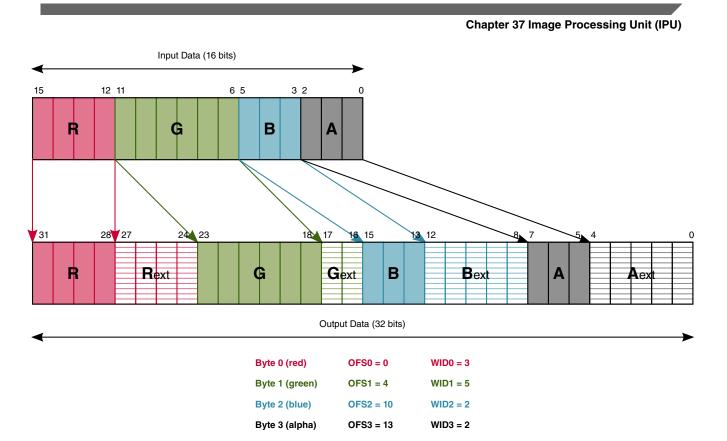

| Interleaved true color                    | 8, 12,16, 18, 24, 32 bits/<br>pixel | both         | Flexible component location  A: translucency value |

Table 37-4. Data Formats Supported By The Memory Interface (continued)

| Format            | Resolution                   | Input/Output | Comments                    |

|-------------------|------------------------------|--------------|-----------------------------|

|                   | 0 - 8 bits per R/G/B/A value |              | (only in input)             |

| Coded color       | 4,8 bits/pixel               | input only   |                             |

| (using a palette) |                              |              |                             |

| Gray scale        | 8 bits/pixel                 | both         |                             |

|                   | 4 bits/pixel                 | input only   | Transferred to display port |

| Generic data      | 8 bits/unit                  | both         | E.g.:                       |

| (Transparent M)   |                              |              | From CSI to DI              |

|                   |                              |              | Compressed data to/from DP  |

|                   |                              |              | Translucency for combining  |

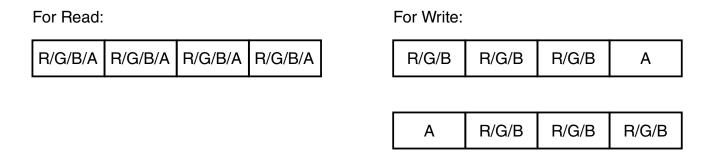

- The pixel formats are translated to/from a uniform internal format: RGBA/YUVA 8:8:8:8

- The supported ordering of bytes and pixels is little endian. For 4 bits/pixel, big endian is also supported.

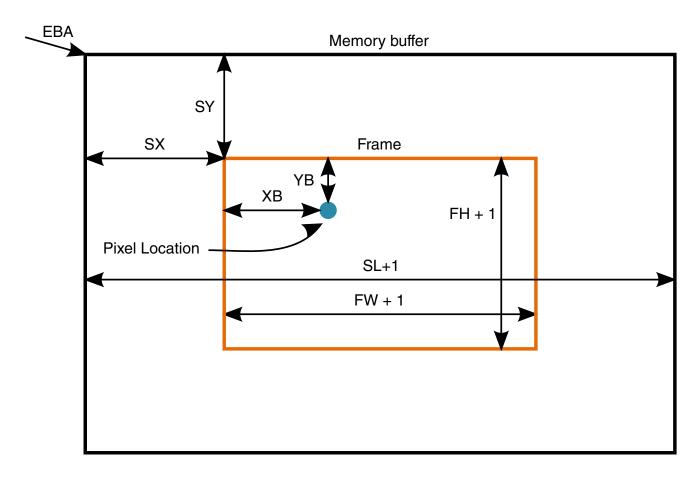

- Addressing modes include:

- Sequential access (to a contiguous memory buffer) for generic data.

- Raster-scan within a two-dimensional window of a video/display buffer for both pixel and generic data.

- Raster-scan of two-dimensional blocks within a two-dimensional window (for rotation of pixel data)

- Additional features

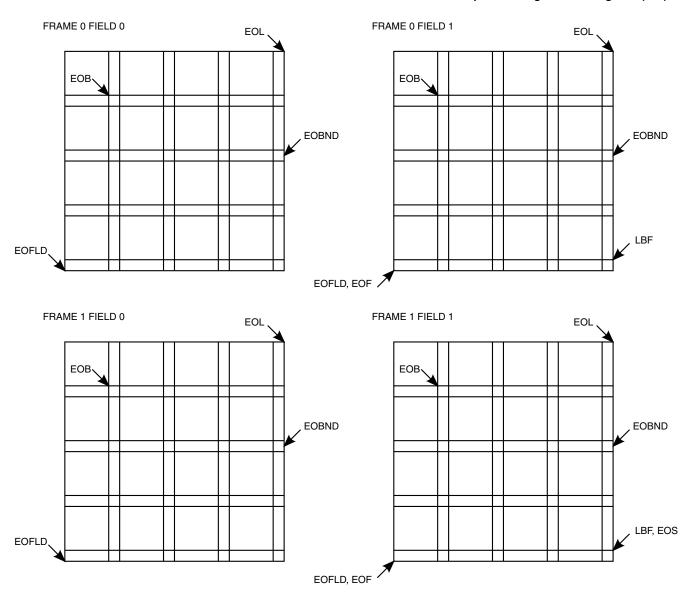

- Scan order: progressive or interlaced Interlaced access is supported for fields which are stored either in separate memory buffers or with rows interleaved in a single buffer.

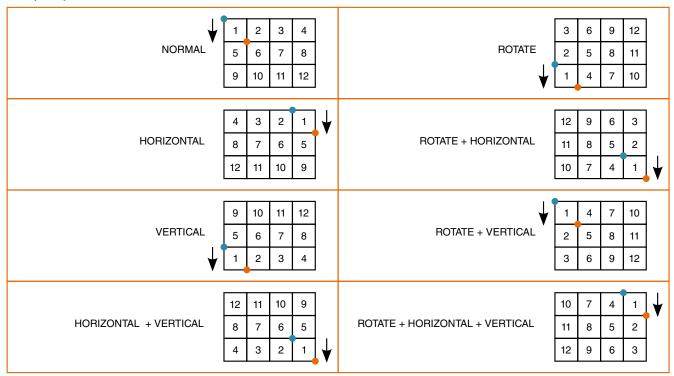

- Reordered scan, implementing inversion and rotation.

- Rotation and horizontal inversion only when transferring two-dimensional blocks (to/from the IRT)

- Vertical inversion also in row-by-row raster-scan

- Scrolling

- Applications Panning within a frame Frame scrolling

- Not supported for non-interleaved and partially-interleaved formats

- Resolution Vertical: single pixel Horizontal: 18 BPP 4 pixels; 12, 4 BPP or YUV 422 - 2 pixels; other formats - one pixel

- Conditional read (for combining): fully-transparent or hidden pixels are not read.

- This is supported, for graphics. by reading the transparency (alpha) from a separate buffer

- Input/output FIFOs (in the SMFC, DMFC and in the processing sub-blocks) size adjusted to provide resilience for latency of up to 1500 cycles.

# 37.1.2.1.4 Processing

The IPU processes rectangular blocks of pixels. The processing is performed in these sub-blocks - VDIC, DP, IC and IRT.

(see the IPU block diagram and Table 37-1).

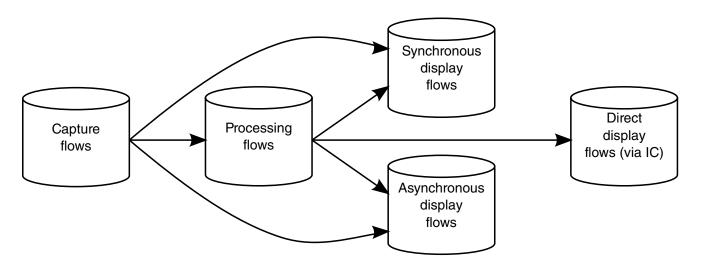

### **37.1.2.1.4.1 Processing flows**

Several time-shared data flows are supported, as described in the following table.

Table 37-5. Time-Shared Data Flows through the IPU

| Name                                                  | Number                                          | Туре | Flow                                                            | Target                                                                | Restrictions                                                                                                                                                                      |

|-------------------------------------------------------|-------------------------------------------------|------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Refresh/ 5 flows (at most two of them of type |                                                 | DS1  | Fmem -> DP -> Display                                           | Synchronous Access<br>(e.g. display refresh;<br>controlled by the DI) |                                                                                                                                                                                   |

|                                                       | DS1)                                            | DS2  | Fmem -> DP -> Display                                           | Asynchronous Access (e.g. display update)                             |                                                                                                                                                                                   |

|                                                       |                                                 | DS3  | Fmem <-> Display                                                | Generic Data Transfer                                                 |                                                                                                                                                                                   |

|                                                       | 1 flow                                          | DS4  | ARM Platform<-> Display                                         | Direct Access                                                         |                                                                                                                                                                                   |

| Video Playback                                        | flows                                           | PL1  | Bmem -> VDIC -> IC -><br>Bmem -> IRT -> Fmem<br>+ DSx           | Main option                                                           |                                                                                                                                                                                   |

|                                                       |                                                 | PL2  | Fmem -> IRT -> Bmem ->                                          | Low power                                                             | Large enough window                                                                                                                                                               |

|                                                       |                                                 |      | IC -> DP                                                        | (branching to DSx, as a video plane)                                  | No other video flows                                                                                                                                                              |

|                                                       |                                                 | PL3  | Fmem -> VDIC -> IC -> DP                                        | Low power                                                             | Interlaced source                                                                                                                                                                 |

|                                                       |                                                 |      |                                                                 | (branching to DSx, as a                                               | Large enough window                                                                                                                                                               |

|                                                       |                                                 |      |                                                                 | video plane)                                                          | No other video flows                                                                                                                                                              |

| Camera Preview                                        | 1 flow<br>(VF2 may be                           | VF1  | Sensor -> IC -> Bmem -> IRT -> Fmem+DSx                         | main option                                                           | Single progressive input                                                                                                                                                          |

|                                                       | (VF2 may be<br>used also as a<br>playback flow) |      | Sensor -> Fmem -> VDIC -<br>> IC -> Bmem -> IRT -><br>Fmem+ DSx | two inputs and/or interlaced input                                    | When the VDIC is used, one of the three input fields can go directly from the sensor to the VDIC. In that case the sensor output goes to the memory via the VDIC and not the SMFC |

|                                                       |                                                 | VF4  | Sensor -> IC -> Fmem                                            | Low power                                                             | Single progressive input                                                                                                                                                          |

|                                                       |                                                 |      | + DS1                                                           | RAM-less Display                                                      | Refresh rate = 2x sensor                                                                                                                                                          |

|                                                       |                                                 |      |                                                                 | Single Display Buffer                                                 | frame rate                                                                                                                                                                        |

|                                                       |                                                 |      |                                                                 | (in internal memory)                                                  | Large enough window                                                                                                                                                               |

|                                                       |                                                 |      |                                                                 | Tearing-less                                                          | No other video flows                                                                                                                                                              |

| Video Record                                          | 1 flow                                          | RCx  | IC -> Bmem -> IRT -><br>Fmem                                    | (branching from VFx)                                                  |                                                                                                                                                                                   |

Table 37-5. Time-Shared Data Flows through the IPU (continued)

| Name     | Number  | Туре | Flow       | Target                   | Restrictions |

|----------|---------|------|------------|--------------------------|--------------|

| Graphic  | 2 flows | GF1  | Fmem -> IC | (combining with the main |              |

| Overlays | 2 flow  | GF2  | Fmem -> DP | flow                     |              |

### Comments

- System memory usage legend

- Fmem: frame double-buffer (page-flip) in system memory (typically external memory: DDR DRAM [address 0x1000\_0000 0xFFFF\_FFFF])

- Bmem: two possibilities

- A frame double buffer, as above

- A band (4-256 rows) double-buffer (page-flip) in system memory (could be internal memory: OCRAM [address 0x0900\_0000 0x093F\_FFFF])

- Direct arrow between two processing stages represents an internal pipeline

- Time-sharing

- IC can time-share tightly three flows: one VFx, one RCx and one PLx (with independent processing parameters)

- DP can time-share one DS1 flow and a one DS2 flow (each with different destinations and independent processing parameters)

- Direct access to display (DS4) time-shares tightly the display port with other active DSx flows.

- Other time-sharing (between PLx flow and DS2 and DS3 flows in IRT) is frameby-frame

- Any of the processing stages in the above flows can be skipped.

- Triggering and synchronization

- Flow segments starting from a sensor are triggered and synchronized by input from the sensor

- Flow segments ending with display refresh are triggered and synchronized by the refresh control mechanism in the DI.

- Flow segments starting and ending in system memory, are triggered either by the double buffering mechanism or by explicit configuration and are processed continuously without delay, at a rate determined by the available resources. These flow segments have a lower priority than the sensor/display-driven flows.

The functionality of each of the processing blocks is described below.

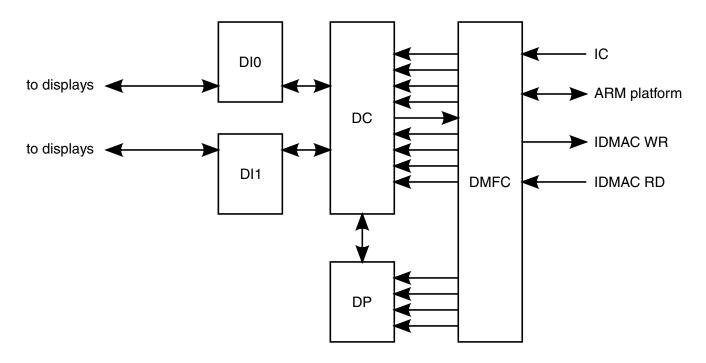

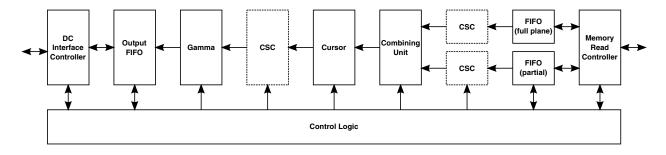

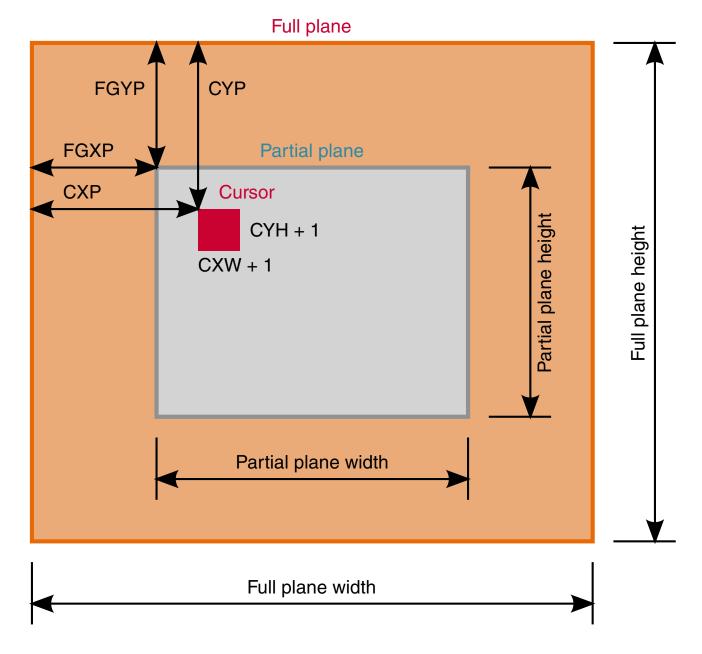

# 37.1.2.1.4.2 Display Processor (DP)

The Display Processor performs all the processing required for data sent to a display.

• Input: from the IC and/or from system memory

- Order: rows, progressive or interlaced

- Format: YUVA/RGBA, non-decimated, 8 bits/value

- Processing chain

- Combining 2 video/graphics planes

- Overlaying a simple HW cursor 32 x 32 pixels, uniform color; may be combined logically with the full plane.

- Color conversion/correction linear (multiplicative & additive) programmable including:

- YUV <-> RGB, YUV<->YUV conversions where YUV stands for any one of the color formats defined in the MPEG-4 standard

- Adjustments: brightness, contrast, color saturation, etc.

- Special effects: gray-scale, color inversion, sephia, blue-tone, etc.

- Color-preserving clipping, for gamut mapping

- Hue-preserving gamut mapping for minimal color distortion

- Applied to the output of combining or to one of the inputs

- Gamma correction and contrast stretching programmable piecewise-linear map

- Output: to display (through the DC)

- Rate: up to 240M pixels/sec

- Format: YUV/RGB, non-decimated, 8 bits/value

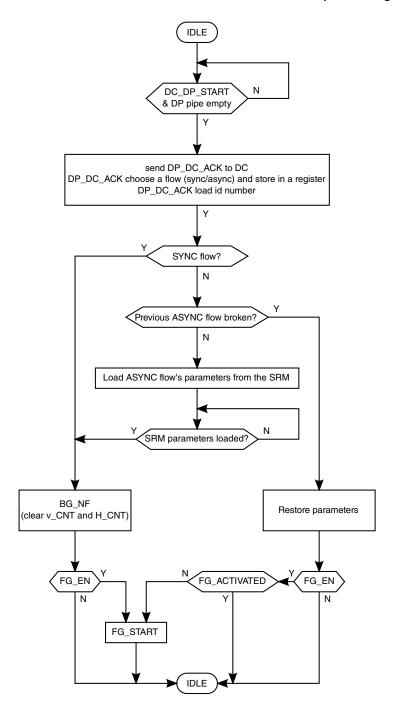

The DP processes a single data flow at any given time, but supports up to three data flows by time sharing.

- A Primary flow:

- The input is loaded periodically using a timer (e.g. for a synchronous access)

- Optionally, frames are skipped if the content has not changed (as appropriate for a smart display)

- Two secondary flows:

- Asynchronous; processed when the DP is not needed for the primary flow (during blanking intervals or when a primary frame is skipped).

- The two secondary flows are switched frame-by-frame.

# 37.1.2.1.5 Video De-Interlacer or Combiner (VDIC)

The Video De-Interlacer as well as the Combiner have two operation modes

- De-interlacing: converts an interlaced video stream to progressive order.

- Combining: combines two video/graphics planes and a background color

# 37.1.2.1.5.1 De-interlacing in the VDIC

The Video De-Interlacer converts an interlaced video stream to progressive order, using a high-quality 3-field motion-adaptive filter.

- Video source SDTV: 480i30 (720x480 @ 30 fps) or 576i25 (720x576 @ 25 fps) and HDTV: 1080i/30 (1920x1080 @ 30 fps)

- Input: -three consecutive fields

- Source

- The most recent field may come from the CSI or from system memory

- The other two fields are read from memory

- Field size: up to 968x1024 pixels (may be a vertical stripe of a wider field; e.g. 1920 pixels)

- Pixel format: YUV 4:2:2/4:2:0, 8 bits/value

- Output: progressive frame

- Destination: to system memory or to the Image Converter.

- Frame size: up to 968x2048 pixels

- Rate: up to 240 MP/sec (e.g., 1920x1080 @ 85 fps)

- Format: same as input format

The de-interlacing is performed using a high-quality 3-field filter which is motion adaptive:

- For slow motion retains the full resolution (of both top and bottom fields)

- For fast motion prevents motion artifacts

The VDIC supports a single video stream at any given time.

### 37.1.2.1.5.2 Combining in the VDIC

- Input for combining: two progressive video/graphics planes

- Source: system memory

- Plane size: up to 1920x1200 pixels.

- Pixel format: RGB/YUV 4:2:2, 8 bits/value

### In this mode:

- The two input planes are read from system memory, using the previous field and next field input FIFOs.

- Their relative height, up/down is configurable

- Each of them may cover only part of the output frame. For the remaining part of the frame, the chip uses the following values:

- Down plane: a 24-bit background color, stored in an internal register

- Up plane: a transparent pixel

- The combining method is identical to the one in the DP, IC.

# 37.1.2.1.5.3 Image Converter (IC)

The Image Converter performs various operations on a video stream.

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

- Input: from sensor or from system memory

- Frame size: up to 4096x4096 pixels

- Rate: up to 200M pixels/sec (e.g. 5 MP @ 30 fps + 35% blanking intervals)

- Order: rows, progressive. If resizing is not used, interlaced order is also acceptable.

- Pixel format: YUV/RGB, 8 bits/value

- Processing chain:

- Resizing

- Fully flexible resizing ratio Maximal downsizing ratio: 8:1. Subject to this limitation, any N->M resizing can be performed.

- Independent horizontal and vertical resizing ratios.

- Color conversion/correction linear (multiplicative & additive) programmable, including:

- YUV <-> RGB, YUV<->YUV conversions where YUV stands for any one of the color formats defined in the MPEG-4 standard

- Adjustments: brightness, contrast, color saturation...

- Special effects: gray-scale, color inversion, sephia, blue-tone...

- Combining with a graphics plane (e.g. application-specific overlay)

- Horizontal inversion

- Output: to system memory or (for a single active flow) to a display device (through the DP).

- Frame size: up to 1024x1024 pixels

- Rate: up to 100Mpixels/sec (e.g. 1920x1080 @ 30 fps)

- Order: rows, progressive. If resizing is not used, interlaced order is also acceptable.

- Format: YUV/RGB, 8 bits/value

The IC supports three time-shared data flows: record, camera preview and playback (the first two share a common input).

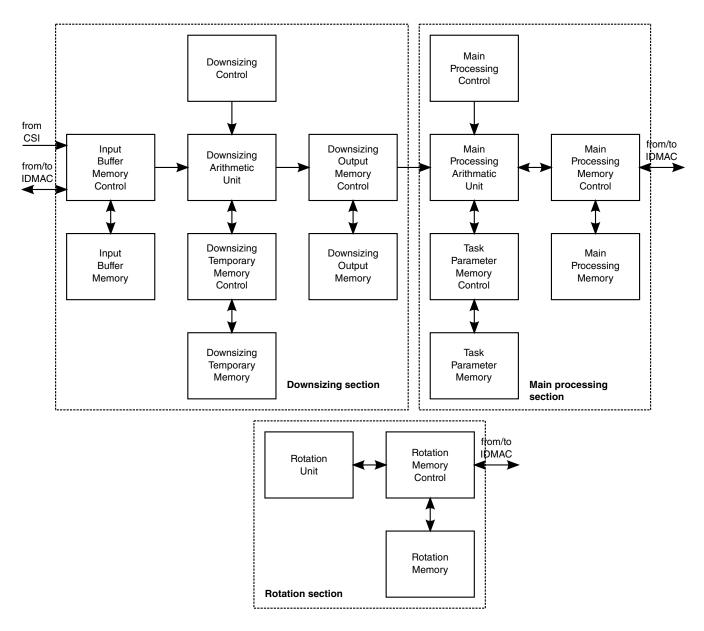

# 37.1.2.1.5.4 Image Rotator (IRT)

- Input/output: from/to system memory

- Rate

- Up to 120M pixels/sec (when a single task is active).

- Up to 100M pixels/sec (when more than one task is active).

- Order: raster scan of 8x8-pixel blocks

- Format: YUV/RGB, non-decimated, 8 bits/value

- Transformation: combination of the following

- 90-degree rotation

- Horizontal inversion

- Vertical inversion

### 37.1.2.1.6 Automatic Procedures

The IPU is equipped with powerful control and synchronization capabilities to perform its tasks with minimal involvement of the ARM Core and minimal use of memory.

In particular, it includes:

- An integrated DMA controller with an AXI master port, allowing autonomous access to the system memory.

- An integrated display controller, performing screen refresh of a RAM-less display.

- A page-flip double buffering mechanism, synchronizing read and write access to system memory, to prevent tearing effects.

- A double/triple buffer synchronization mechanism with a video/graphics source.

- Internal synchronization, e.g., between input from sensor and output to display

As a result, in most cases, the ARM platform is involved only when it also performs part of the processing (e.g. video coding). In particular, the following procedures are performed by the IPU completely autonomously:

- Screen refresh for RAM-less displays

- Update of the ("partial plane") display buffer used for screen refresh (located either in system memory or in an external display controller, e.g. of a smart display or graphics accelerator), when the content is generated in a different ("full plane") buffer.

Typically, there are extended periods of times in which there is no other activity in the system. The ARM platform, being idle, can be put to a low-power mode, reducing the power consumption and extending significantly the battery life.

The IPU supports several techniques to reduce further the power consumption of the display system:

- Dynamically optimized screen refresh rate (see Screen Refresh below)

- Optimized update of the display buffer (see Update Of The Display Buffer below)

- Dynamic backlight control, with low-light compensation by image enhancement

Further features and capabilities of the automatic procedures are outlined below

### 37.1.2.1.6.1 Screen Refresh

- The refresh rate may vary within a predefined range. Within this range, the rate is dynamically adjusted to the content update rate.

- An indication about the availability of new content is obtained as follows:

#### **External Signals**

- If the page-flip double buffering is used, the mechanism provides this indication

- If only a single buffer is used (and incrementally updated), the IPU can receive an indication of a modification from the ARM platform (by setting an internal flag).

- The IPU counts the refresh cycles: the total and those with new content. The ARM platform can use these counters to optimize display management (e.g. switching display buffer compression on/off). The counters are reset by the ARM platform.

- The transferred data may be processed on the way, using the IC and DP.

### 37.1.2.1.6.2 Update Of The Display Buffer

- Conditional update The IPU can receive an external "snooping" signal indicating a modification of the full plane buffer (as during screen refresh above). It monitors the signal and, upon detection, it performs one of the following:

- Performs an update, without any SW intervention

- Interrupts the ARM core, that can initiate some more involved procedure (e.g. selective update)

- Automatic display of a changing image (animation) or moving image (scrolling) This

is implemented by reading frames (from a full plane buffer) with incremental offset.

When the IPU reaches the last programmed frame, it can perform one of the

following:

- Return to the first frame, without any SW intervention

- Interrupt the ARM platform, to generate the next content.

- The timing of the update can be adjusted to avoid tearing.

- The transferred data may be processed on the way, using the IC and DP

### 37.1.2.1.6.3 Camera Preview

- Tearing artifacts can be prevented by (automatic) page-flip double buffering in system memory

- Alternatively, the video stream from an image sensor can be sent directly to the display buffer used for screen refresh. The significance of this option is that only a single frame buffer is needed (and not two). This buffer may be located either in system memory or in an external display controller.

- This option is useful, e.g., in a low frame rate, when tearing is not visible.

- When tearing must be prevented, the refresh cycle in the display can be synchronized with the timing signals from the sensor (two refresh cycles for each input frame): the IPU receives a VSYNC signal from the sensor and generates from it synchronization signals for the display.

# 37.2 External Signals

The table found here describes the external signals of IPU1.

Table 37-6. IPU1 External Signals

| Signal            | Description | Pad          | Mode | Direction |

|-------------------|-------------|--------------|------|-----------|

| IPU1_CSI0_DATA00  | -           | EIM_D27      | ALT2 | I         |

| IPU1_CSI0_DATA01  | -           | EIM_D26      | ALT2 | I         |

| IPU1_CSI0_DATA02  | -           | EIM_D31      | ALT3 | I         |

| IPU1_CSI0_DATA03  | -           | EIM_D30      | ALT3 | I         |

| IPU1_CSI0_DATA04  | -           | CSI0_DAT4    | ALT0 | I         |

| IPU1_CSI0_DATA05  | -           | CSI0_DAT5    | ALT0 | I         |

| IPU1_CSI0_DATA06  | -           | CSI0_DAT6    | ALT0 | I         |

| IPU1_CSI0_DATA07  | -           | CSI0_DAT7    | ALT0 | I         |

| IPU1_CSI0_DATA08  | -           | CSI0_DAT8    | ALT0 | I         |

| IPU1_CSI0_DATA09  | -           | CSI0_DAT9    | ALT0 | I         |

| IPU1_CSI0_DATA10  | -           | CSI0_DAT10   | ALT0 | I         |

| IPU1_CSI0_DATA11  | -           | CSI0_DAT11   | ALT0 | I         |

| IPU1_CSI0_DATA12  | -           | CSI0_DAT12   | ALT0 | I         |

| IPU1_CSI0_DATA13  | -           | CSI0_DAT13   | ALT0 | I         |

| IPU1_CSI0_DATA14  | -           | CSI0_DAT14   | ALT0 | I         |

| IPU1_CSI0_DATA15  | -           | CSI0_DAT15   | ALT0 | I         |

| IPU1_CSI0_DATA16  | -           | CSI0_DAT16   | ALT0 | I         |

| IPU1_CSI0_DATA17  | -           | CSI0_DAT17   | ALT0 | I         |

| IPU1_CSI0_DATA18  | -           | CSI0_DAT18   | ALT0 | I         |

| IPU1_CSI0_DATA19  | -           | CSI0_DAT19   | ALT0 | I         |

| IPU1_CSI0_DATA_EN | -           | CSI0_DATA_EN | ALT0 | I         |

| IPU1_CSI0_HSYNC   | -           | CSI0_MCLK    | ALT0 | I         |

| IPU1_CSI0_PIXCLK  | -           | CSI0_PIXCLK  | ALT0 | I         |

| IPU1_CSI0_VSYNC   | -           | CSI0_VSYNC   | ALT0 | I         |

| IPU1_DI0_D0_CS    | -           | EIM_D23      | ALT1 | 0         |

| IPU1_DI0_D1_CS    | -           | EIM_A25      | ALT4 | 0         |

| IPU1_DI0_DISP_CLK | -           | DI0_DISP_CLK | ALT0 | 0         |

| IPU1_DI0_PIN01    | -           | EIM_D22      | ALT2 | Ю         |

| IPU1_DI0_PIN02    | -           | DI0_PIN2     | ALT0 | 0         |

| IPU1_DI0_PIN03    | -           | DI0_PIN3     | ALT0 | 0         |

| IPU1_DI0_PIN04    | -           | DI0_PIN4     | ALT0 | 0         |

| IPU1_DI0_PIN05    | -           | EIM_D16      | ALT2 | 0         |

| IPU1_DI0_PIN06    | -           | EIM_D17      | ALT2 | 0         |

| IPU1_DI0_PIN07    | -           | EIM_D18      | ALT2 | 0         |

| IPU1_DI0_PIN08    | -           | EIM_D19      | ALT2 | 0         |

| IPU1_DI0_PIN11    | _           | EIM_D30      | ALT2 | 0         |

### **External Signals**

Table 37-6. IPU1 External Signals (continued)

| Signal              | Description | Pad         | Mode | Direction |

|---------------------|-------------|-------------|------|-----------|

| IPU1_DI0_PIN12 -    |             | EIM_D31     | ALT2 | 0         |

| IPU1_DI0_PIN13 -    |             | EIM_D28     | ALT7 | 0         |

| IPU1_DI0_PIN14 -    |             | EIM_D29     | ALT7 | 0         |

| IPU1_DI0_PIN15 -    |             | DI0_PIN15   | ALT0 | 0         |

| IPU1_DI0_PIN16 -    |             | EIM_D20     | ALT2 | 0         |

| IPU1_DI0_PIN17 -    |             | EIM_D21     | ALT2 | 0         |

| IPU1_DI1_D0_CS      |             | EIM_DA13    | ALT1 | 0         |

|                     |             | EIM_D18     | ALT4 |           |

| IPU1_DI1_D1_CS -    |             | EIM_DA14    | ALT1 | 0         |

| IPU1_DI1_DISP_CLK - |             | EIM_A16     | ALT1 | 0         |

| IPU1_DI1_PIN01 -    |             | EIM_DA15    | ALT1 | Ю         |

| IPU1_DI1_PIN02      |             | EIM_DA11    | ALT1 | 0         |

|                     |             | EIM_D23     | ALT6 |           |

| IPU1_DI1_PIN03      |             | EIM_DA12    | ALT1 | 0         |

|                     |             | EIM_EB3     | ALT6 |           |

| IPU1_DI1_PIN04 -    |             | EIM_DA15    | ALT2 | 0         |

| IPU1_DI1_PIN05 -    |             | EIM_CS0     | ALT1 | 0         |

| IPU1_DI1_PIN06 -    |             | EIM_CS1     | ALT1 | 0         |

| IPU1_DI1_PIN07 -    |             | EIM_OE      | ALT1 | 0         |

| IPU1_DI1_PIN08 -    |             | EIM_RW      | ALT1 | 0         |

| IPU1_DI1_PIN11 -    |             | EIM_D26     | ALT1 | 0         |

| IPU1_DI1_PIN12 -    |             | EIM_A25     | ALT3 | 0         |

| IPU1_DI1_PIN13 -    |             | EIM_D27     | ALT1 | 0         |

| IPU1_DI1_PIN14 -    |             | EIM_D23     | ALT7 | 0         |

| IPU1_DI1_PIN15      |             | EIM_DA10    | ALT1 | 0         |

|                     |             | EIM_D29     | ALT1 |           |

| IPU1_DI1_PIN16 -    |             | EIM_BCLK    | ALT1 | 0         |

| IPU1_DI1_PIN17 -    |             | EIM_LBA     | ALT1 | 0         |

| IPU1_DISP0_DATA00 - |             | DISP0_DAT0  | ALT0 | IO        |

| IPU1_DISP0_DATA01 - |             | DISP0_DAT1  | ALT0 | IO        |

| IPU1_DISP0_DATA02 - |             | DISP0_DAT2  | ALT0 | IO        |

| IPU1_DISP0_DATA03 - |             | DISP0_DAT3  | ALT0 | IO        |

| IPU1_DISP0_DATA04 - |             | DISP0_DAT4  | ALT0 | IO        |

| IPU1_DISP0_DATA05 - |             | DISP0_DAT5  | ALT0 | IO        |

| IPU1_DISP0_DATA06 - |             | DISP0_DAT6  | ALT0 | IO        |

| IPU1_DISP0_DATA07 - |             | DISP0_DAT7  | ALT0 | IO        |

| IPU1_DISP0_DATA08 - |             | DISP0_DAT8  | ALT0 | IO        |

| IPU1_DISP0_DATA09 - |             | DISP0_DAT9  | ALT0 | IO        |

| IPU1_DISP0_DATA10 - |             | DISP0_DAT10 | ALT0 | IO        |

Table 37-6. IPU1 External Signals (continued)

| Signal              | Description | Pad         | Mode | Direction |

|---------------------|-------------|-------------|------|-----------|

| IPU1_DISP0_DATA11 - |             | DISP0_DAT11 | ALT0 | Ю         |

| IPU1_DISP0_DATA12 - |             | DISP0_DAT12 | ALT0 | Ю         |

| IPU1_DISP0_DATA13 - |             | DISP0_DAT13 | ALT0 | Ю         |

| IPU1_DISP0_DATA14 - |             | DISP0_DAT14 | ALT0 | Ю         |

| IPU1_DISP0_DATA15 - |             | DISP0_DAT15 | ALT0 | Ю         |

| IPU1_DISP0_DATA16 - |             | DISP0_DAT16 | ALT0 | IO        |

| IPU1_DISP0_DATA17 - |             | DISP0_DAT17 | ALT0 | Ю         |

| IPU1_DISP0_DATA18 - |             | DISP0_DAT18 | ALT0 | IO        |

| IPU1_DISP0_DATA19 - |             | DISP0_DAT19 | ALT0 | Ю         |

| IPU1_DISP0_DATA20 - |             | DISP0_DAT20 | ALT0 | Ю         |

| IPU1_DISP0_DATA21 - |             | DISP0_DAT21 | ALT0 | Ю         |

| IPU1_DISP0_DATA22 - |             | DISP0_DAT22 | ALT0 | Ю         |

| IPU1_DISP0_DATA23 - |             | DISP0_DAT23 | ALT0 | Ю         |

| IPU1_DISP1_DATA00 - |             | EIM_DA9     | ALT1 | Ю         |

| IPU1_DISP1_DATA01 - |             | EIM_DA8     | ALT1 | IO        |

| IPU1_DISP1_DATA02 - |             | EIM_DA7     | ALT1 | Ю         |

| IPU1_DISP1_DATA03 - |             | EIM_DA6     | ALT1 | Ю         |

| IPU1_DISP1_DATA04 - |             | EIM_DA5     | ALT1 | Ю         |

| IPU1_DISP1_DATA05 - |             | EIM_DA4     | ALT1 | Ю         |

| IPU1_DISP1_DATA06 - |             | EIM_DA3     | ALT1 | IO        |

| IPU1_DISP1_DATA07 - |             | EIM_DA2     | ALT1 | Ю         |

| IPU1_DISP1_DATA08 - |             | EIM_DA1     | ALT1 | Ю         |

| IPU1_DISP1_DATA09 - |             | EIM_DA0     | ALT1 | Ю         |

| IPU1_DISP1_DATA10 - |             | EIM_EB1     | ALT1 | IO        |

| IPU1_DISP1_DATA11 - |             | EIM_EB0     | ALT1 | IO        |

| IPU1_DISP1_DATA12 - |             | EIM_A17     | ALT1 | IO        |

| IPU1_DISP1_DATA13 - |             | EIM_A18     | ALT1 | Ю         |

| IPU1_DISP1_DATA14 - |             | EIM_A19     | ALT1 | IO        |

| IPU1_DISP1_DATA15 - |             | EIM_A20     | ALT1 | Ю         |

| IPU1_DISP1_DATA16 - |             | EIM_A21     | ALT1 | IO        |

| IPU1_DISP1_DATA17 - |             | EIM_A22     | ALT1 | Ю         |

| IPU1_DISP1_DATA18 - |             | EIM_A23     | ALT1 | IO        |

| IPU1_DISP1_DATA19 - |             | EIM_A24     | ALT1 | IO        |

| IPU1_DISP1_DATA20 - |             | EIM_D31     | ALT1 | IO        |

| IPU1_DISP1_DATA21 - |             | EIM_D30     | ALT1 | IO        |

| IPU1_DISP1_DATA22 - |             | EIM_D26     | ALT7 | IO        |

| IPU1_DISP1_DATA23 - |             | EIM_D27     | ALT7 | Ю         |

| IPU1_EXT_TRIG -     |             | EIM_D28     | ALT6 | I         |

| IPU1_SISG0 -        |             | NANDF_CS2   | ALT1 | 0         |

### **External Signals**

# Table 37-6. IPU1 External Signals (continued)

| Signal     | Description | Pad       | Mode | Direction |

|------------|-------------|-----------|------|-----------|

| IPU1_SISG1 | -           | NANDF_CS3 | ALT1 | 0         |

| IPU1_SISG2 |             | EIM_A24   | ALT4 | 0         |

|            |             | EIM_D26   | ALT6 |           |

| IPU1_SISG3 |             | EIM_A23   | ALT4 | 0         |

|            |             | EIM_D27   | ALT6 |           |

| IPU1_SISG4 | -           | KEY_COL4  | ALT1 | 0         |

| IPU1_SISG5 | -           | KEY_ROW4  | ALT1 | 0         |

# Table 37-7. IPU2 External Signals

| Signal           | Description | Pad     | Mode | Direction |

|------------------|-------------|---------|------|-----------|

| IPU2_CSI1_DATA00 | -           | EIM_DA9 | ALT2 | I         |

| IPU2_CSI1_DATA01 | -           | EIM_DA8 | ALT2 | I         |

| IPU2_CSI1_DATA02 | -           | EIM_DA7 | ALT2 | I         |

| IPU2_CSI1_DATA03 | -           | EIM_DA6 | ALT2 | I         |

| IPU2_CSI1_DATA04 | -           | EIM_DA5 | ALT2 | I         |

| IPU2_CSI1_DATA05 | -           | EIM_DA4 | ALT2 | I         |

| IPU2_CSI1_DATA06 | -           | EIM_DA3 | ALT2 | I         |

| IPU2_CSI1_DATA07 | -           | EIM_DA2 | ALT2 | I         |

| IPU2_CSI1_DATA08 | -           | EIM_DA1 | ALT2 | I         |

| IPU2_CSI1_DATA09 | -           | EIM_DA0 | ALT2 | I         |

| IPU2_CSI1_DATA10 |             | EIM_D22 | ALT3 | I         |

|                  |             | EIM_EB1 | ALT2 |           |

| IPU2_CSI1_DATA11 |             | EIM_D21 | ALT3 | I         |

|                  |             | EIM_EB0 | ALT2 |           |

| IPU2_CSI1_DATA12 |             | EIM_A17 | ALT2 | I         |

|                  |             | EIM_D28 | ALT3 |           |

| IPU2_CSI1_DATA13 |             | EIM_A18 | ALT2 | I         |

|                  |             | EIM_D27 | ALT3 |           |

| IPU2_CSI1_DATA14 |             | EIM_A19 | ALT2 | I         |

|                  |             | EIM_D26 | ALT3 |           |

| IPU2_CSI1_DATA15 |             | EIM_A20 | ALT2 | I         |

|                  |             | EIM_D20 | ALT3 |           |

| IPU2_CSI1_DATA16 |             | EIM_A21 | ALT2 | I         |

|                  |             | EIM_D19 | ALT3 |           |

| IPU2_CSI1_DATA17 |             | EIM_A22 | ALT2 | I         |

|                  |             | EIM_D18 | ALT3 |           |

| IPU2_CSI1_DATA18 |             | EIM_A23 | ALT2 | I         |

|                  |             | EIM_D16 | ALT3 |           |

Table 37-7. IPU2 External Signals (continued)

| Signal            | Description | Pad          | Mode | Direction |

|-------------------|-------------|--------------|------|-----------|

| IPU2_CSI1_DATA19  |             | EIM_A24      | ALT2 | ı         |

|                   |             | EIM_EB2      | ALT3 | -         |

| IPU2_CSI1_DATA_EN |             | EIM_DA10     | ALT2 | I         |

|                   |             | EIM_D23      | ALT4 | -         |

| IPU2_CSI1_HSYNC   |             | EIM_DA11     | ALT2 | I         |

|                   |             | EIM_EB3      | ALT4 | -         |

| IPU2_CSI1_PIXCLK  |             | EIM_A16      | ALT2 | I         |

|                   |             | EIM_D17      | ALT3 | 1         |

| IPU2_CSI1_VSYNC   |             | EIM_DA12     | ALT2 | I         |

|                   |             | EIM_D29      | ALT6 | -         |

| IPU2_DI0_DISP_CLK | -           | DI0_DISP_CLK | ALT1 | 0         |

| IPU2_DI0_PIN01    | -           | NANDF_RB0    | ALT1 | Ю         |

| IPU2_DI0_PIN02    | -           | DI0_PIN2     | ALT1 | 0         |

| IPU2_DI0_PIN03    | -           | DI0_PIN3     | ALT1 | 0         |

| IPU2_DI0_PIN04    | -           | DI0_PIN4     | ALT1 | 0         |

| IPU2_DI0_PIN15    | -           | DI0_PIN15    | ALT1 | 0         |

| IPU2_DISP0_DATA00 | -           | DISP0_DAT0   | ALT1 | Ю         |

| IPU2_DISP0_DATA01 | -           | DISP0_DAT1   | ALT1 | Ю         |

| IPU2_DISP0_DATA02 | -           | DISP0_DAT2   | ALT1 | Ю         |

| IPU2_DISP0_DATA03 | -           | DISP0_DAT3   | ALT1 | Ю         |

| IPU2_DISP0_DATA04 | -           | DISP0_DAT4   | ALT1 | Ю         |

| IPU2_DISP0_DATA05 | -           | DISP0_DAT5   | ALT1 | Ю         |

| IPU2_DISP0_DATA06 | -           | DISP0_DAT6   | ALT1 | Ю         |

| IPU2_DISP0_DATA07 | -           | DISP0_DAT7   | ALT1 | Ю         |

| IPU2_DISP0_DATA08 | -           | DISP0_DAT8   | ALT1 | Ю         |

| IPU2_DISP0_DATA09 | -           | DISP0_DAT9   | ALT1 | Ю         |

| IPU2_DISP0_DATA10 | -           | DISP0_DAT10  | ALT1 | Ю         |

| IPU2_DISP0_DATA11 | -           | DISP0_DAT11  | ALT1 | Ю         |

| IPU2_DISP0_DATA12 | -           | DISP0_DAT12  | ALT1 | Ю         |

| IPU2_DISP0_DATA13 | -           | DISP0_DAT13  | ALT1 | Ю         |

| IPU2_DISP0_DATA14 | -           | DISP0_DAT14  | ALT1 | Ю         |

| IPU2_DISP0_DATA15 | -           | DISP0_DAT15  | ALT1 | Ю         |

| IPU2_DISP0_DATA16 | -           | DISP0_DAT16  | ALT1 | Ю         |

| IPU2_DISP0_DATA17 | -           | DISP0_DAT17  | ALT1 | Ю         |

| IPU2_DISP0_DATA18 | -           | DISP0_DAT18  | ALT1 | Ю         |

| IPU2_DISP0_DATA19 | -           | DISP0_DAT19  | ALT1 | Ю         |

| IPU2_DISP0_DATA20 | -           | DISP0_DAT20  | ALT1 | Ю         |

| IPU2_DISP0_DATA21 | -           | DISP0_DAT21  | ALT1 | Ю         |

| IPU2_DISP0_DATA22 | -           | DISP0_DAT22  | ALT1 | Ю         |

#### Clocks

Table 37-7. IPU2 External Signals (continued)

| Signal            | Description | Pad         | Mode | Direction |

|-------------------|-------------|-------------|------|-----------|

| IPU2_DISP0_DATA23 | -           | DISP0_DAT23 | ALT1 | Ю         |

| IPU2_SISG0        | -           | NANDF_CS2   | ALT6 | 0         |

| IPU2_SISG1        | -           | NANDF_CS3   | ALT6 | 0         |

| IPU2_SISG2        | -           | EIM_A24     | ALT3 | 0         |

| IPU2_SISG3        | -           | EIM_A23     | ALT3 | 0         |

| IPU2_SISG4        | -           | NANDF_CLE   | ALT1 | 0         |

| IPU2_SISG5        | -           | NANDF_WP_B  | ALT1 | 0         |

# 37.3 Clocks

The table found here describes the clock sources for IPU.

Please see Clock Controller Module (CCM) for clock setting, configuration and gating information.

Table 37-8. IPU Clocks

| Clock name       | Clock Root            | Description                   |

|------------------|-----------------------|-------------------------------|

| hsp_clk          | ipu1_ipu_hsp_clk_root | HSP clock                     |

| ipp_di_0_ext_clk | ipu1_di0_clk_root     | IPU DI0 interface pixel clock |

| ipp_di_1_ext_clk | ipu1_di1_clk_root     | IPU DI1 interface pixel clock |

| ipu_master_hclk  | ahb_clk_root          | IPU master clock              |

# 37.4 Functional Description

This section provides a complete functional description of the block.

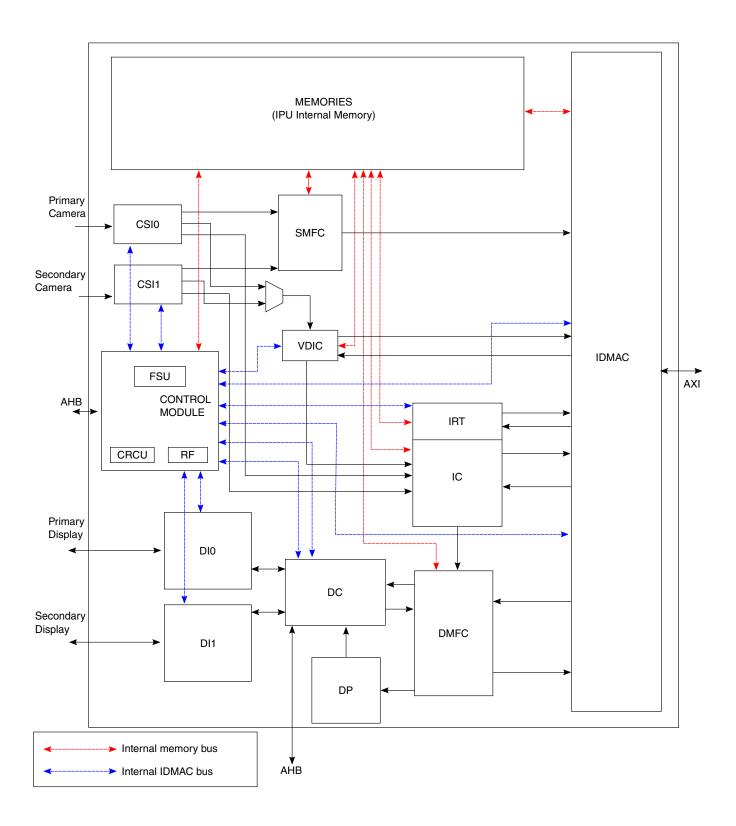

# 37.4.1 IPU detailed block diagram

The following figure is the IPU top level block diagram.

Figure 37-2. IPU Detailed Block Diagram

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

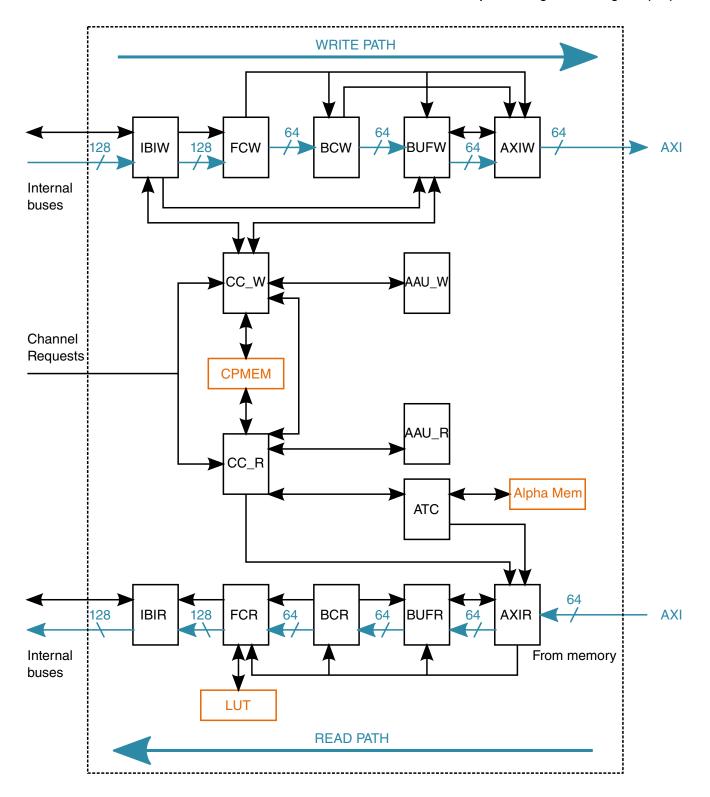

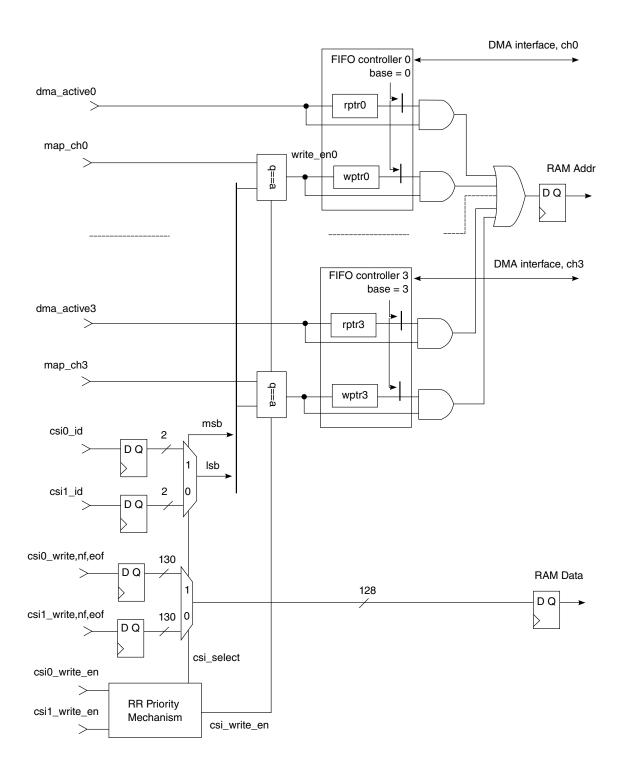

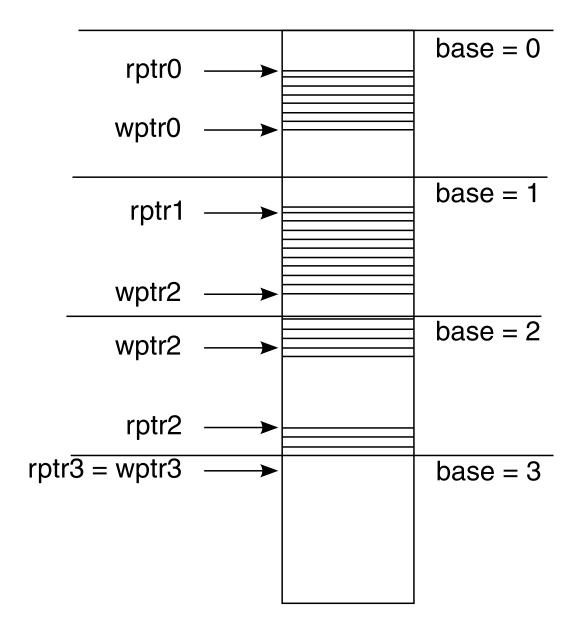

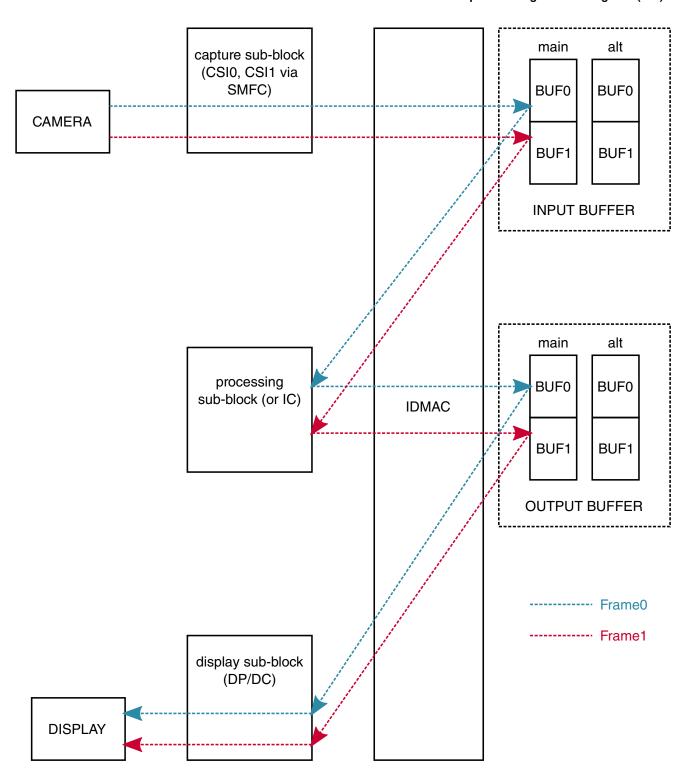

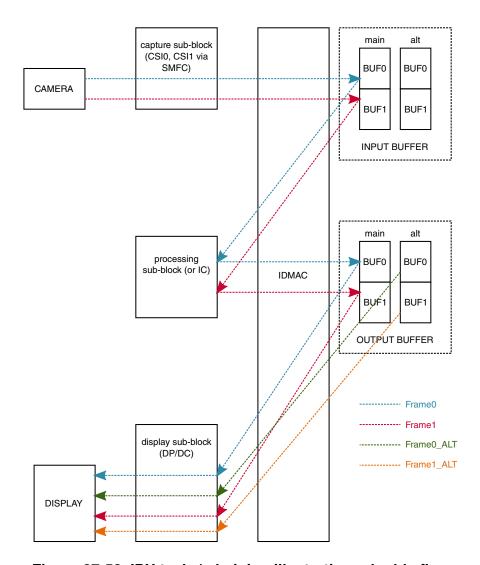

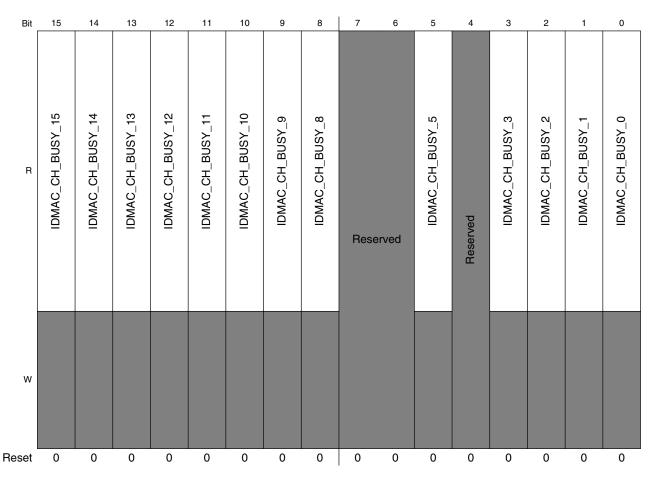

# 37.4.2 Image DMA Controller (IDMAC)

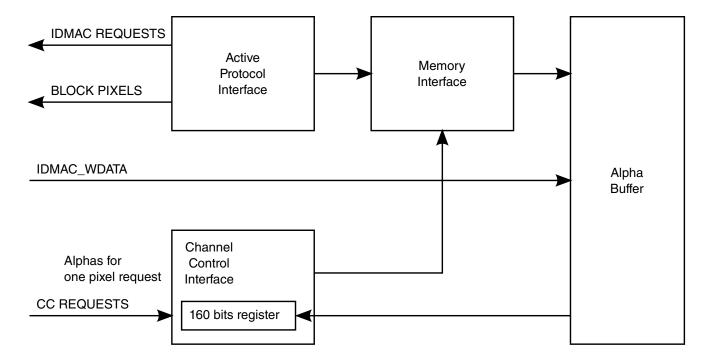

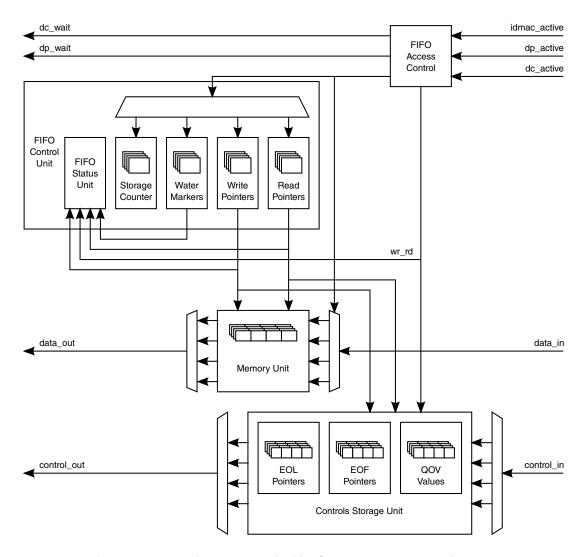

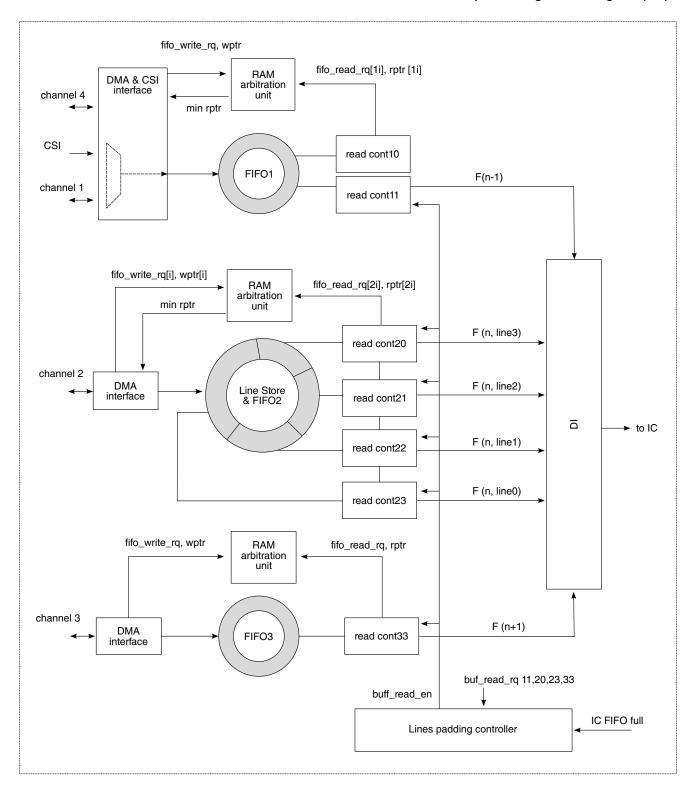

The following diagram is the IDMAC's block diagram.

Figure 37-3. IDMAC Block Diagram

The following table describes the IDMAC's sub-block glossary

#### **Functional Description**

Table 37-9. IDMAC's sub modules glossary

| Sub Module | Description                   |

|------------|-------------------------------|

| IBIW       | Internal Bus Interface Write  |

| IBIR       | Internal Bus Interface Read   |

| FCW        | Format Converter Write        |

| FCR        | Format Converter Read         |

| BCW        | Buffer Controller Write       |

| BCR        | Buffer Controller Read        |

| BUFW       | Buffer Write                  |

| BUFR       | Buffer Read                   |

| AXIW       | AXI Write                     |

| AXIR       | AXI Read                      |

| CC_W       | Channel Control Write         |

| CC_R       | Channel Control Read          |

| AAU_W      | Address Arithmetic Unit Write |

| AAU_R      | Address Arithmetic Unit Read  |

| ATC        | Alpha Transparency Controller |

| LUT        | Look up table                 |

| СРМЕМ      | Channel Parameter Memory      |

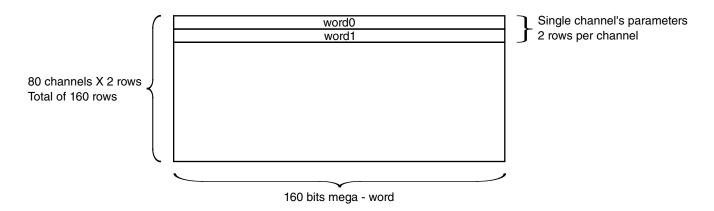

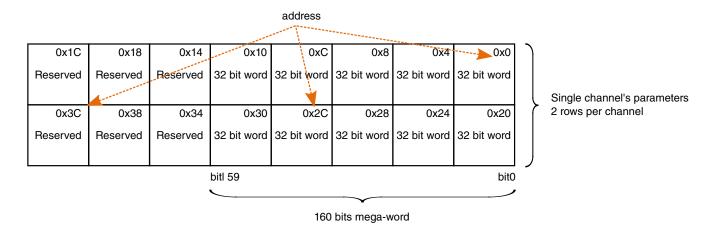

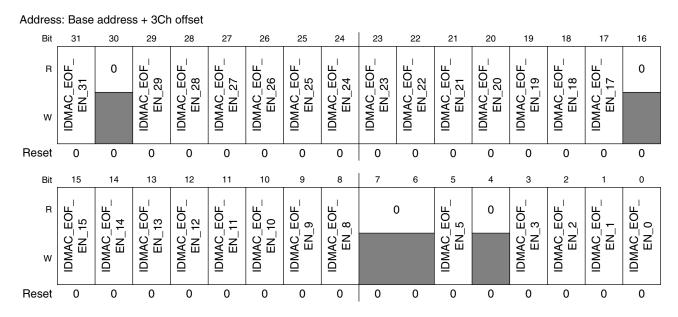

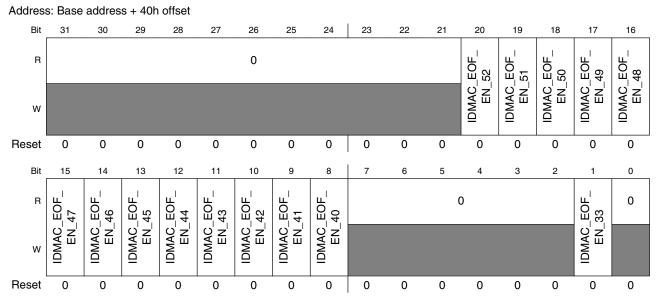

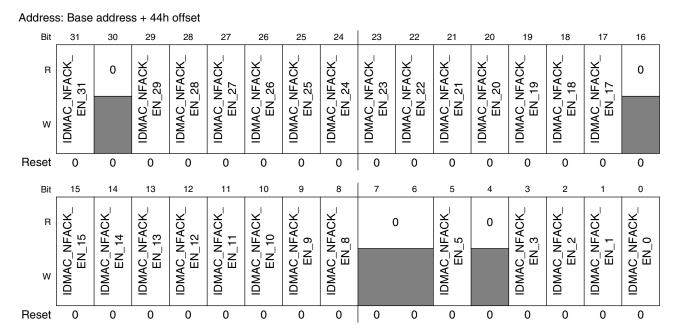

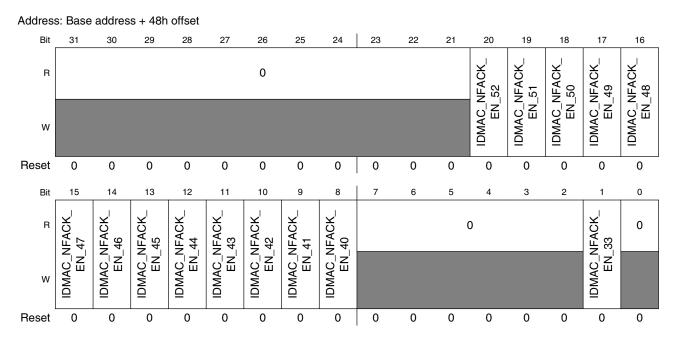

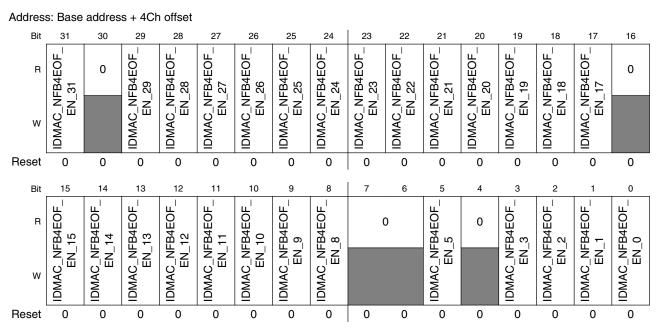

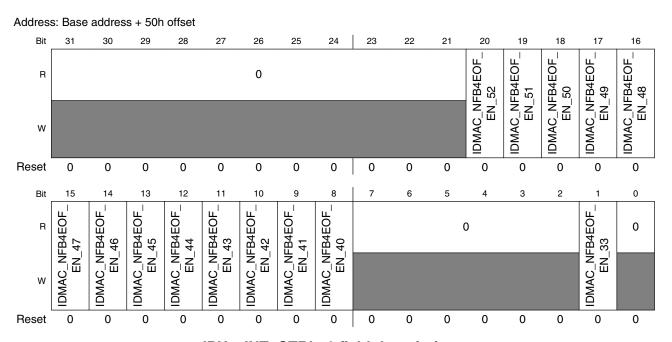

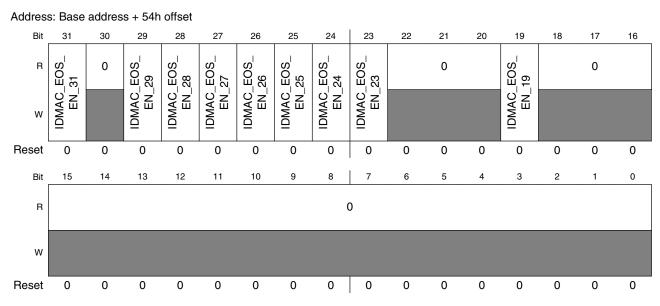

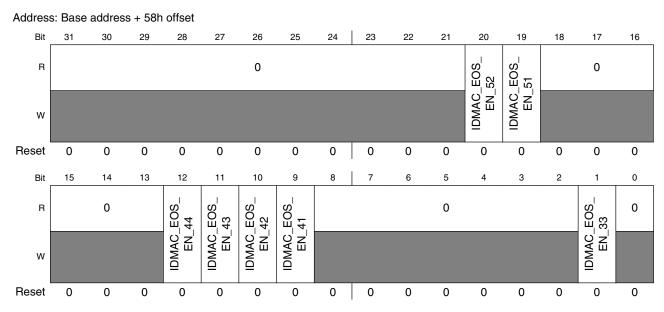

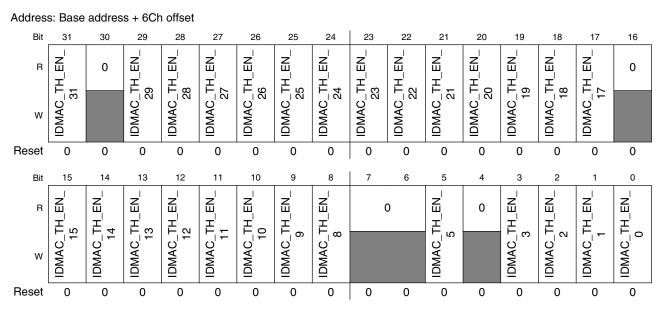

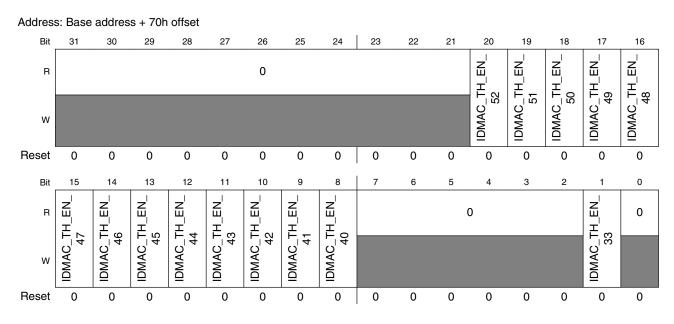

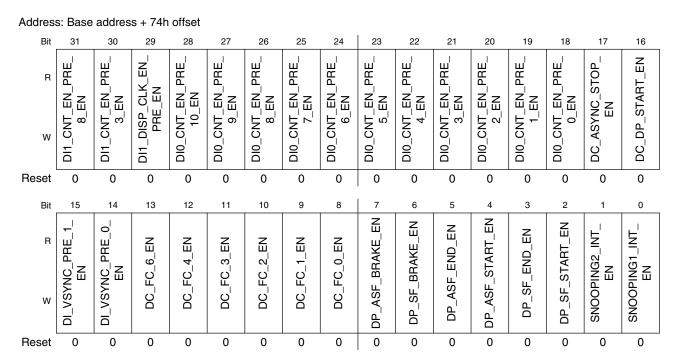

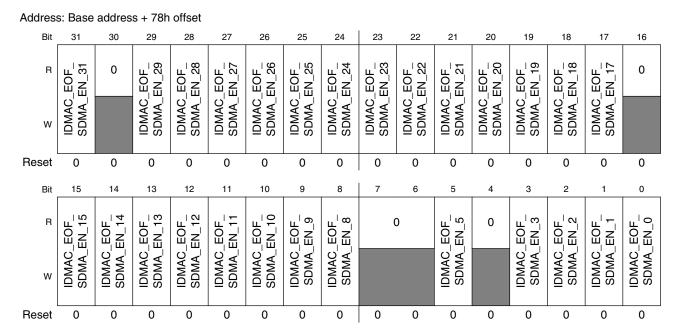

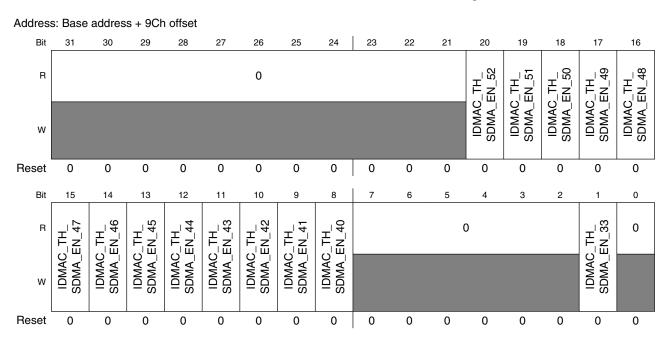

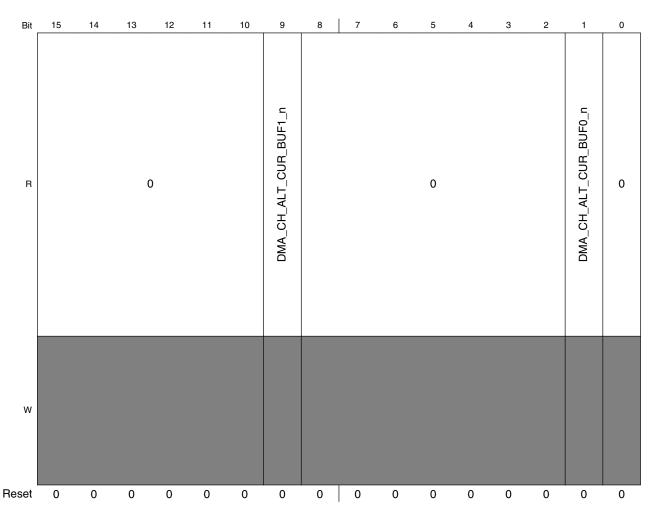

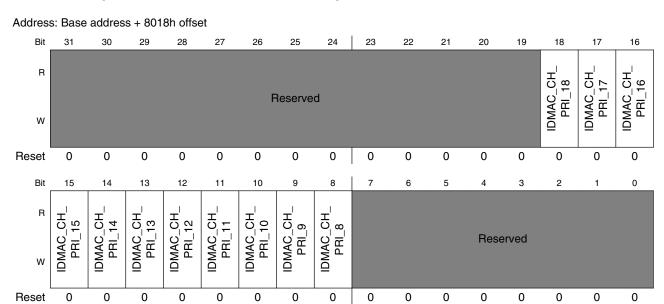

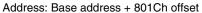

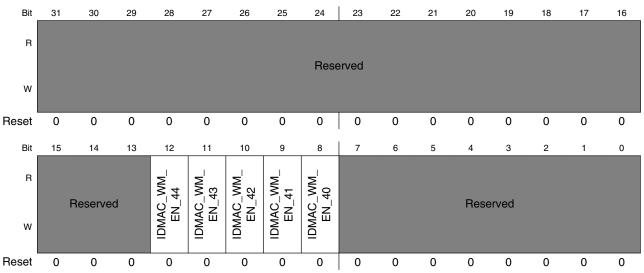

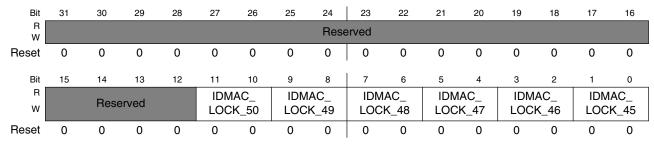

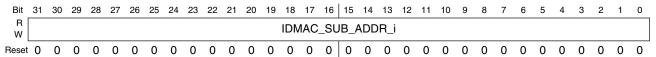

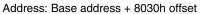

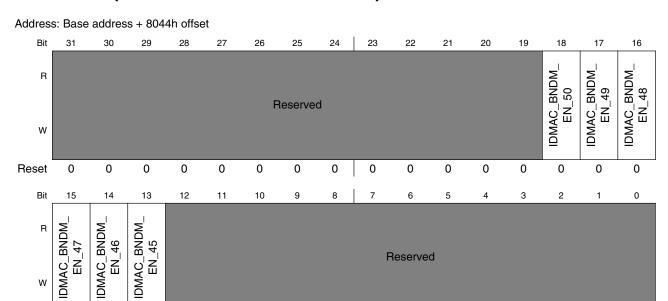

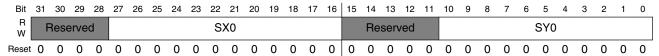

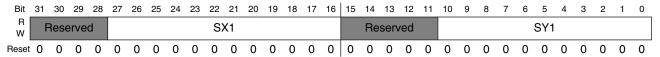

# 37.4.2.1 IDMAC's channels

The table below summarizes the IDMAC's channels.

Enabling a channel is done via the channel's corresponding IDMAC\_CH\_EN bit.

Table 37-10. IDMAC DMA channels list

| Channel<br># | Source            | Destination | Alternate<br>Destination | Purpose                                            | Data type           |

|--------------|-------------------|-------------|--------------------------|----------------------------------------------------|---------------------|

| 0            | CSI (via<br>SMFC) | Fmem        |                          | VF2 - Bayer; BPP>8; JPEG; MIPI additional channels | Generic or<br>Pixel |

| 1            | CSI (via<br>SMFC) | Fmem        |                          | VF2 - Bayer; BPP>8; JPEG; MIPI additional channels | Generic or<br>Pixel |

| 2            | CSI (via<br>SMFC) | Fmem        |                          | VF2 - Bayer; BPP>8; JPEG; MIPI additional channels | Generic or<br>Pixel |

| 3            | CSI (via<br>SMFC) | Fmem        |                          | VF2 - Bayer; BPP>8; JPEG; MIPI additional channels | Generic or<br>Pixel |

| 5            | VDIC              | Bmem        | IC                       | VF1/VF2                                            | Pixel               |

| 8            | Fmem              | VDIC        |                          | Previous field                                     | Pixel               |

| 9            | Fmem              | VDIC        |                          | Current field                                      | Pixel               |

| 10           | Fmem              | VDIC        |                          | Next field                                         | Pixel               |

Table 37-10. IDMAC DMA channels list (continued)

| Channel<br># | Source   | Destination | Alternate<br>Destination | Purpose                                                                                                                                                                        | Data type |

|--------------|----------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 11           | Bmem     | IC          |                          | video plane for post processing task                                                                                                                                           | Pixel     |

| 12           | Bmem     | IC          |                          | video plane for PrP tasks (view finder or encoding)                                                                                                                            | Pixel     |

| 13           | VDIC     | Fmem        |                          | Recent field from CSI                                                                                                                                                          | Pixel     |

| 14           | Fmem     | IC          |                          | graphics plane for PrP task (view finder or encoding)                                                                                                                          | Pixel     |

| 15           | Fmem     | IC          |                          | graphics plane for post processing task                                                                                                                                        | Pixel     |

| 16           | Reserved |             |                          |                                                                                                                                                                                |           |

| 17           | Fmem     | IC          |                          | Transparency (alpha for channel 14)                                                                                                                                            | Generic   |

| 18           | Fmem     | IC          |                          | Transparency (alpha for channel 15)                                                                                                                                            | Generic   |

| 19           | Fmem     | VDIC        |                          | Transparency (alpha for channel 25)                                                                                                                                            | Generic   |

| 20           | IC       | Bmem        |                          | Preprocessing data from IC (encoding task) to memory                                                                                                                           | Pixel     |

| 21           | IC       | Bmem        | DMFC                     | Preprocessing data from IC (viewfinder task) to memory; This channel can be configured to send the data directly to the DMFC. This is done by programming the IC_DMFC_SEL bit. | Pixel     |

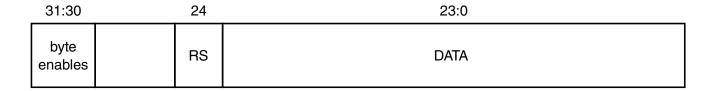

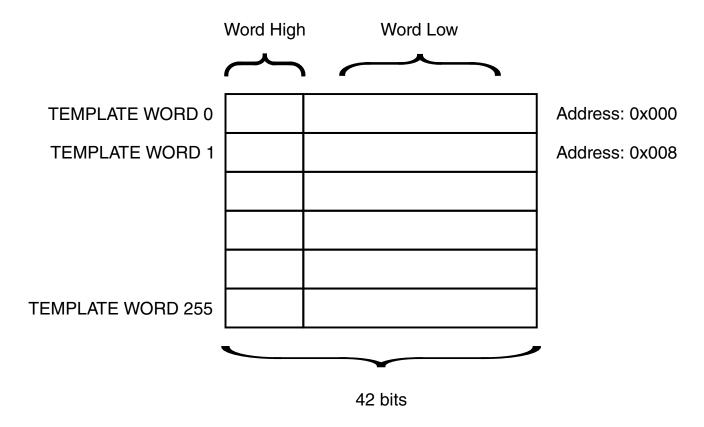

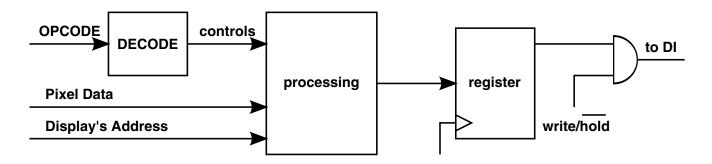

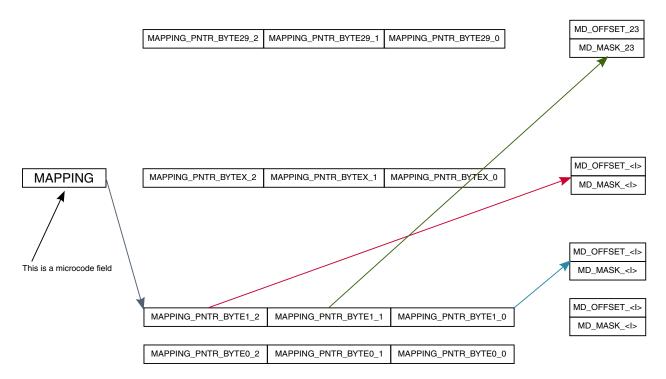

| 22           | IC       | Bmem        |                          | Postprocessing data from IC to memory                                                                                                                                          | Pixel     |