### Intel<sup>®</sup> I/O Controller Hub 6 (ICH6) High Definition Audio / AC '97

**Programmer's Reference Manual (PRM)**

May 2005

Document Number: 302349-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The High Definition Audio/AC'97 Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004 - 2005, Intel Corporation

# int<sub>el®</sub> Contents

| 1 | AC ' | 97 Progr             | amming I              | Nodel                                                         | 17 |

|---|------|----------------------|-----------------------|---------------------------------------------------------------|----|

|   | 1.1  | Intel <sup>®</sup> I | CH6: AC '             | 97 Software                                                   | 17 |

|   |      | 1.1.1                | Introduct             | ion                                                           | 18 |

|   |      | 1.1.2                |                       | ۷                                                             |    |

|   |      | 1.1.3                | Intel <sup>®</sup> IC | H6 AC '97 Controller Compatibility                            | 21 |

|   |      |                      | 1.1.3.1               | AC '97 Component Specification 2.1, 2.2, 2.3 Compliant Codecs |    |

|   |      |                      | 1.1.3.2               | Dedicated S/P DIF DMA Output Channel                          | 21 |

|   |      |                      | 1.1.3.3               | 20 Bits Surround PCM Output                                   |    |

|   |      |                      | 1.1.3.4               | Memory Map Status and Control Registers                       |    |

|   |      |                      | 1.1.3.5               | Second Independent Input DMA Engines                          |    |

|   |      |                      | 1.1.3.6               | PCI Local Bus Specification, Revision 2.2 Power Management    |    |

|   |      | 1.1.4                |                       | Requirements                                                  |    |

|   | 1.2  |                      |                       | 97 Controller Theory of Operation                             |    |

|   |      | 1.2.1                |                       | H6 AC '97 Initialization                                      |    |

|   |      |                      | 1.2.1.1               | System Reset                                                  |    |

|   |      |                      | 1.2.1.2               | Codec Topology                                                |    |

|   |      |                      | 1.2.1.3               | BIOS PCI Configuration                                        |    |

|   |      | 4.0.0                | 1.2.1.4               | Hardware Interrupt Routing                                    |    |

|   |      | 1.2.2                |                       | gines                                                         |    |

|   |      |                      | 1.2.2.1               | Buffer Descriptor List                                        |    |

|   |      |                      | 1.2.2.2<br>1.2.2.3    | DMA Initialization<br>DMA Steady State Operation              |    |

|   |      |                      | 1.2.2.3               | Stopping Transfers                                            |    |

|   |      | 1.2.3                |                       | Arbitration                                                   |    |

|   |      | 1.2.3                |                       | Firs                                                          |    |

|   |      | 1.2.4                | 1.2.4.1               | Memory Organization of Data                                   |    |

|   |      |                      | 1.2.4.1               | PCM Buffer Restrictions                                       | 31 |

|   |      |                      | 1.2.4.3               | FIFO Organization                                             |    |

|   |      | 1.2.5                |                       | Codec/Driver Support                                          |    |

|   |      |                      | 1.2.5.1               | Codec Register Read                                           |    |

|   |      |                      | 1.2.5.2               | Codec Access Synchronization                                  |    |

|   |      |                      | 1.2.5.3               | Data Request Synchronization in Audio Split Configurations    | 35 |

|   |      | 1.2.6                | Power M               | lanagement                                                    |    |

|   |      |                      | 1.2.6.1               | Power Management Transition Maps                              |    |

|   |      |                      | 1.2.6.2               | Power Management Topology Considerations                      |    |

|   |      |                      | 1.2.6.3               | Resume Context Recovery                                       |    |

|   |      |                      | 1.2.6.4               | Aggressive Power Management                                   | 40 |

|   | 1.3  | Surrou               |                       | Support                                                       |    |

|   |      | 1.3.1                |                       | ne Codec's Audio Channels                                     |    |

|   |      | 1.3.2                | Enabling              | Intel <sup>®</sup> ICH6 AC '97 Controller Audio Channels      | 44 |

|   | 1.4  |                      |                       | port                                                          |    |

|   | 1.5  |                      |                       | /DIF Output Capability                                        |    |

|   | 1.6  |                      |                       | ole Rate Audio                                                |    |

|   | 1.7  | Indepe               | ndent Inpu            | ut Channels Capability                                        | 47 |

|   |      | 1.7.1                |                       | ology Determination                                           |    |

|   | 1.8  | Intel <sup>®</sup> I |                       | 97 Modem Driver                                               | 49 |

|   |      | 1.8.1                |                       | lost Based Generation of a Synchronous                        |    |

|   |      |                      | Data Stre             | eam                                                           | 49 |

|   |      |          | 1.8.1.1       Spurious Data Algorithm         1.8.1.2       Intel <sup>®</sup> ICH6 AC '97 Spurious Data Implementation |    |

|---|------|----------|-------------------------------------------------------------------------------------------------------------------------|----|

| 2 | AC ' | 97 Audio | o Controller Registers (D30:F2)                                                                                         | 53 |

|   | 2.1  |          | Audio PCI Configuration Space                                                                                           |    |

|   |      |          | —D30:F2)                                                                                                                | 53 |

|   |      | 2.1.1    | VID—Vendor Identification Register (Audio—D30:F2)                                                                       | 54 |

|   |      | 2.1.2    | DID—Device Identification Register (Audio—D30:F2)                                                                       | 54 |

|   |      | 2.1.3    | PCICMD—PCI Command Register (Audio—D30:F2)                                                                              | 55 |

|   |      | 2.1.4    | PCISTS—PCI Status Register (Audio—D30:F2)                                                                               | 56 |

|   |      | 2.1.5    | RID—Revision Identification Register (Audio—D30:F2)                                                                     | 57 |

|   |      | 2.1.6    | PI—Programming Interface Register (Audio—D30:F2)                                                                        | 57 |

|   |      | 2.1.7    | SCC—Sub Class Code Register (Audio—D30:F2)                                                                              | 57 |

|   |      | 2.1.8    | BCC—Base Class Code Register (Audio—D30:F2)                                                                             | 57 |

|   |      | 2.1.9    | HEADTYP—Header Type Register (Audio—D30:F2)                                                                             | 58 |

|   |      | 2.1.10   | NAMBAR—Native Audio Mixer Base Address Register                                                                         |    |

|   |      |          | (Audio—D30:F2)                                                                                                          | 58 |

|   |      | 2.1.11   | NABMBAR—Native Audio Bus Mastering Base Address                                                                         |    |

|   |      |          | Register (Audio—D30:F2)                                                                                                 |    |

|   |      |          | MMBAR—Mixer Base Address Register (Audio—D30:F2)                                                                        | 59 |

|   |      | 2.1.13   | MBBAR—Bus Master Base Address Register                                                                                  |    |

|   |      | ~        | (Audio—D30:F2)                                                                                                          | 60 |

|   |      | 2.1.14   | SVID—Subsystem Vendor Identification Register                                                                           | 00 |

|   |      | 0445     | (Audio—D30:F2)                                                                                                          |    |

|   |      |          | SID—Subsystem Identification Register (Audio—D30:F2)                                                                    |    |

|   |      |          | CAP_PTR—Capabilities Pointer Register (Audio—D30:F2)                                                                    |    |

|   |      |          | INT_LN—Interrupt Line Register (Audio—D30:F2)                                                                           |    |

|   |      |          | INT_PN—Interrupt Pin Register (Audio—D30:F2)                                                                            |    |

|   |      | 2.1.19   | PCID—Programmable Codec Identification Register<br>(Audio—D30:F2)                                                       | 62 |

|   |      | 2 1 20   | CFG—Configuration Register (Audio—D30:F2)                                                                               |    |

|   |      | 2.1.20   | PID—PCI Power Management Capability Identification                                                                      |    |

|   |      | 2.1.21   | Register (Audio—D30:F2)                                                                                                 |    |

|   |      | 2.1.22   | PC—Power Management Capabilities Register                                                                               |    |

|   |      |          | (Audio—D30:F2)                                                                                                          | 64 |

|   |      | 2.1.23   | PCS—Power Management Control and Status Register                                                                        | -  |

|   |      |          | (Audio—D30:F2)                                                                                                          | 65 |

|   | 2.2  | AC '97   | Audio I/O Space (D30:F2)                                                                                                | 66 |

|   |      | 2.2.1    | x_BDBAR—Buffer Descriptor Base Address Register                                                                         |    |

|   |      |          | (Audio—D30:F2)                                                                                                          | 69 |

|   |      | 2.2.2    | x_CIV—Current Index Value Register (Audio—D30:F2)                                                                       | 70 |

|   |      | 2.2.3    | x_LVI—Last Valid Index Register (Audio—D30:F2)                                                                          |    |

|   |      | 2.2.4    | x_SR—Status Register (Audio—D30:F2)                                                                                     | 71 |

|   |      | 2.2.5    | x_PICB—Position In Current Buffer Register                                                                              |    |

|   |      |          | (Audio—D30:F2)                                                                                                          |    |

|   |      | 2.2.6    | x_PIV—Prefetched Index Value Register (Audio—D30:F2)                                                                    |    |

|   |      | 2.2.7    | x_CR—Control Register (Audio—D30:F2)                                                                                    |    |

|   |      | 2.2.8    | GLOB_CNT—Global Control Register (Audio—D30:F2)                                                                         |    |

|   |      | 2.2.9    | GLOB_STA—Global Status Register (Audio—D30:F2)                                                                          |    |

|   |      | 2.2.10   | CAS—Codec Access Semaphore Register (Audio—D30:F2)                                                                      |    |

|   |      | 2.2.11   | SDM—SDATA_IN Map Register (Audio—D30:F2)                                                                                | 78 |

#### Contents

# intel

| 3 | AC '9 | 97 Mode             | m Controller Registers (D30:F3)                                  | 81  |

|---|-------|---------------------|------------------------------------------------------------------|-----|

|   | 3.1   | AC '97              | Modem PCI Configuration Space (D30:F3)                           | 81  |

|   |       | 3.1.1               | VID—Vendor Identification Register (Modem—D30:F3)                |     |

|   |       | 3.1.2               | DID—Device Identification Register (Modem—D30:F3)                |     |

|   |       | 3.1.3               | PCICMD—PCI Command Register (Modem—D30:F3)                       |     |

|   |       | 3.1.4               | PCISTS—PCI Status Register (Modem—D30:F3)                        |     |

|   |       | 3.1.5               | RID—Revision Identification Register (Modem—D30:F3)              |     |

|   |       | 3.1.6               | PI—Programming Interface Register (Modem—D30:F3)                 |     |

|   |       | 3.1.7               | SCC-Sub Class Code Register (Modem-D30:F3)                       |     |

|   |       | 3.1.8               | BCC—Base Class Code Register (Modem—D30:F3)                      | 84  |

|   |       | 3.1.9               | HEADTYP—Header Type Register (Modem—D30:F3)                      | 85  |

|   |       | 3.1.10              | MMBAR—Modem Mixer Base Address Register                          |     |

|   |       |                     | (Modem—D30:F3)                                                   | 85  |

|   |       | 3.1.11              | MBAR—Modem Base Address Register (Modem—D30:F3)                  | 86  |

|   |       | 3.1.12              | SVID—Subsystem Vendor Identification Register<br>(Modem—D30:F3)  | 86  |

|   |       | 3.1.13              | SID—Subsystem Identification Register (Modem—D30:F3)             | 87  |

|   |       | 3.1.14              | CAP_PTR—Capabilities Pointer Register (Modem—D30:F3)             | 87  |

|   |       |                     | INT_LN—Interrupt Line Register (Modem—D30:F3)                    |     |

|   |       | 3.1.16              | INT_PIN—Interrupt Pin Register (Modem—D30:F3)                    | 88  |

|   |       | 3.1.17              | PID—PCI Power Management Capability Identification               |     |

|   |       |                     | Register (Modem—D30:F3)                                          | 88  |

|   |       | 3.1.18              | PC—Power Management Capabilities Register<br>(Modem—D30:F3)      |     |

|   |       | 3.1.19              | PCS—Power Management Control and Status Register                 |     |

|   |       |                     | (Modem—D30:F3)                                                   |     |

|   | 3.2   |                     | Modem I/O Space (D30:F3)                                         | 90  |

|   |       | 3.2.1               | x_BDBAR—Buffer Descriptor List Base Address Register             |     |

|   |       |                     | (Modem—D30:F3)                                                   |     |

|   |       | 3.2.2               | x_CIV—Current Index Value Register (Modem—D30:F3)                |     |

|   |       | 3.2.3               | x_LVI—Last Valid Index Register (Modem—D30:F3)                   |     |

|   |       | 3.2.4               | x_SR—Status Register (Modem—D30:F3)                              |     |

|   |       | 3.2.5               | x_PICB—Position in Current Buffer Register<br>(Modem—D30:F3)     | 04  |

|   |       | 3.2.6               | x_PIV—Prefetch Index Value Register                              | 94  |

|   |       | 3.2.0               | (Modem—D30:F3)                                                   | 94  |

|   |       | 3.2.7               | x_CR—Control Register (Modem—D30:F3)                             |     |

|   |       | 3.2.8               | GLOB_CNT—Global Control Register (Modem—D30:F3)                  |     |

|   |       | 3.2.9               | GLOB_STA—Global Status Register (Modem—D30:F3)                   |     |

|   |       | 3.2.10              |                                                                  |     |

|   |       | 0.2.10              | (Modem—D30:F3)                                                   | 99  |

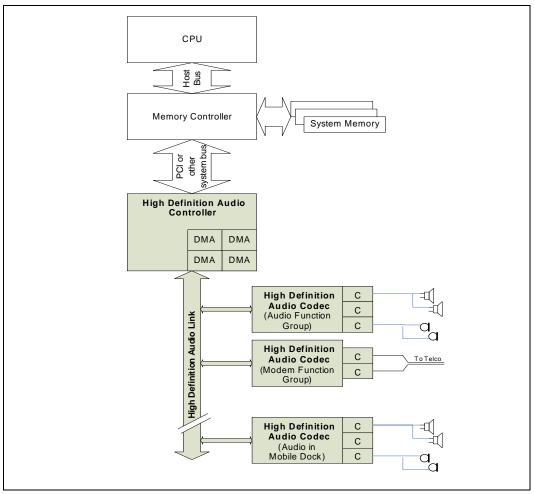

| 4 | Intel | <sup>®</sup> High D | efinition Audio Programming Model                                | 101 |

|   | 4.1   | Hardwa              | are System Overview                                              |     |

|   | 4.2   |                     | of Operation                                                     |     |

|   | 4.3   |                     | ller Initialization                                              |     |

|   |       | •                   | 4.3.0.1 Configuring a PCI or PCI Express* Interface              |     |

|   |       | 4.3.1               | Starting the Intel <sup>®</sup> High Definition Audio Controller |     |

|   | 4.4   | Codec               | Discovery                                                        |     |

|   | 4.5   |                     | Command and Control                                              | 104 |

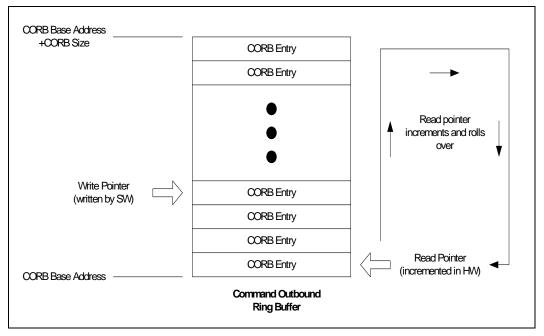

|   |       | 4.5.1               | Command Outbound Ring Buffer – CORB                              |     |

|   |            |                | 4.5.1.1                | CORB Buffer Allocation                   |          |          |

|---|------------|----------------|------------------------|------------------------------------------|----------|----------|

|   |            |                | 4.5.1.2                | CORB Entry Format                        |          |          |

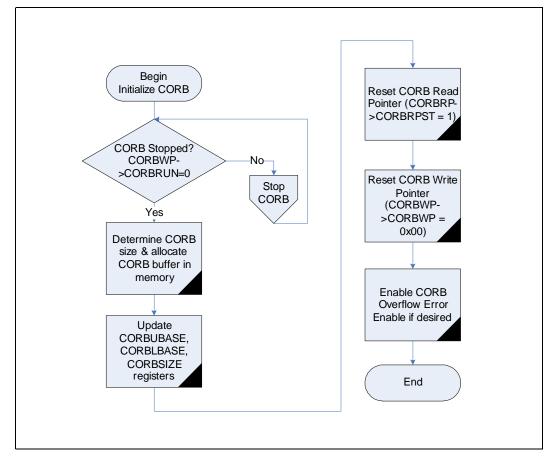

|   |            |                | 4.5.1.3                | Initializing the CORB                    | 1(       | )6       |

|   |            |                | 4.5.1.4                | Transmitting Commands via the CORB       |          |          |

|   |            |                | 4.5.1.5                | Other CORB Programming Notes             |          |          |

|   |            | 4.5.2          |                        | e Inbound Ring Buffer - RIRB             |          |          |

|   |            |                | 4.5.2.1                | RIRB Entry Format                        |          |          |

|   |            |                | 4.5.2.2                | Initializing the RIRB                    |          |          |

| 4 | 4.6        | Stream         | Managem                | nent                                     | 11       | 11       |

|   |            | 4.6.1          |                        | Data In Memory                           |          |          |

|   |            | 4.6.2          | Configuri              | ng and Controlling Streams               | 11       | 12       |

|   |            | 4.6.3          |                        | Streams                                  |          |          |

|   |            | 4.6.4          |                        | Streams                                  |          |          |

|   |            | 4.6.5          |                        | g Streams                                |          |          |

|   |            | 4.6.6          |                        | teady State Operation                    |          |          |

|   |            | 4.6.7          |                        | ization                                  |          |          |

|   |            | non            | 4.6.7.1                | Controller-to-Controller Synchronization |          |          |

|   |            |                | 4.6.7.2                | Stream-to-Stream Start Synchronization   | 11       | 14       |

|   |            |                | 4.6.7.3                | Stream-to-Stream Stop Synchronization    |          |          |

|   |            | 4.6.8          |                        | anagement                                |          |          |

|   |            | 1.0.0          | 4.6.8.1                | Power State Transitions                  |          |          |

|   |            |                | 4.6.8.2                | Power Optimization                       |          |          |

|   |            | 4.6.9          |                        | ake                                      |          |          |

|   |            | 4.0.5          | 4.6.9.1                | Codec Wake from System S0, Controller D0 |          |          |

|   |            |                | 4.6.9.2                | Codec Wake from System S0, Controller D3 |          |          |

|   |            |                | 4.6.9.3                | Codec Wake from System S3.               |          |          |

|   |            |                | 4.6.9.4                | Checking Wake Status on Resume           |          |          |

|   | <b>.</b> . |                |                        | -                                        |          |          |

|   |            |                |                        | equirements                              |          |          |

| ! | 5.1        |                |                        | re                                       |          |          |

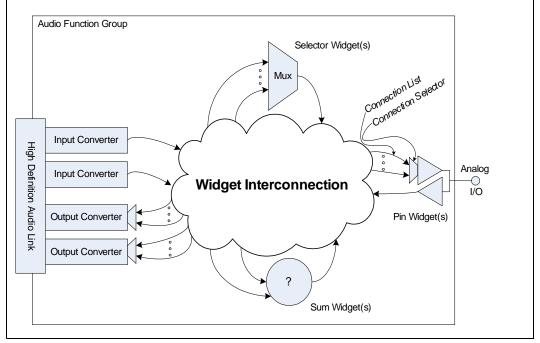

|   |            | 5.1.1          |                        | Architecture                             |          |          |

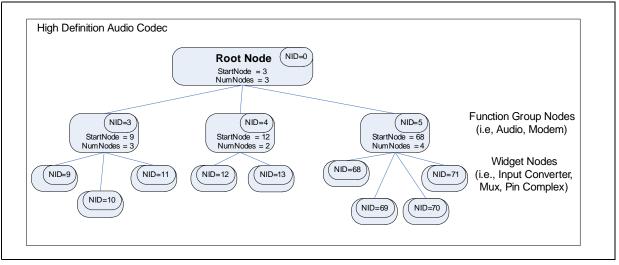

|   |            | 5.1.2          | Node Ad                | dressing                                 | 11       | 18       |

|   |            | 5.1.3          |                        | terconnection Rules                      |          |          |

| į | 5.2        | Qualitat       | tive Node              | Definition                               | 12       | 22       |

|   |            | 5.2.1          | Root Noc               | le                                       | 12       | 22       |

|   |            | 5.2.2          |                        | Groups                                   |          |          |

|   |            |                | 5.2.2.1                | Audio Function Group                     |          |          |

|   |            |                | 5.2.2.2                | Vendor Specific Modem Function Group     |          |          |

|   |            | 5.2.3          | Widgets.               |                                          |          |          |

|   |            | 0.2.0          | 5.2.3.1                | Audio Output Converter Widget            |          |          |

|   |            |                | 5.2.3.2                | Audio Input Converter Widget             |          |          |

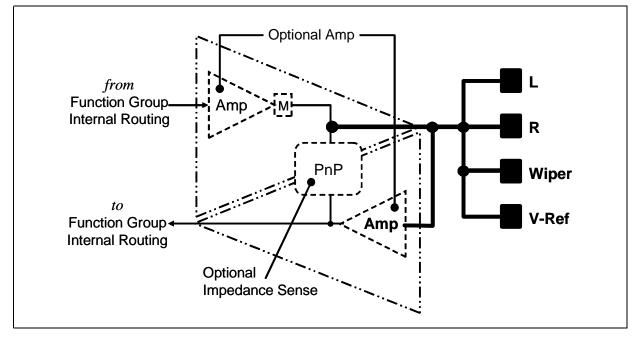

|   |            |                | 5.2.3.3                | Pin Widget                               |          |          |

|   |            |                | 5.2.3.4                | Mixer (Summing Amp) Widget               |          |          |

|   |            |                | 5.2.3.5                | Selector (Multiplexer) Widget            | 12       | 28       |

|   |            |                | 5.2.3.6                | Power Widget                             |          |          |

|   |            |                | 5.2.3.7                | Volume Knob Widget                       |          |          |

|   |            |                | 5.2.3.8                | Beep Generator Widget                    |          |          |

| į | 5.3        | Codec I        |                        | rs and Controls                          |          |          |

|   |            |                | Parametei              |                                          |          |          |

|   |            | 5.3.1          |                        |                                          | 13       | 30       |

|   |            | 5.3.1<br>5.3.2 | Required               | Verb Response                            |          |          |

|   |            | 5.3.2          | Required<br>Multiple S | Verb Response<br>SDI Operation           | 13       | 31       |

|   |            |                | Required<br>Multiple S | Verb Response                            | 13<br>13 | 31<br>32 |

5

|        |                      | 5.3.3.2     | Connection Select Control                 |   |    |

|--------|----------------------|-------------|-------------------------------------------|---|----|

|        |                      | 5.3.3.3     | Get Connection List Entry                 |   |    |

|        |                      | 5.3.3.4     | Processing State                          |   |    |

|        |                      | 5.3.3.5     | Coefficient Index                         |   |    |

|        |                      | 5.3.3.6     | Processing Coefficient                    |   |    |

|        |                      | 5.3.3.7     | Amplifier Gain/Mute                       |   |    |

|        |                      | 5.3.3.8     | Converter Format                          |   |    |

|        |                      | 5.3.3.9     | Digital Converter Control                 |   |    |

|        |                      |             | Power State                               |   |    |

|        |                      |             | Converter Stream, Channel                 |   |    |

|        |                      |             | Input Converter SDI Select                |   |    |

|        |                      |             | Pin Widget Control                        |   |    |

|        |                      |             | Unsolicited Response                      |   |    |

|        |                      |             | Pin Sense                                 |   |    |

|        |                      |             | EAPD/BTL Enable                           |   |    |

|        |                      |             | GPI Data                                  |   |    |

|        |                      | 5.3.3.18    | GPI Wake Enable Mask                      | 1 | 47 |

|        |                      |             | GPI Unsolicited Enable Mask               |   |    |

|        |                      | 5.3.3.20    | GPI Sticky Mask                           | 1 | 48 |

|        |                      |             | GPO Data                                  |   |    |

|        |                      |             | GPIO Data                                 |   |    |

|        |                      |             | GPIO Enable Mask                          |   |    |

|        |                      |             | GPIO Direction                            |   |    |

|        |                      | 5.3.3.25    | GPIO Wake Enable Mask                     | 1 | 51 |

|        |                      |             | GPIO Unsolicited Enable Mask              |   |    |

|        |                      |             | GPIO Sticky Mask                          |   |    |

|        |                      |             | Beep Generation                           |   |    |

|        |                      |             | Volume Knob                               |   |    |

|        |                      |             | Subsystem ID.                             |   |    |

|        |                      | 5.3.3.31    | Configuration Default                     | 1 | 55 |

|        |                      |             | Stripe Control                            |   |    |

|        | 504                  |             | Function Reset                            |   |    |

|        | 5.3.4                |             | ers                                       |   |    |

|        |                      | 5.3.4.1     | Vendor ID                                 |   |    |

|        |                      | 5.3.4.2     | Revision ID.                              |   |    |

|        |                      | 5.3.4.3     | Subordinate Node Count                    |   |    |

|        |                      | 5.3.4.4     | Function Group Type                       |   |    |

|        |                      | 5.3.4.5     | Audio Function Group Capabilities         |   |    |

|        |                      | 5.3.4.6     | Audio Widget Capabilities                 |   |    |

|        |                      | 5.3.4.7     | Supported PCM Size, Rates                 |   |    |

|        |                      | 5.3.4.8     | Supported Stream Formats                  |   |    |

|        |                      | 5.3.4.9     | Pin Capabilities                          |   |    |

|        |                      |             | Amplifier Capabilities                    |   |    |

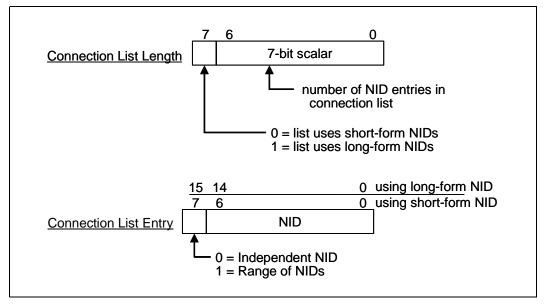

|        |                      | 5.3.4.11    | Connection List Length                    | 1 | 70 |

|        |                      |             | Supported Power States                    |   |    |

|        |                      |             | Processing Capabilities                   |   |    |

|        |                      |             | GP I/O Count                              |   |    |

|        |                      |             | Volume Knob Capabilities                  |   |    |

|        | 5.3.5                |             | Defined Verbs                             |   |    |

| ~      | 5.3.6                | •           | Parameter and Control Support             |   |    |

| Intel® | -                    |             | Audio Audio Controller Registers (D27:F0) | 1 | 77 |

| 6.1    | Intel <sup>®</sup> ⊢ | ligh Defini | tion Audio Audio PCI Configuration Space  |   |    |

|        | (High D              | efinition A | udio— D27:F0)                             | 1 | 77 |

6

#### Contents

## intel

| 6.1.1      | VID—Vendor Identification Register                                          |  |

|------------|-----------------------------------------------------------------------------|--|

| 0.1.1      | (High Definition Audio Controller—D27:F0)                                   |  |

| <b>040</b> |                                                                             |  |

| 6.1.2      | DID—Device Identification Register                                          |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.3      | PCICMD—PCI Command Register                                                 |  |

|            | (High Definition Audio Controller—D27:F0)179                                |  |

| 6.1.4      | PCISTS—PCI Status Register                                                  |  |

|            | (High Definition Audio Controller—D27:F0)180                                |  |

| 6.1.5      | RID—Revision Identification Register                                        |  |

|            | (High Definition Audio Controller—D27:F0)181                                |  |

| 6.1.6      | PI—Programming Interface Register                                           |  |

|            | (High Definition Audio Controller—D27:F0)181                                |  |

| 6.1.7      | SCC—Sub Class Code Register                                                 |  |

| -          | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.8      | BCC—Base Class Code Register                                                |  |

| 00         | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.9      | CLS—Cache Line Size Register                                                |  |

| 0.1.3      | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.10     |                                                                             |  |

| 0.1.10     | (High Definition Audio Controller—D27:F0)                                   |  |

| 6111       |                                                                             |  |

| 6.1.11     | HEADTYP—Header Type Register<br>(High Definition Audio Controller—D27:F0)   |  |

| 0 4 40     |                                                                             |  |

| 6.1.12     | AZBARL—Intel <sup>®</sup> High Definition Audio Lower Base Address Register |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.13     | AZBARU—Intel <sup>®</sup> High Definition Audio Upper Base Address Register |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.14     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.15     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.16     | CAPPTR—Capabilities Pointer Register (Audio—D30:F2)                         |  |

| 6.1.17     | INTLN—Interrupt Line Register                                               |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.18     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.19     |                                                                             |  |

| 0.1.10     | (High Definition Audio Controller—D27:F0)                                   |  |

| 6 1 20     | TCSEL—Traffic Class Select Register                                         |  |

| 0.1.20     | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.21     | PID—PCI Power Management Capability ID Register                             |  |

| 0.1.21     | (High Definition Audio Controller—D27:F0)                                   |  |

| 6 4 00     |                                                                             |  |

| 6.1.22     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.23     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.24     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.25     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)                                   |  |

| 6.1.26     |                                                                             |  |

|            | (High Definition Audio Controller—D27:F0)189                                |  |

| 6.1.27     | MMUA—MSI Message Upper Address Register                                     |  |

|            | -                                                                           |  |

|     |        | (High Definition Audio Controller—D27:F0)                            | 189 |

|-----|--------|----------------------------------------------------------------------|-----|

|     | 6.1.28 | MMD—MSI Message Data Register                                        |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 189 |

|     | 6.1.29 | PXID—PCI Express* Capability ID Register                             |     |

|     |        | (High Definition Audio Controller-D27:F0)                            | 189 |

|     | 6.1.30 | PXC—PCI Express* Capabilities Register                               |     |

|     |        | (High Definition Audio Controller—DŽ7:F0)                            | 190 |

|     | 6.1.31 | DEVCAP—Device Capabilities Register                                  |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 190 |

|     | 6.1.32 | DEVC—Device Control Register                                         |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 191 |

|     | 6.1.33 | DEVS—Device Status Register                                          |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 191 |

|     | 6.1.34 | VCCAP—Virtual Channel Enhanced Capability Header                     |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 192 |

|     | 6.1.35 | PVCCAP1—Port VC Capability Register 1                                |     |

|     |        | (High Definition Audio Controller-D27:F0)                            | 192 |

|     | 6.1.36 | PVCCAP2—Port VC Capability Register 2                                |     |

|     |        | (High Definition Audio Controller-Ď27:F0)                            | 192 |

|     | 6.1.37 | PVCCLT—Port VC Control Register                                      |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 193 |

|     | 6.1.38 | PVCSTS—Port VC Status Register                                       |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 193 |

|     | 6.1.39 |                                                                      |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 193 |

|     | 6.1.40 | VC0CTL—VC0 Resource Control Register                                 |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 194 |

|     | 6.1.41 | VC0STS—VC0 Resource Status Register                                  |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 194 |

|     | 6.1.42 | VCiCAP—VCi Resource Capability Register                              |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 194 |

|     | 6.1.43 | VCiCTL—VCi Resource Control Register                                 |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 195 |

|     | 6.1.44 | VCiSTS—VCi Resource Status Register                                  |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 195 |

|     | 6.1.45 |                                                                      |     |

|     |        | Capability Header Register (High Definition Audio Controller-D27:F0) | 195 |

|     | 6.1.46 | ESD—Element Self Description Register                                |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 196 |

|     | 6.1.47 | L1DESC—Link 1 Description Register                                   |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 196 |

|     | 6.1.48 | L1ADDL—Link 1 Lower Address Register                                 |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 196 |

|     | 6.1.49 | L1ADDU—Link 1 Upper Address Register                                 |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 197 |

| 6.2 |        | ligh Definition Audio Memory Mapped Configuration Registers          |     |

|     | ν O    | Definition Audio— D27:F0)                                            | 197 |

|     | 6.2.1  | GCAP—Global Capabilities Register                                    | _   |

|     |        | (High Definition Audio Controller—D27:F0)                            | 201 |

|     | 6.2.2  | VMIN—Minor Version Register                                          |     |

|     |        | (High Definition Audio Controller—D27:F0)                            | 201 |

|     | 6.2.3  | VMAJ—Major Version Register                                          |     |

|        | (High Definition Audio Controller—D27:F0)  |

|--------|--------------------------------------------|

| 6.2.4  | OUTPAY—Output Payload Capability Register  |

|        | (High Definition Audio Controller-D27:F0)  |

| 6.2.5  | INPAY—Input Payload Capability Register    |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.6  | GCTL—Global Control Register               |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.7  | WAKEEN—Wake Enable Register                |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.8  | STATESTS—State Change Status Register      |

|        | (High Definition Audio Controller-D27:F0)  |

| 6.2.9  | GSTS—Global Status Register                |

|        | (High Definition Audio Controller-D27:F0)  |

| 6.2.10 | INTCTL—Interrupt Control Register          |

|        | (High Definition Audio Controller-D27:F0)  |

| 6.2.11 | INTSTS—Interrupt Status Register           |

|        | (High Definition Audio Controller-D27:F0)  |

| 6.2.12 | WALCLK—Wall Clock Counter Register         |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.13 | SSYNC—Stream Synchronization Register      |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.14 | CORBLBASE—CORB Lower Base Address Register |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.15 | CORBUBASE—CORB Upper Base Address Register |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.16 | CORBRP—CORB Read Pointer Register          |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.17 | CORBCTL—CORB Control Register              |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.18 | CORBST—CORB Status Register                |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.19 | CORBSIZE—CORB Size Register                |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.20 | RIRBLBASE—RIRB Lower Base Address Register |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.21 | RIRBUBASE—RIRB Upper Base Address Register |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.22 | RIRBWP—RIRB Write Pointer Register         |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.23 |                                            |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.24 | RIRBCTL—RIRB Control Register              |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.25 | RIRBSTS—RIRB Status Register               |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.26 | RIRBSIZE—RIRB Size Register                |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.27 | IC—Immediate Command Register              |

|        | (High Definition Audio Controller—D27:F0)  |

| 6.2.28 | IR—Immediate Response Register             |

| 0 0 00 | (High Definition Audio Controller—D27:F0)  |

| 6.2.29 | IRS—Immediate Command Status Register      |

|        |                      | (High Definition Audio Controller—D27:F0)2                                                         | 13  |

|--------|----------------------|----------------------------------------------------------------------------------------------------|-----|

|        | 6.2.30               | DPLBASE—DMA Position Lower Base Address Register                                                   |     |

|        |                      | (High Definition Audio Controller—D27:F0)24                                                        | 13  |

|        | 6.2.31               | DPUBASE—DMA Position Upper Base Address Register                                                   |     |

|        |                      | (High Definition Audio Controller—D27:F0)24                                                        | 14  |

|        | 6.2.32               |                                                                                                    |     |

|        |                      | (High Definition Audio Controller—D27:F0)                                                          | 14  |

|        | 6.2.33               | SDSTS—Stream Descriptor Status Register                                                            |     |

|        |                      | (High Definition Audio Controller—D27:F0)                                                          | 16  |

|        | 6.2.34               | SDLPIB—Stream Descriptor Link Position in Buffer                                                   | 4 – |

|        | 0 0 05               | Register (High Definition Audio Controller—D27:F0)                                                 | 17  |

|        | 6.2.35               | SDCBL—Stream Descriptor Cyclic Buffer Length Register<br>(High Definition Audio Controller—D27:F0) | 17  |

|        | 6.2.36               | SDLVI—Stream Descriptor Last Valid Index Register                                                  | 17  |

|        | 0.2.30               | (High Definition Audio Controller—D27:F0)                                                          | 18  |

|        | 6.2.37               |                                                                                                    | 10  |

|        | 0.2.57               | (High Definition Audio Controller—D27:F0)                                                          | 18  |

|        | 6.2.38               | SDFIFOS—Stream Descriptor FIFO Size Register                                                       | 10  |

|        | 0.2.00               | (High Definition Audio Controller—D27:F0)                                                          | 19  |

|        | 6.2.39               |                                                                                                    |     |

|        |                      | (High Definition Audio Controller—D27:F0)                                                          | 20  |

|        | 6.2.40               |                                                                                                    |     |

|        |                      | Register                                                                                           |     |

|        |                      | (High Definition Audio Controller—D27:F0)22                                                        | 21  |

|        | 6.2.41               | SDBDPU—Stream Descriptor Buffer Descriptor List Pointer                                            |     |

|        |                      | Upper Base Address Register (High Definition Audio Controller-D27:F0)22                            | 21  |

| Intel® | Hiah De              | efinition Audio BIOS Considerations                                                                | 23  |

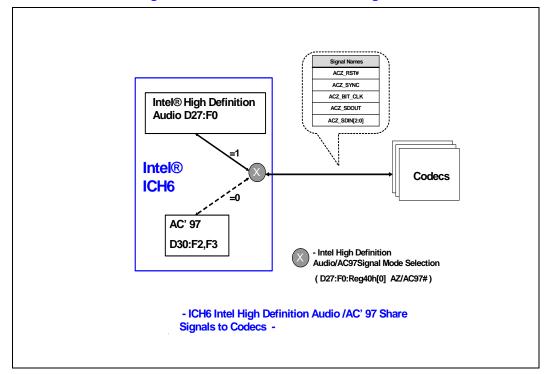

| 7.1    |                      | ligh Definition Audio/AC' 97 Signal Mode Selection22                                               |     |

| 1.1    | 7.1.1                | Intel <sup>®</sup> High Definition Audio/AC' 97 Codec Detection                                    | 2/  |

|        | 7.1.2                | Intel <sup>®</sup> High Definition Audio Codec Initialization                                      | 26  |

|        | 1.1.2                | 7.1.2.1 Intel <sup>®</sup> High Definition Audio Codec Architecture Introduction                   | 26  |

|        |                      | 7.1.2.2 Codec Verb Table                                                                           |     |

|        |                      | 7.1.2.3 Codec Initialization Programming Sequence                                                  |     |

|        |                      | 7.1.2.4 Codec Initialization Sample Code                                                           |     |

| 7.2    | Intel <sup>®</sup> H | ligh Definition Audio Controller Configuration23                                                   |     |

|        | 7.2.1                | Intel <sup>®</sup> High Definition Audio PME Event                                                 | 40  |

### **Figures**

7

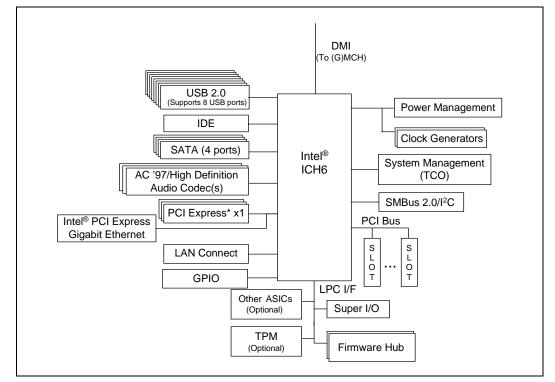

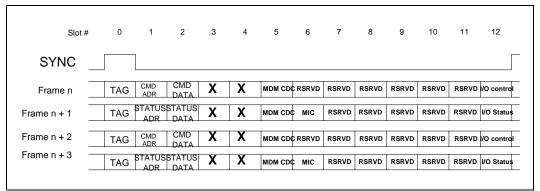

| 1-1 | Block Diagram Intel <sup>®</sup> ICH6 Component                             | 19  |

|-----|-----------------------------------------------------------------------------|-----|

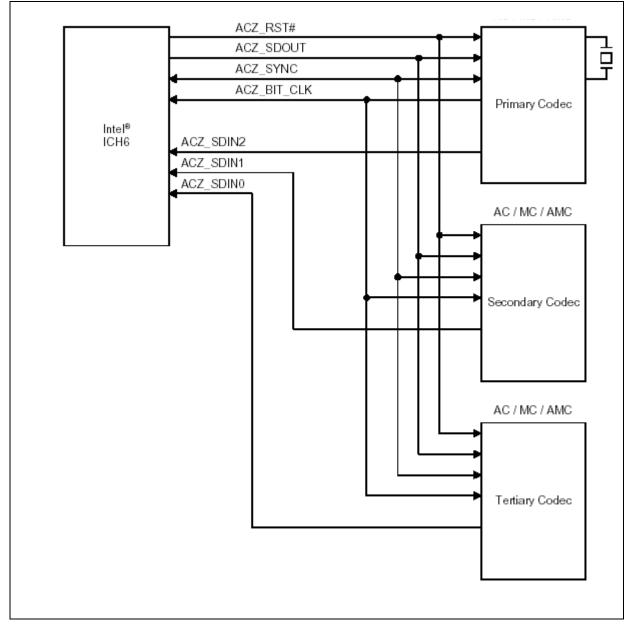

| 1-2 | Intel® ICH6 AC '97 Controller Connection to Its Companion Codecs            | 20  |

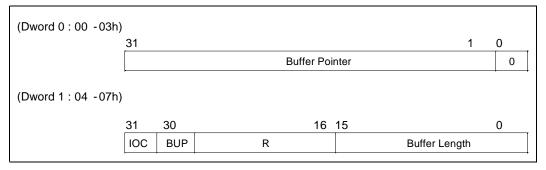

| 1-3 | Generic Form of Buffer Descriptor (One Entry in the List)                   |     |

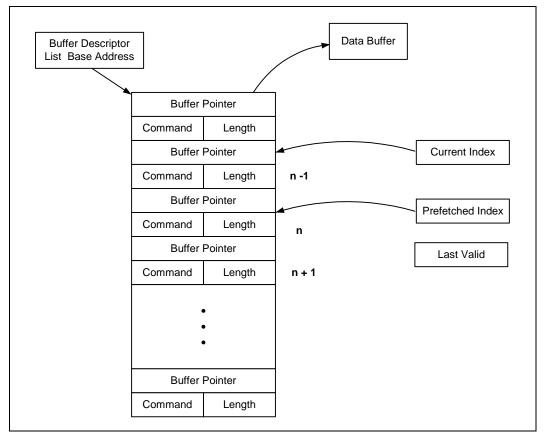

| 1-4 | Buffer Descriptor List                                                      | 27  |

| 1-5 | Compatible Implementation with Left and Right Sample Pair in Slot 3/4       |     |

|     | Every Frame                                                                 |     |

| 1-6 | Compatible Sample Rate Conversion Slots 3 and 4 Alternating over Next Frame | 32  |

| 1-7 | Incompatible Sample Rate Conversion with Repeating Slots over Next Frames   | 32  |

| 4-1 | Intel <sup>®</sup> High Definition Audio Hardware Overview                  | 101 |

| 4-2 | Command Ring Buffer (CORB)                                                  |     |

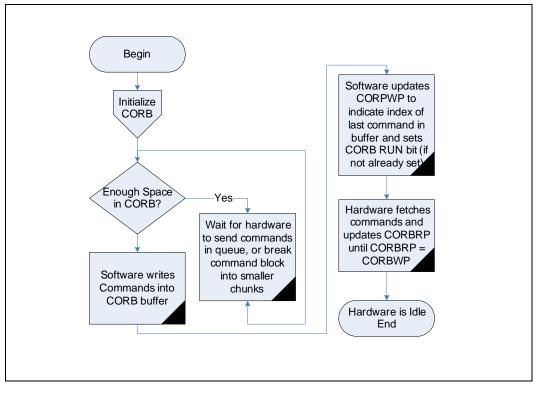

| 4-3 | CORB Initialization                                                         |     |

|          | ansmitting Commands via the CORB1                                         |    |

|----------|---------------------------------------------------------------------------|----|

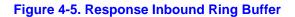

|          | sponse Inbound Ring Buffer1                                               |    |

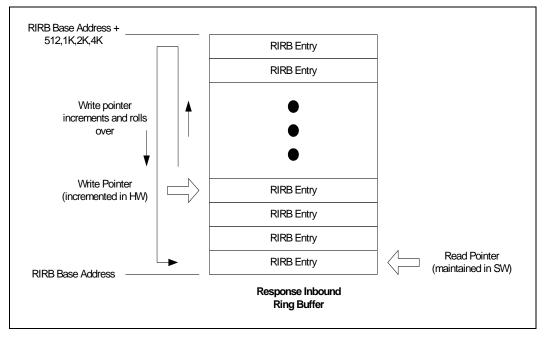

|          | tializing the RIRB1                                                       |    |

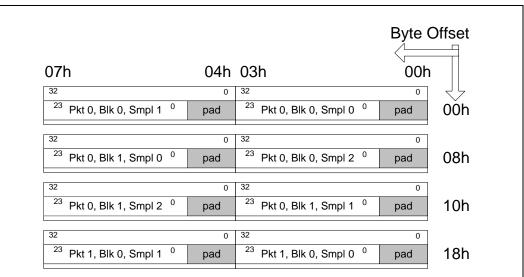

|          | 24-bit, 3 Channel, 96 kHz Stream in Memory1                               |    |

|          | odule-Based Codec Architecture 1                                          |    |

|          | dec Module Addressing Scheme1                                             |    |

|          | nnection Lists1                                                           |    |

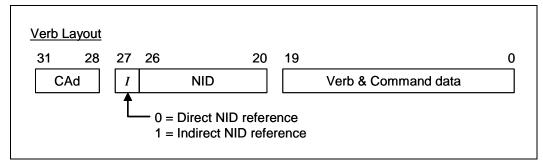

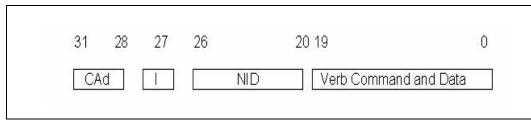

|          | rb Addressing Fields1                                                     |    |

|          | dio Output Converter Widget1                                              |    |

|          | Idio Input Converter Widget1                                              |    |

|          | ח Widget 1                                                                |    |

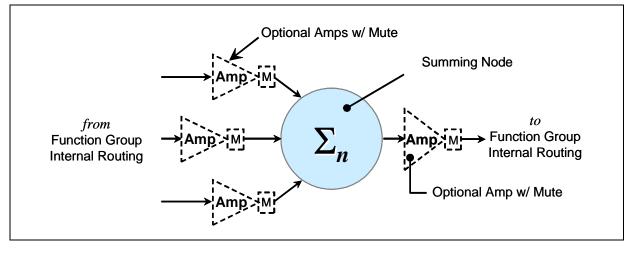

|          | xer Widget1                                                               |    |

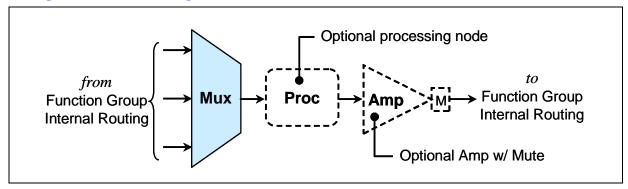

| 5-9 Se   | lector Widget1                                                            | 28 |

| 5-10Co   | mmand Field Format1                                                       | 30 |

| 5-11Re   | sponse Field Format1                                                      | 30 |

| 5-12Re   | sponse Format1                                                            | 33 |

|          | sponse Format1                                                            |    |

| 5-14 Am  |                                                                           | 36 |

| 5-15 Am  | nplifier Gain/Mute Get Response1                                          | 36 |

|          | nplifier Gain/Mute Set Payload1                                           |    |

|          | PDIF IEC Control (SIC) Bits1                                              |    |

|          | n Cntl Format                                                             |    |

|          | ableUnsol Format1                                                         |    |

| 5-20 Sul | bsystem ID Register1                                                      | 55 |

|          | nfiguration Data Structure                                                |    |

|          | ripe Control Register1                                                    |    |

|          | ndor ID Response Format1                                                  |    |

|          | evision ID Response Format1                                               |    |

|          | bordinate Node Count Response Format1                                     |    |

|          | nction Group Type Response Format1                                        |    |

|          | dio Function Group Capabilities Response Format1                          |    |

|          | dio Widget Capabilities Response Format1                                  |    |

|          | pported PCM Size, Rates Return Format1                                    |    |

|          | pported Stream Formats Response Format1                                   |    |

|          | n Capabilities Response Format1                                           |    |

|          | Ref Bit Field                                                             |    |

|          | nplifier Capabilities Response Format1                                    |    |

|          | nnection List Length Response Format1                                     |    |

|          | pported Power States Response Format1                                     |    |

|          | ocessing Capabilities Response Format1                                    |    |

|          | P I/O Capabilities Response Format                                        |    |

|          | lume Knob Capabilities Response Format1                                   |    |

|          | el® ICH6 Intel® High Definition Audio/AC'97 Share Signals to Codecs       |    |

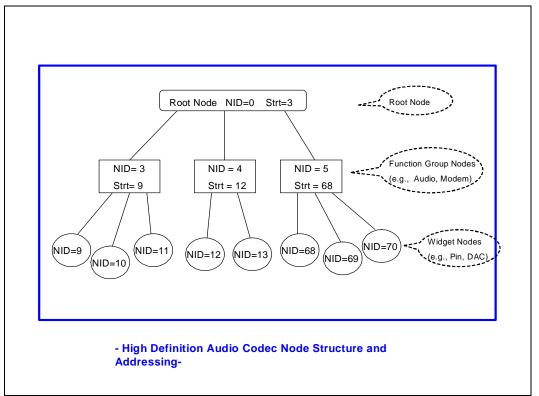

|          | el <sup>®</sup> High Definition Audio Codec Node Structure and Addressing |    |

|          | rmat of a Verb Dword                                                      |    |

|          |                                                                           | 1  |

### **Tables**

| 1-1 | Audio Features Distribution Matrix | 21 |

|-----|------------------------------------|----|

| 1-2 | Audio Registers                    | 24 |

| 1-3 Modem Registers                                                                | 25  |

|------------------------------------------------------------------------------------|-----|

| 1-4 BD Buffer Pointer (DWORD 0: 00-03h)                                            | 26  |

| 1-5 BD Control and Length (DWORD 1: 04-07h)                                        | 27  |

| 1-6 Audio Descriptor List Base Address                                             | 28  |

| 1-7 Modem Descriptor List Base Address                                             | 28  |

| 1-8 Audio Last Valid Index                                                         | 28  |

| 1-9 Modem Last Valid Index                                                         | 28  |

| 1-10 FIFO Summary                                                                  | 33  |

| 1-11 SDM Register Description                                                      | 34  |

| 1-12 Codecs Topologies                                                             | 36  |

| 1-13 Power State Mapping for Audio Single or Dual (Split) Codec Desktop Transition | 37  |

| 1-14 Power State Mapping for Modem Single Codec Desktop Transition                 | 38  |

| 1-15 Power State Mapping for Audio in Dual Codec Desktop Transition                | 38  |

| 1-16 Power State Mapping for Modem in Dual Codec Desktop Transition                | 39  |

| 1-17 Audio Codec Extended Audio ID Register                                        | 43  |

| 1-18 Single Codec Audio Channel Distribution                                       |     |

| 1-19 Multiple Codec Audio Channel Distribution                                     | 44  |

| 1-20 CM 4/6 -PCM Channels Capability Bits                                          |     |

| 1-21 AC-Link PCM 4/6 -Channels Enable Bits                                         | 45  |

| 1-22 Sample Capabilities                                                           | 45  |

| 1-23 PCM Out Mode Selector                                                         | 45  |

| 1-24 Global Control Register S-P/DIF Slot Map Bits                                 | 46  |

| 1-25 Topology Descriptor                                                           | 47  |

| 1-26 SDATA_IN Map                                                                  | 47  |

| 1-27 Codec Ready Bits                                                              | 48  |

| 1-28MMBAR: Mixer Base Address Register                                             | 48  |

| 2-1 AC '97 Audio PCI Register Address Map (Audio-D30:F2)                           | 53  |

| 2-2 Intel <sup>®</sup> ICH6 Audio Mixer Register Configuration                     | 66  |

| 2-3 Native Audio Bus Master Control Registers                                      | 67  |

| 3-1 AC '97 Modem PCI Register Address Map (Modem—D30:F3)                           | 81  |

| 3-2 Intel <sup>®</sup> ICH6 Modem Mixer Register Configuration                     | 90  |

| 3-3 Modem Registers                                                                |     |

| 4-1 RIRB Entry Format                                                              | 109 |

| 5-1 Get Parameter Command                                                          | 132 |

| 5-2 Connection Select Control                                                      | 132 |

| 5-3 Connection List Entry Control                                                  | 133 |

| 5-4 Processing State                                                               |     |

| 5-5 Coefficient Index                                                              | 135 |

| 5-6 Processing Coefficient                                                         | 135 |

| 5-7 Amplifier Gain/Mute                                                            | 136 |

| 5-8 Converter Format                                                               | 138 |

| 5-9 SPDIF Sync Preamble Bits                                                       |     |

| 5-10 S/PDIF Converter Control 1 and 2                                              | 139 |

| 5-11 Power State                                                                   | 140 |

| 5-12 Converter Control                                                             | 142 |

| 5-13 SDI Select                                                                    | 142 |

| 5-14 Enable VRef                                                                   |     |

| 5-15 VRefEn Values                                                                 |     |

| 5-16 Connection Set Control                                                        |     |

| 5-17 Pin Sense                                                                     | 145 |

| 5-18EAPD/BTL Enable1                                                         | 146 |

|------------------------------------------------------------------------------|-----|

| 5-19 GPI Data1                                                               | 147 |

| 5-20 GPI Wake Mask1                                                          | 147 |

| 5-21 GPI Unsolicited Enable1                                                 | 148 |

| 5-22 GPI Sticky Mask1                                                        | 148 |

| 5-23 GPO Data1                                                               | 149 |

| 5-24 GPIO Data1                                                              | 149 |

| 5-25 GPIO Enable1                                                            | 150 |

| 5-26 GPIO Direction1                                                         | 151 |

| 5-27 GPIO Wake Enable1                                                       | 151 |

| 5-28 GPIO Unsolicited Enable 1                                               |     |

| 5-29 GPIO Sticky Mask1                                                       | 152 |

| 5-30 Beep Generation1                                                        | 153 |

| 5-31 Volume Knob Control1                                                    | 154 |

| 5-32 Subsystem ID1                                                           |     |

| 5-33Configuration Default1                                                   | 155 |

| 5-34 Port Connectivity1                                                      |     |

| 5-35 Location1                                                               | 157 |

| 5-36 Default Device1                                                         | 158 |

| 5-37 Connection Type1                                                        |     |

| 5-38 Color1                                                                  |     |

| 5-39Miscellaneous1                                                           |     |

| 5-40 Stripe Control1                                                         |     |

| 5-41 Function Reset1                                                         | 160 |

| 5-42Node Type1                                                               | 163 |

| 5-43 Widget Type1                                                            |     |

| 5-44Bit Depth and Sample Rate1                                               |     |

| 5-45 Required Support for Parameters1                                        |     |

| 5-46 Required Support for Verbs1                                             | 174 |

| 6-1 Intel <sup>®</sup> High Definition Audio Audio PCI Register Address Map  |     |

| (High Definition Audio—D27:F0)1                                              | 177 |

| 6-2 Intel <sup>®</sup> High Definition Audio Audio PCI Register Address Map  |     |

| (High Definition Audio—D27:F0)1                                              |     |

| 7-1 D27:F0:Reg40h - AZCTL - Intel <sup>®</sup> High Definition Audio Control | 224 |

### **Revision History**

| Revision<br>Number | Description                                                                                                                        | Date      |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|

| -001               | Initial public release                                                                                                             | June 2004 |

| -002               | Added Codec Features and Requirements section                                                                                      | July 2004 |

| -003               | <ul> <li>Sections 7.3 and 8 removed. For information about these sections<br/>please contact your Intel representative.</li> </ul> | May 2005  |

§

Contents

### intel®

### **1** AC '97 Programming Model

### 1.1 Intel<sup>®</sup> ICH6: AC '97 Software

| Device Name               | Vendor ID | Device ID | Subsystem<br>Vendor ID                                                            | Subsystem<br>Device ID                                                            | Base Class Code | Sub-Class Code | Prog. Interface | Revision ID | Bus Number<br>(PCI Addr) | Device Number<br>(PCI Addr) | Function Number<br>(PCI Addr) | Microsoft PNP Device<br>Node ID                                                         | Intel Desired Device<br>Description (INF name)<br>Name for:<br>Windows* 95<br>Windows NT*<br>Windows NT*                     |

|---------------------------|-----------|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|----------------|-----------------|-------------|--------------------------|-----------------------------|-------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Intel <sup>®</sup><br>ICH | 8086      | 2415      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 5                             | PCI\VEN_8086&DE<br>V_2415 (subsystem<br>will also provide<br>additional<br>information) | Intel <sup>®</sup> 82801AA AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                             |

| Intel<br>ICH              | 8086      | 2416      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 07h             | 03h            | 00h             | ALL         | 00h                      | 1Fh                         | 6                             | PCI/VEN_8086&DE<br>V_2416 (subsystem<br>will also provide<br>additional<br>information) | Intel 82801AA AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF)                                          |

| Intel<br>ICH-0            | 8086      | 2425      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 5                             | PCI\VEN_8086&DE<br>V_2425<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> 82801AB AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                             |

| Intel<br>ICH-0            | 8086      | 2426      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 07h             | 03h            | 00h             | ALL         | 00h                      | 1Fh                         | 6                             | PCI\VEN_8086&DE<br>V_2426 (subsystem<br>will also provide<br>additional<br>information) | Intel 82801AB AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF)                                          |

| Intel<br>ICH3             | 8086      | 2445      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 5                             | PCI/VEN_8086&DE<br>V_2445 (subsystem<br>will also provide<br>additional<br>information) | Intel <sup>®</sup> "ICH3" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                              |

| Intel<br>ICH3             | 8086      | 2446      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 6                             | PCI/VEN_8086&DE<br>V_2446<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH3 DT/Server /<br>Mobile/Low End" AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF) |

| Intel<br>ICH4             | 8086      | 24C5      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 5                             | PCI\VEN_8086&DE<br>V_24C5<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> "ICH4" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                              |

| Intel<br>ICH4             | 8086      | 24C6      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh                         | 6                             | PCI\VEN_8086&DE<br>V_24C6<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH4 DT/Server /<br>Mobile/Low End" AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF) |

| Intel<br>ICH5             | 8086      | 24D5      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | 00          | 00h                      | 1Fh                         | 5                             | PCI\VEN_8086&DE<br>V_24C6<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH5 DT/Server /<br>Mobile/Low End" AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF) |

| Device Name   | Vendor ID | Device ID | Subsystem<br>Vendor ID                                                            | Subsystem<br>Device ID                                                            | Base Class Code | Sub-Class Code | Prog. Interface | Revision ID | Bus Number<br>(PCI Addr) | Device Number<br>(PCI Addr) | Function Number<br>(PCI Addr) | Microsoft PNP Device<br>Node ID                                                         | Intel Desired Device<br>Description (INF name)<br>Name for:<br>Windows*95<br>Windows*07*<br>Windows NT*<br>Windows 2000*     |

|---------------|-----------|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|----------------|-----------------|-------------|--------------------------|-----------------------------|-------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Intel<br>ICH6 | 8086      | 266E      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | 00          | 00h                      | 1Eh                         | 2                             | PCI\VEN_8086&DE<br>V_24C6<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH6 DT/Server /<br>Mobile/Low End" AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF) |

### 1.1.1 Introduction

This document was prepared to assist Independent Hardware Vendors (IHV) in supporting the Intel<sup>®</sup> I/O Controller Hub (ICH6) AC '97 Digital Controller feature set. This document also applies to the previous generation of Intel I/O Controller Hub components. New features for the ICH6 which are not supported in the ICH component have been distinguished by gray shading to improve readability. Please refer to the Applicable Component Table, above. This document also describes the general requirements to develop an audio mini-port driver that will make use of the AC '97 audio interface. The primary purpose of this document is to supplement the information provided in the *Intel<sup>®</sup> I/O Controller Hub 6 (ICH6) Family Datasheet* for use by IHVs and Intel customers developing their own driver interface.

This document also describes functions that the BIOS or Operating Systems (OS) must perform in order to ensure correct and reliable operation of the platform. This document will be supplemented from time to time with specification updates. The specification updates contain information relating to the latest programming changes. Check with your Intel representative for availability of specification updates.

#### Figure 1-1. Block Diagram Intel<sup>®</sup> ICH6 Component