## TC9021 64-Bit PCI Gigabit Ethernet Controller

## 1 Features

- PCI & DMA Features

- PCI Specification Revision 2.2 compliant

- 64-bit, 33/66MHz bus master capability

- Efficient DMA operation maximizes PCI band-width utilization

- 1 Terabyte (40 bit) address space

- Scatter, gather transmit/receive DMA

- Transmit "interrupt-less" mode of operation

- Transmit frame priority queuing

- Receive frame priority interrupts

- Receive interrupt coalescing

- FIFO Features

- Large transmit & receive FIFO

- No external memory required

- Receive FIFO flow control thresholds

- MAC Features

- IEEE 802.3z, 802.3x compliant

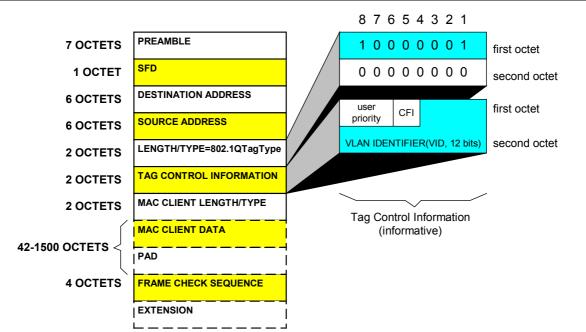

- IEEE 802.1p, 802.1Q compliant

- 1000Mbps, 100Mbps, 10Mbps triple speed, half/full duplex operation

- Transmit and receive back to back frames at full wire speed

- Half duplex carrier extension and packet burst-ing

- Asymmetric/symmetric flow control

- VLAN tag insertion/removal

- VLAN tagged frame filtering

- IP, TCP, UDP checksum calculation/verification

- 802.3 MIB & RMON MIB statistic register sets

- 64-bit hash table for multicast frame filtering

- Jumbo frame support, transmit and receive

- GMII and MII support

- 1000BASE-X PCS Features

- For use with 1000BASE-X Gigabit PHY devices having Ten Bit Interface (TBI)

- 8B10B encoder/decoder

- Auto-Negotiation

- PHY management registers

- Power Management

- WakeOnLAN support

- ACPI Revision 1.0 compliant

- 2.5/3.3V CMOS with 5V tolerant I/O

- Low power 0.25µm technology

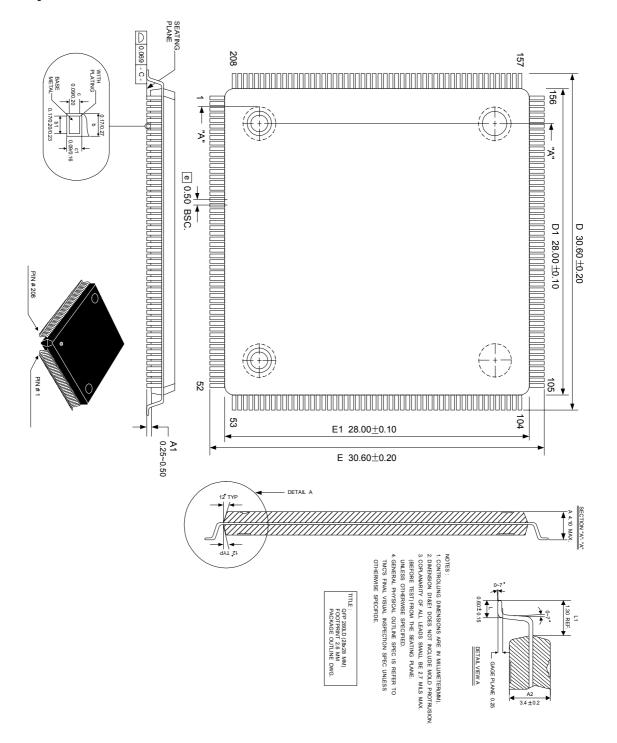

- 208-pin PQFP

1/136

The TC9021 is compliant to 802.3x Full Duplex standard, and supporting both symmetrical and asymmetrical flow control. PAUSE frames can be automatically generated by the device according to programmable flow control thresholds associated with the receive buffer.

To support half duplex gigabit operation, the

## 2 General Description

The TC9021 is designed as a high performance, host-optimized network interface, targeted for applications (either embedded or as a standard NIC) operating in full or half duplex Gigabit Ether-net LANs.

The highly efficient scatter/gather DMA logic moves data between 1 terabyte of system memory via the 64-bit 66MHz PCI bus interface. After the DMA processing overhead, each independent transmit and receive DMA channel can sustain well over 1 gigabit per second of throughput. The TC9021 stores frames in large integrated data buffers, eliminating the need for external buffer memory.

In order to reduce the processing load of the host CPU, the TC9021 implements TCP, UDP and IP V4 checksum generation and validation. A flexible scheme to coalesce host system interrupts allows the host CPU to process multiple frames with a single interrupt from the TC9021, further increasing the efficiency of the host system.

The TC9021 supports 802.1p/Q tagged frames by automatically inserting and removing the tag fields, which allows for compatibility with legacy hardware and software. Receive tagged frames can be filtered by the device according to the VLAN ID of the frame. The arrival of higher priority frames can be programmed to generate immediate interrupts for notification to the host system.

The TC9021 supports jumbo frame technology that allows for extension of Ethernet frame length up to 9018 (or 9022 for VLAN tagged) octets. Tests have shown servers using jumbo frames has significant performance improvement over non-jumbo frame enabled systems when operating in a Gigabit Ethernet environment.

> TC9021-DS-R20 Apr. 26, 2001

TC9021 inplements carrier extension and packet bursting functions compliant to 802.3z standard.

The TC9021 supports three PHY interfaces, the standard media independent MII (for 10Mbps and 100Mbps PHY) and GMII (for 1000Mbps PHY), and the defacto TBI interface for 1000BASE-X PHY.

To further optimize the system configuration for 1000BASE-X systems, the TC9021 implements the entire 1000BASE-X PCS function, including 8B10B encoder and decoder, and Auto-Negotiation. The TBI interface allows the TC9021 to be connected directly to an industry standard SERDES device for 1000BASE-X applications.

The TC9021 is fully compliant with ACPI Power Management specification revision 1.0. The TC9021 also supports Wake-On-LAN and Magic Packet power management remote wakeup mechanisms.

The TC9021 implements a complete set of Ether-net management statistic MIB and RMON counters that provide detail performance information about the network and the interface.

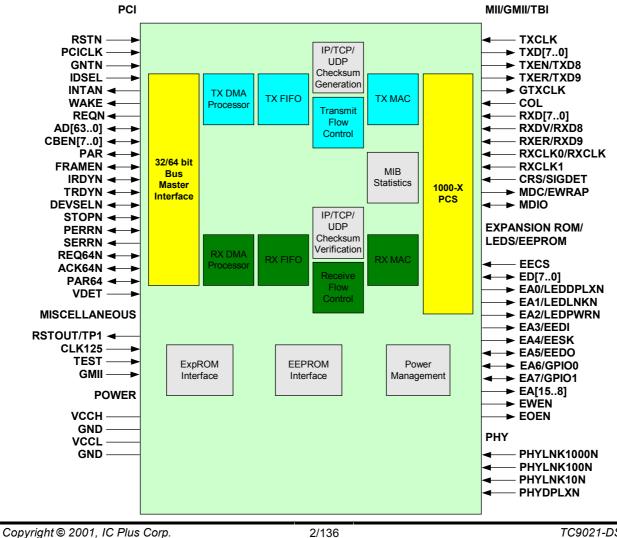

### 3 Block Diagram

All rights reserved. Preliminary, Specification subject to change without notice.

| TAB | LE OF CONTEN   | ITS                              |     |

|-----|----------------|----------------------------------|-----|

| 1   | Features       |                                  | 1   |

| 2   |                | iption                           |     |

| 3   |                | •<br>                            |     |

| 4   |                | ns                               |     |

| 5   |                | tions                            |     |

| 6   | Functional Des | scription                        | 14  |

|     | 6.1 PCI Bus    | s Interface                      | 14  |

|     | 6.2 DMA        |                                  | 14  |

|     | 6.2.1          | Transmit DMA                     | 14  |

|     | 6.2.2          | Receive DMA                      | 15  |

|     | 6.3 Interrup   | ots                              | 16  |

|     | 6.3.1          | Transmit DMA Interrupts          | 17  |

|     | 6.3.2          | "Interrupt-Less" Transmit DMA    | 17  |

|     | 6.3.3          | Receive DMA Interrupts           |     |

|     | 6.3.4          | Receive DMA Interrupt Coalescing |     |

|     | 6.4 ACPI       |                                  | 18  |

|     | 6.4.1          | Power Management States          | 18  |

|     | 6.5 Wake C     | Dn LAN                           | 19  |

|     | 6.5.1          | Power Management Events          | 19  |

|     | 6.6 FIFO       | -                                |     |

|     | 6.7 MAC        |                                  |     |

|     | 6.7.1          | VLAN                             | 22  |

|     | 6.7.2          | Layer 3/4 Checksums              | 23  |

|     | 6.7.3          | Flow Control                     | -   |

|     | 6.8 GMII       |                                  | 24  |

|     | 6.9 PCS        |                                  | 25  |

|     | 6.9.1          | Auto-Negotiation                 | 25  |

|     | 6.10 Registe   | ers and Data Structures          | 27  |

|     | 6.10.1         | Transmit DMA Data Structure      |     |

|     | 6.10.2         | Receive DMA Data Structure       |     |

|     | 6.10.3         | Wake Event Data Structures       |     |

|     | 6.10.4         | RMON Statistics                  |     |

|     | 6.10.5         | Ethernet MIB Statistics          |     |

|     | 6.10.6         | I/O Registers                    | 63  |

|     | 6.10.7         | PCI Configuration Registers      | 108 |

|     | 6.10.8         | EEPROM Fields                    |     |

|     | 6.10.9         | PCS Management Registers         |     |

| 7   |                | mum Ratings                      |     |

| 8   |                | ges                              |     |

| 9   |                | stics                            |     |

| 10  |                | racteristics                     |     |

| 11  | Physical Dimer | nsions                           | 136 |

#### 4 Pin Designations

| #  | Pin Name   | #  | Pin Name | #   | Pin Name | #   | Pin Name        |

|----|------------|----|----------|-----|----------|-----|-----------------|

| 1  | MDIO       | 53 | AD17     | 105 | VCCH     | 157 | ED5             |

| 2  | MDC/EWRAP  | 54 | AD16     | 106 | AD62     | 158 | ED4             |

| 3  | CRS/SIGDET | 55 | VCCH     | 107 | AD61     | 159 | ED3             |

| 4  | COL        | 56 | CBEN2    | 108 | AD60     | 160 | VCCH            |

| 5  | GND        | 57 | FRAMEN   | 109 | AD59     | 161 | ED2             |

| 6  | GTXCLK     | 58 | IRDYN    | 110 | GND      | 162 | ED1             |

| 7  | VCCH       | 59 | GND      | 111 | AD58     | 163 | ED0             |

| 8  | TXER/TXD9  | 60 | TRDYN    | 112 | AD57     | 164 | EA0/LEDDPLXN    |

| 9  | TXEN/TXD8  | 61 | DEVSELN  | 113 | AD56     | 165 | EA1/LEDLNK1000N |

| 10 | TXD7       | 62 | STOPN    | 114 | VCCH     | 166 | GND             |

| 11 | TXD6       | 63 | PERRN    | 115 | AD55     | 167 | EA2/LEDPWRN     |

| 12 | TXD5       | 64 | VCCH     | 116 | AD54     | 168 | EA3/EEDI        |

| 13 | TXD4       | 65 | SERRN    | 117 | AD53     | 169 | EA4/EESK        |

| 14 | GND        | 66 | PAR      | 118 | GND      | 170 | EA5/EEDO        |

| 15 | TXD3       | 67 | CBEN1    | 119 | AD52     | 171 | EA6/GPIO0       |

| 16 | TXD2       | 68 | GND      | 120 | GND      | 172 | PWRRSTN(VCCH)   |

| 17 | TXD1       | 69 | GND      | 121 | AD51     | 173 | EA7/GPIO1       |

| 18 | GND        | 70 | AD15     | 122 | VCCL     | 174 | GND             |

| 19 | TXD0       | 71 | VCCL     | 123 | AD50     | 175 | EA8             |

| 20 | VCCL       | 72 | AD14     | 124 | AD49     | 176 | EA9             |

| 21 | TXCLK      | 73 | AD13     | 125 | VCCH     | 177 | EA10            |

| 22 | WAKE       | 74 | AD12     | 126 | AD48     | 178 | EA11            |

| 23 | INTAN      | 75 | VCCH     | 127 | AD47     | 179 | EA12            |

| 24 | RSTN       | 76 | AD11     | 128 | GND      | 180 | EA13            |

| 25 | VCCH       | 77 | AD10     | 129 | AD46     | 181 | VCCL            |

| 26 | PCICLK     | 78 | GND      | 130 | AD45     | 182 | EA14/LEDLNK100N |

| 27 | GND        | 79 | AD9      | 131 | AD44     | 183 | EA15/LEDLNK10N  |

| 28 | GNTN       | 80 | AD8      | 132 | AD43     | 184 | GND             |

| 29 | REQN       | 81 | CBEN0    | 133 | AD42     | 185 | CLK125          |

| 30 | AD31       | 82 | AD7      | 134 | VCCH     | 186 | VCCH            |

| 31 | AD30       | 83 | AD6      | 135 | AD41     | 187 | TEST            |

| 32 | AD29       | 84 | VCCH     | 136 | GND      | 188 | GMII            |

| 33 | GND        | 85 | VCCL     | 137 | GND      | 189 | RSTOUT          |

| 34 | GND        | 86 | AD5      | 138 | AD40     | 190 | GND             |

| 35 | AD28       | 87 | GND      | 139 | VCCL     | 191 | PHYDPLXN        |

| 36 | VCCL       | 88 | GND      | 140 | AD39     | 192 | PHYLNK10N       |

| 37 | VCCH       | 89 | AD4      | 141 | AD38     | 193 | PHYLNK100N      |

Copyright © 2001, IC Plus Corp. All rights reserved. Preliminary, Specification subject to change without notice.

4/136

| #  | Pin Name | #   | Pin Name | #   | Pin Name | #   | Pin Name     |

|----|----------|-----|----------|-----|----------|-----|--------------|

| 38 | AD27     | 90  | AD3      | 142 | AD37     | 194 | PHYLNK1000N  |

| 39 | AD26     | 91  | AD2      | 143 | AD36     | 195 | RXD0         |

| 40 | AD25     | 92  | AD1      | 144 | VCCH     | 196 | RXD1         |

| 41 | AD24     | 93  | AD0      | 145 | AD35     | 197 | RXD2         |

| 42 | CBEN3    | 94  | GND      | 146 | GND      | 198 | RXD3         |

| 43 | GND      | 95  | ACK64N   | 147 | AD34     | 199 | RXD4         |

| 44 | IDSEL    | 96  | VCCH     | 148 | AD33     | 200 | RXD5         |

| 45 | AD23     | 97  | REQ64N   | 149 | AD32     | 201 | RXD6         |

| 46 | VCCH     | 98  | CBEN7    | 150 | VDET     | 202 | RXD7         |

| 47 | AD22     | 99  | CBEN6    | 151 | EECS     | 203 | RXDV/RXD8    |

| 48 | AD21     | 100 | CBEN5    | 152 | EWEN     | 204 | RXER/RXD9    |

| 49 | AD20     | 101 | CBEN4    | 153 | EOEN     | 205 | GND          |

| 50 | AD19     | 102 | GND      | 154 | GND      | 206 | RXCLK0/RXCLK |

| 51 | GND      | 103 | PAR64    | 155 | ED7      | 207 | VCCH         |

| 52 | AD18     | 104 | AD63     | 156 | ED6      | 208 | RXCLK1       |

TABLE 1: TC9021 Pin Designations

## 5 Signal Descriptions

| Signal Name | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RSTN        | INPUT       | <b>Reset, asserted LOW.</b><br>RSTN will cause the TC9021 to reset all of its functional blocks. RSTN must be asserted for a minimum duration of 10 PCICLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PCICLK      | INPUT       | <b>PCI Bus Clock.</b><br>This clock is used to drive the PCI bus interfaces and the internal DMA logic. All bus signals are sampled on the rising edge of PCICLK. PCICLK can operate from 0MHz to 66MHz.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GNTN        | INPUT       | <b>PCI Bus Grant, asserted LOW.</b><br>GNTN signals access to the PCI bus has been granted to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IDSEL       | INPUT       | <b>Initialization Device Select.</b><br>The ISEL is used to select the TC9021 during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INTAN       | OUTPUT      | Interrupt Request, asserted LOW.<br>The TC9021 asserts INTAN to request an interrupt, when any one of the<br>programmed interrupt event occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| WAKE        | OUTPUT      | Wake Event, assertion level is programmable.<br>The TC9021 asserts WAKE to signal the detection of a wake event. The<br>WAKE signal eventually drives the PCI bus PME# signal, but is not<br>intended to be directly connected to PME#. See the PCI Bus Power<br>Management Interface Specification for details on generating PME#<br>from WAKE.                                                                                                                                                                                                                                                                                    |

| REQN        | OUTPUT      | <b>Request, asserted LOW.</b><br>The TC9021 asserts REQN to request PCI bus master operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD[630]     | IN/OUT      | <b>PCI Bus Address/Data.</b><br>Address and data are multiplexed on the AD pins. Bits 0 through 31 carry the lower 32 bits of the physical address during the first clock cycle of a transaction, and carry data during the subsequent clock cycles. Bits 32 through 63 carry the upper 32 bits of the physical address during the first clock cycle of a transaction (if the Dual Address Cycle, or DAC command is used along with the assertion of REQ64N), and carry an additional 32 bits of data during subsequent clock cycles (if a 64 bit transaction has been negotiated through the assertion of both REQ64N and ACK64N). |

| CBEN[70]    | IN/OUT      | <b>PCI Bus Command/Byte Enable, asserted LOW.</b><br>Bus command and byte enables are multiplexed on the CBEN signals.<br>CBEN specify the bus command during the address phase transaction,<br>and carry byte enables during the data phase. CBEN bits 4 through 7<br>are reserved unless a 64 bit transaction has been negotiated through<br>the assertion of both REQ64N and ACK64N.                                                                                                                                                                                                                                             |

| Signal Name | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI         |             |                                                                                                                                                                                                                                                                                                                                                                                      |

| PAR         | IN/OUT      | <b>Parity.</b><br>PCI Bus parity is even across bits 0 through 31 of AD and bits 0 through 3 of CBEN. The TC9021 generates PAR during address and write data phases as a bus master, and during read data phase as a target. It checks for correct parity during read data phase as bus master, during every address phase as a bus slave, and during write data phases as a target. |

| FRAMEN      | IN/OUT      | <b>PCI Bus Cycle Frame, asserted LOW.</b><br>FRAMEN is asserted at the beginning of the address phase of the bus transaction and deasserted before the final transfer of the data phase of the transaction.                                                                                                                                                                          |

| IRDYN       | IN/OUT      | <b>Initiator Ready, asserted LOW.</b><br>A bus master asserts IRDYN to indicate valid data phases on AD during write data phases, and to indicate it is ready to accept data during read data phases. A target will monitor IRDYN.                                                                                                                                                   |

| TRDYN       | IN/OUT      | <b>Target Ready, asserted LOW.</b><br>A bus target asserts TRDYN to indicate valid read data phases, and to indicate it is ready to accept data during write data phases. A bus master will monitor TRDYN.                                                                                                                                                                           |

| DEVSELN     | IN/OUT      | <b>Device Select, asserted LOW.</b><br>The TC9021 asserts DEVSELN when it is selected as a target during a bus transaction. It monitors DEVSELN for any target to acknowledge a bus transaction initiated by the device.                                                                                                                                                             |

| STOPN       | IN/OUT      | <b>Stop, asserted LOW.</b><br>STOPN is driven by the slave target to inform the bus master to terminate the current transaction.                                                                                                                                                                                                                                                     |

| PERRN       | IN/OUT      | <b>Parity Error, asserted LOW.</b><br>The TC9021 asserts PERRN when it checks and detects a bus parity errors. When it is generating PAR output, the device monitors for any reported parity error on PERRN.                                                                                                                                                                         |

| SERRN       | OUTPUT      | System Error, asserted LOW.                                                                                                                                                                                                                                                                                                                                                          |

| REQ64N      | IN/OUT      | <b>64 Bit Transaction Request, asserted LOW.</b><br>The REQ64N signal is asserted by a bus master to indicate a preference for 64 bit transaction.                                                                                                                                                                                                                                   |

| ACK64N      | IN/OUT      | <b>64 Bit Transaction Acknowledgment, asserted LOW.</b><br>The ACK64N signal is asserted by a bus target which supports 64 bit transactions in response to REQ64N assertion.                                                                                                                                                                                                         |

| Signal Name | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI         |             |                                                                                                                                                                                                                                                                                                                                                                                         |

| PAR64       | IN/OUT      | <b>Parity.</b><br>PCI Bus parity is even across bits 32 through 63 of AD and bits 4 through 7 of CBEN. The TC9021 generates PAR64 during address and write data phases as a bus master, and during read data phase as a target. It checks for correct parity during read data phase as bus master, during every address phase as a bus slave, and during write data phases as a target. |

| VDET        | INPUT       | <b>Power Detect.</b><br>The device detects PCI bus power supply loss when VDET is LOW.                                                                                                                                                                                                                                                                                                  |

| Signal Name  | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII/GMII/TBI |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TXCLK        | INPUT       | <b>Transmit Clock.</b><br>TXCLK is a continuous clock supplied by the PHY to synchronize transmit data transfers when the TC9021 is configured in 10Mbps or 100Mbps Mode. The nominal rate of TXCLK is 2.5MHz for 10Mbps operation, and 25MHz for 100Mbps operation.                                                                                                                                                                               |

| TXD[70]      | OUTPUT      | <b>Transmit Data.</b><br>Eight bits of transmit data from the transmit MAC to the PHY device.<br>When the TC9021 is configured in GMII Mode, these signals represent<br>the entire transmit data bus. TXD are synchronized to the GTXCLK.<br>When the TC9021 is configured in TBI Mode, these pins represent the<br>lower 8 bits of the 10-bit transmit data bus. TXD are synchronized with<br>GTXCLK.                                             |

| TXEN/TXD8    | OUTPUT      | Transmit Enable/Transmit Data Bit 9.<br>When the TC9021 is configured in GMII mode, this signal is TXEN.<br>When asserted, TXEN/TXD8 indicates to the PHY that TXD carry valid<br>transmit data. TXEN/TXD8 is asserted with the first byte of the preamble<br>until the last byte of the frame data.<br>When the TC9021 is configured in TBI Mode, this signal is TXD[8], the<br>ninth transmit data bit.<br>TXEN/TXD8 is synchronous with GTXCLK. |

| TXER/TXD9    | OUTPUT      | <b>Transmit Error/Transmit Data Bit 10.</b><br>When the TC9021 is configured in GMII mode, this signal is TXER.<br>When asserted, TXER/TXD9 indicates to the PHY that an error symbol<br>should be transmitted in place of the TXD transmit data.<br>When the TC9021 is configured in TBI Mode, this signal is TXD[9], the<br>tenth transmit data bit. TXER/TXD9 is synchronous with GTXCLK.                                                       |

| GTXCLK       | OUTPUT      | <b>Gigabit Transmit Clock.</b><br>GTXCLK is a continuous clock supplied to the PHY to synchronize transmit data transfers when the device is configured in GMII Mode or TBI Mode. The nominal rate of GTXCLK is 125MHz.                                                                                                                                                                                                                            |

| Signal Name  | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII/GMII/TBI |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| COL          | INPUT       | <b>Collision.</b><br>When the TC9021 is configured in TBI Mode, COL is ignored and should be tied LOW.<br>When the TC9021 is configured in GMII Mode, COL is asserted by the PHY to signal a collision condition is detected on the physical medium. COL is asynchronous.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXD[70]      | INPUT       | Receive Data.<br>8 bits of receive data from the PHY device to the receive MAC. When<br>the TC9021 is configured in GMII Mode, these signals represent the<br>entire receive data bus. In GMII Mode, RXD are synchronized to the<br>RXCLK0/RXCLK.<br>When the TC9021 is configured in TBI Mode, these pins represent the<br>lower 8 bits of the 10-bit receive data bus. In TBI Mode, RXD are<br>synchronized with both RXCLK0/RXCLK and RXCLK1.                                                                                                                                                                                                                                                                                                                                                                                         |

| RXDV/RXD8    | INPUT       | <b>Receive Data Valid/Receive Data Bit 9.</b><br>When the TC9021 is configured in GMII Mode, this signal is RXDV, indicating valid frame data is present on the RXD pins. The PHY asserts RXDV/RXD8 before the SFD, and de-asserts it after the last data nibble of the frame. In GMII mode, RXDV/RXD8 is synchronous with RXCLK0/RXCLK.<br>When the TC9021 is configured in TBI Mode, this signal is RXD[8], the ninth receive data bit. In TBI mode, RXDV/RXD8 is synchronous with both RXCLK0/RXCLK and RXCLK1.                                                                                                                                                                                                                                                                                                                       |

| RXER/RXD9    | INPUT       | Receive Error/Receive Data Bit 10.<br>When the TC9021 is configured in GMII Mode, this signal is RXER, an indication from the PHY that an error has been detected during frame data reception. In GMII mode, RXER/RXD9 is synchronous with RXCLK0/RXCLK.<br>When the TC9021 is configured in TBI Bode, this signal is RXD[9], the tenth receive data bit. In TBI mode, RXER/RXD9 is synchronous with both RXCLK0/RXCLK and RXCLK1.                                                                                                                                                                                                                                                                                                                                                                                                       |

| RXCLK0/RXCLK | INPUT       | <b>Receive Clock Zero.</b><br>When the TC9021 is configured in GMII Mode, RXCLK0/RXCLK provide<br>the timing reference for RXD, RXDV/RXD8, and RXER/RXD9 signals.<br>The nominal rate for RXCLK0/RXCLK is 125MHz.<br>When the TC9021 is configured in TBI Mode, RXCLK0/RXCLK and<br>RXCLK1 together provide a timing reference for the 10-bit data bus<br>defined by RXD, RXDV/RXD8, and RXER/RXD9 signals.<br>RXDLK0/RXCLK rising edges correspond to odd-numbered<br>code-groups appearing on the 10-bit data bus defined by RXD,<br>RXDV/RXD8, and RXER/RXD9 signals. RXCLK0/RXCLK and RXCLK1<br>are supplied by the PHY based on the receive clock recovery circuit.<br>RXCLK0/RXCLK and RXCLK1 are 180 degrees out of phase. Nominal<br>rate for RXCLK0/RXCLK is 62.5MHz. RXCLK0/RXCLK may be<br>stretched, but is never shortened. |

| Signal Name  | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII/GMII/TBI |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXCLK1       | INPUT       | Receive Clock One.<br>When the TC9021 is configured in GMII Mode, RXCLK1 is ignored and<br>should be tied LOW.<br>When the TC9021 is configured in TBI mode, RXCLK0/RXCLK and<br>RXCLK1 together provide a timing reference for the 10-bit data bus<br>defined by RXD, RXDV/RXD8, and RXER/RXD9 signals. RXCLK1<br>rising edges correspond to even-numbered code-groups appearing on<br>the 10-bit data bus defined by RXD, RXDV/RXD8, and RXER/RXD9<br>signal. RXCLK0/RXCLK and RXCLK1 are supplied by the PHY based<br>on the receive clock recovery circuit. RXCLK0/RXCLK and RXCLK1 are<br>180 degrees out of phase. Nominal rate for RXCLK1 is 62.5MHz.<br>RXCLK1 may be stretched, but is never shortened. |

| CRS/SIGDET   | INPUT       | <b>Carrier Sense/Signal Detect.</b><br>When the TC9021 is configured in GMII Mode, this signal is CRS, asserted by the PHY to signal a non-idle medium with either transmit or receive activity detected. CRS is asynchronous.<br>When the TC9021 is configured in TBI Mode, this signal is SIGDET. An indication from the media transceiver that a signal is present.                                                                                                                                                                                                                                                                                                                                           |

| MDC/EWRAP    | OUTPUT      | Management Data Clock/Electrically Wrap.<br>When the TC9021 is configured in GMII Mode, this signal is MDC which<br>is used to synchronize the read and write operations of MDIO.<br>When the TC9021 is configured in TBI Mode, this signal is EWRAP<br>which is asserted HIGH to indicate the PHY device should internally<br>loop transmit data to the receiver, and should keep the transmitter serial<br>outputs in a static state. MDC/EWRAP asserted LOW indicates the PHY<br>device should operate normally.                                                                                                                                                                                              |

| MDIO         | IN/OUT      | Management Data Input/Output.<br>When the TC9021 is configured in TBI Mode, MDIO is ignored and<br>should be tied HIGH through a resistor ( $10k\Omega$ or higher).<br>When the device is configured in GMII Mode, MDIO carries<br>management data for the management port read and write operations.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Signal Name   | Signal Type | Signal Description                                                                                                                                                   |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY INTERFACE |             |                                                                                                                                                                      |

| PHYLNK1000N   | INPUT       | <b>PHY Link 1000Mbps Status, asserted LOW.</b><br>PHYLNK1000N is driven by the physical layer device. It is asserted to signal a functional 1000Mbps link (link up). |

| PHYLNK100N    | INPUT       | <b>PHY Link 100Mbps Status, asserted LOW.</b><br>PHYLNK100N is driven by the physical layer device. It is asserted to signal a functional 100Mbps link (link up).    |

| PHYLNK10N     | INPUT       | <b>PHY Link 10Mbps Status, asserted LOW.</b><br>PHYLNK10N is driven by the physical layer device. It is asserted to signal a functional 10Mbps link (link up).       |

| Signal Name   | Signal Type | Signal Description                                                                                                                                                                                                                                                     |  |  |  |

|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PHY INTERFACE |             |                                                                                                                                                                                                                                                                        |  |  |  |

| PHYDPLXN      | INPUT       | <b>PHY Duplex Status, assertion level is programmable.</b><br>PHYDPLXN is driven by the physical layer device. It is asserted to indicate a full duplex link, and de-asserted to indicate a half duplex link.<br>PHYDPLXN is undefined when PHYLNK10N is not asserted. |  |  |  |

| Signal Name                                                    | Signal Type | Signal Description                                                                                                                                       |  |

|----------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EEPROM INTERFACE(SEE ALSO EXPANSION ROM INTERFACE/LED DRIVERS) |             |                                                                                                                                                          |  |

| EECS                                                           | OUTPUT      | EEPROM Chip Select.<br>EECS is asserted by the TC9021 to access the EEPROM. EECS is<br>connected directly to the chip select input of the EEPROM device. |  |

| Signal Name                         | Signal Type | Signal Description                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EXPANSION ROM INTERFACE/LED DRIVERS |             |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| ED[70]                              | IN/OUT      | Expansion ROM Data.<br>ED provide data access to the expansion ROM.                                                                                                                                                                                                                                                                                    |  |  |  |

| EA15/LEDLNK<br>10N                  | OUTPUT      | <b>Expansion ROM Address Bit 15/10Mbps Link Status LED.</b><br>EA15/LEDLNK10N is a shared pin assuming the value of bit 15 of t<br>expansion ROM address during accesses to the expansion ROM (s<br>ExpRomAddre and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA15/LEDLNK10N is t<br>10Mbps Link Status LED driver signal. |  |  |  |

| EA14/LEDLNK<br>100N                 | OUTPUT      | <b>Expansion ROM Address Bit 14/100Mbps Link Status LED.</b><br>EA14/LEDLNK100N is a shared pin assuming the value of bit 14 of the expansion ROM address during accesses to the expansion ROM (see ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA14/LEDLNK100N is the 100Mbps Link Status LED driver signal. |  |  |  |

| EA[138]                             | OUTPUT      | <b>Expansion ROM Address.</b><br>The EA along with EA7/GPIO1, EA6/GPIO0, EA5/EEDO, EA4/EESK, EA3/EEDI, EA2/LEDPWRN, EA1/LEDLNK1000N, and EA0/LEDDPLXN carry the address to the expansion ROM.                                                                                                                                                          |  |  |  |

| EA7/GPIO1                           | IN/OUT      | <b>Expansion ROM Address Bit 7/General Purpose Input/Output 1.</b><br>EA7/GPIO1 is a shared pin assuming the value of bit 7 of the expansion<br>ROM address during accesses to the expansion ROM (see<br>ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA7/GPIO1 is the general<br>purpose input/output bit 1.  |  |  |  |

| Signal Name         | Signal Type                         | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| EXPANSION ROM       | EXPANSION ROM INTERFACE/LED DRIVERS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| EA6/GPIO0           | IN/OUT                              | <b>Expansion ROM Address Bit 6/General Purpose Input/Output 0.</b><br>EA6/GPIO0 is a shared pin assuming the value of bit 6 of the expansion<br>ROM address during accesses to the expansion ROM (see<br>ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA6/GPIO0 is the general<br>purpose input/output bit 0.                                                                                                                              |  |  |  |  |  |

| EA5/EEDO            | IN/OUT                              | Expansion ROM Address Bit 5/EEPROM Data Output.<br>EA5/EEDO is a shared pin assuming the value of bit 5 of the expansion<br>ROM address during accesses to the expansion ROM (see<br>ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA5/EEDO is an input<br>connected directly to the data output of the EEPROM device.                                                                                                                      |  |  |  |  |  |

| EA4/EESK            | OUTPUT                              | <b>Expansion ROM Address Bit 4/EEPROM Serial Clock.</b><br>EA4/EESK is a shared pin assuming the value of bit 4 of the expansion<br>ROM address during accesses to the expansion ROM (see<br>ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA4/EESK is the clock<br>(frequency 150kHz) used to synchronize the EEPROM data access with<br>EA3/EEDI and EA5/EEDO. EA4/EESK is connected directly to the clock<br>input of the EEPROM device. |  |  |  |  |  |

| EA3/EEDI            | OUTPUT                              | <b>Expansion ROM Address Bit 3/EEPROM Data Input.</b><br>EA3/EEDI is a shared pin assuming the value of bit 3 of the expansion<br>ROM address during accesses to the expansion ROM (see<br>ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accessed, EA3/EEDI is the data input<br>to an EEPROM. EA3/EEDI is connected directly to the data input of the<br>EEPROM device.                                                                              |  |  |  |  |  |

| EA2/LEDPWRN         | OUTPUT                              | <b>Expansion ROM Address Bit 2/Power Status LED.</b><br>EA2/LEDPWRN is a shared pin assuming the value of bit 2 of the expansion ROM address during accesses to the expansion ROM (see ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accesses, EA2/LEDPWRN is the Power Status LED driver signal.                                                                                                                                                     |  |  |  |  |  |

| EA1/LEDLNK<br>1000N | OUTPUT                              | <b>Expansion ROM Address Bit 1/1000Mbps Link Status LED.</b><br>EA1/LEDLNK1000N is a shared pin assuming the value of bit 1 of the expansion ROM address during accesses to the expansion ROM (see ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accesses, EA1/LEDLNK1000N is the 1000Mbps Link Status LED driver signal.                                                                                                                             |  |  |  |  |  |

| EA0/LEDDPLXN        | OUTPUT                              | <b>Expansion ROM Address Bit 0/Power Status LED.</b><br>EA0/LEDDPLXN is a shared pin assuming the value of bit 0 of the expansion ROM address during accesses to the expansion ROM (see ExpRomAddr and ExpRomData registers).<br>If the expansion ROM is not being accesses, EA0/LEDDPLXN is the Duplex Status LED driver signal.                                                                                                                                                  |  |  |  |  |  |

| Signal Name   | Signal Type                         | Signal Description           |  |  |  |

|---------------|-------------------------------------|------------------------------|--|--|--|

| EXPANSION ROM | EXPANSION ROM INTERFACE/LED DRIVERS |                              |  |  |  |

| EWEN          | OUTPUT                              | Expansion ROM Write Enable.  |  |  |  |

| EOEN          | OUTPUT                              | Expansion ROM Output Enable. |  |  |  |

| Signal Name   | Signal Type | Signal Description                                                                                                                                                                                        |  |  |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MISCELLANEOUS |             |                                                                                                                                                                                                           |  |  |

| RSTOUT        | OUTPUT      | <b>Reset Output.</b><br>RSTOUT is the reset output from the device. The TC9021 will assert<br>RSTOUT when it is being reset. RSTOUT is intended to be used as<br>reset to other circuitry on the adapter. |  |  |

| TEST          | INPUT       | <b>Test Mode.</b><br>TEST asserted HIGH during reset places the TC9021 in TEST mode.<br>For normal operation, TEST is LOW.                                                                                |  |  |

| GMII          | INPUT       | <b>Physical Layer Mode.</b><br>GMII asserted HIGH places the TC9021 in GMII Mode. GMII asserted<br>LOW places the device in TBI Mode.                                                                     |  |  |

| CLK125        | INPUT       | <b>125MHz Clock.</b><br>CLK125 is the reference clock used for the TC9021's internal logic.                                                                                                               |  |  |

| Signal Name      | Signal Type | Signal Description                                |  |  |  |

|------------------|-------------|---------------------------------------------------|--|--|--|

| POWER AND GROUND |             |                                                   |  |  |  |

| VCCH             | POWER       | +3.3 volt power supply for input/output circuits. |  |  |  |

| GND              | GROUND      | +3.3 volt return.                                 |  |  |  |

| VCCL             | POWER       | +2.5 volt power supply for internal core logic.   |  |  |  |

| GND              | GROUND      | +2.5 volt return.                                 |  |  |  |

### 6 Functional Description

#### 6.1 PCI Bus Interface

The PCI Bus Interface (PBI) implements the procedures and algorithms needed for the TC9021 to operate in a PCI bus slot as either a PCI bus master or slave. The PBI is also responsible for managing the DMA interfaces and the host processor access to the TC9021 registers. Arbitration logic within the PBI block accepts bus requests from the TxDMA Logic and RxDMA Logic. The PBI also manages interrupt generation for a host processor.

The TC9021 supports all of the PCI memory commands and decides on a burst-by-burst basis which command to use in order to maximize bus efficiency. The list of PCI memory commands is shown below. Memory Read (MR) Memory Read Line (MRL) Memory Read Multiple (MRM) Memory Write (MW) Memory Write Invalidate (MWI)

MR is used for all fetches of descriptor information. For reads of transmit frame data, MR, MRL, or MRM is used, depending upon the remaining number of bytes in the fragment, the amount of free space in the TxFIFO, and whether the RxDMA Logic is requesting a bus master operation.

MW is used for all descriptor writes. Writes of receive frame data use either MW or MWI, depending upon the remaining number of bytes in the fragment, the amount of frame data in the RxFIFO, and whether the TxDMA Logic is requesting a bus master operation.

The TC9021 provides a set of registers that control the PCI burst behavior. These registers allow a trade-off to be made between PCI bus efficiency and underrun/overrun frequency.

In support of bus isolation requirements for system states in which the TC9021 is powered down, all TC9021 PCI outputs will enter the tri-state condition when the RSTN is active.

### 6.2 DMA

The TC9021 implements scatter gather Direct Memory Access (DMA) for moving data from the device to/from the host's system memory. Two independent DMA processes are used to transfer transmit data from host system memory to the TC9021 (transmit DMA), and to transfer receive data from the device to host system memory (receive DMA).

#### 6.2.1 Transmit DMA

To utilize the TC9021 to transmit data onto a Gigabit Ethernet network, the data must be transferred from the host's system memory over the PCI bus.

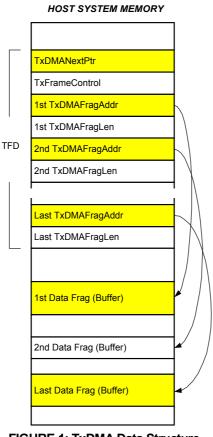

The locations within system memory which contain the data to be transmitted are indicated to the TC9021 using Transmit Frame Descriptors.

The Transmit Frame Descriptor (TFD) is a data structure containing fields specifying a pointer to another TFD (the TFDNextPtr field), control information (the TFC field), and from one to 15 pointers to locations within system memory containing the Ethernet frame data (the FragInfo fields). The TFD is used to indicate to the TC9021 which blocks of system memory comprise the Ethernet frame data to be transmitted. Each Ethernet frame is described by one and only one TFD.

FIGURE 1: TxDMA Data Structure

The TFD format is covered in the Registers and Data Structures section. TFDs are typically grouped into linked lists (called TFD lists) within system memory by the host system.

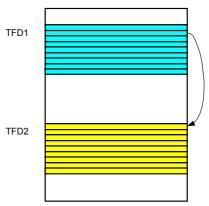

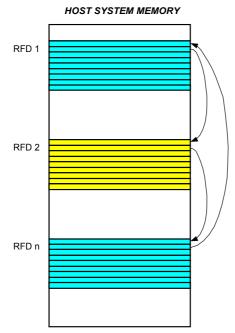

The TFDNextPtr field is used to link one TFD to the next in the list. The resulting linked list of TFDs is referred to as the TxDMAList, as shown in Figure 2.

HOST SYSTEM MEMORY

FIGURE 2: TxDMA List of Two TFDs

The location of the first TFD in a TFD list is indicated to the device by writing the memory location of the first TFD to the TFDListPtr register.

Upon reset, the TFDListPtr register contains a null value (0x00000000) indicating to the device that there is no data to transfer via the transmit DMA process. Once a TFD list has been created in system memory, and the location of the first TFD in the list has been written to the TFDListPtr register, the transmit DMA process begins.

There are several cases during transmit DMA operation in which host system interrupts are generated.

See section 6.3.1 for details on transmit DMA interrupts.

### 6.2.2 Receive DMA

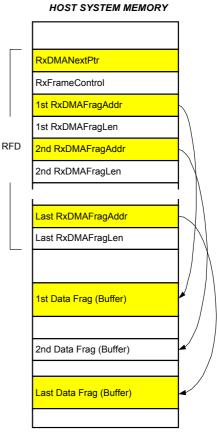

To utilize the TC9021 to receive data from a Gigabit Ethernet network, the received data must be transferred from the device to the host's system memory via the PCI bus by DMA. The locations within system memory reserved for the received data are indicated to device using Receive Frame Descriptors.

The Receive Frame Descriptor (RFD) is a data structure containing fields specifying a pointer to another RFD (the RFDNextPtr field), status information (the RFS field), and one pointer (the Frag-Info field) to a unique, contiguous block of system memory which is reserved for holding the

received data. Typically, one RFD will completely specify a single received Ethernet frame. While it is possible to use multiple RFDs to describe a single Ethernet frame, it is not possible to describe multiple Ether-net frames with a single RFD. The RFD format is described in section 6.10.2.

RFDs are typically grouped into linked lists (called RFD lists) within system memory by the host system, as shown below:.

#### Figure 3: RxDMA List Shown in Ring Configuration

The RFDNextPtr field is used to link RFDs within the list. The location of the first RFD in a RFD list is indicated to the device by writing the memory location of the first RFD to the RFDListPtr register.

Upon reset, the RFDListPtr register contains a value of 0x000000000 indicating to the device that there is no room in host system memory reserved for received data. The RFD format is covered in the Registers and Data Structures section, while graphically shown below in Figure 4.

Figure 4: RxDMA Data Structure

Once a RFD list has been created in system memory, and the location of the first RFD in the list has been written to the RFDListPtr register, the receive DMA process begins.

There are several cases during receive DMA operation in which host system interrupts are generated.

See section 6.3.3 for details on receive DMA interrupts.

#### 6.3 Interrupts

The TC9021generates host system processor interrupts via the PCI bus based on events related to transmit and receive DMA operation. It is the responsibility of the host system to detect these interrupts, identify the corresponding condition which caused the interrupt, and take

the appropriate action.

At gigabit per second data rates, interrupts related to Gigabit Ethernet frame transmission and reception can quickly overwhelm a host system processor. The device incorporates several features for minimizing the number of interrupts generated.

These features should be utilized to achieve maximum system performance in Gigabit Ethernet networks.

### 6.3.1 Transmit DMA Interrupts

Interrupts can be generated by the device based on a number of events related to transmit DMA operation:

- TxDMAComplete interrupt is issued after successful transfer of an Ethernet frame to the device via transmit DMA with the TxDMAIndi-cate bit in the TFD's TFC field is a logic 1. Use of this interrupt is not recommended due to the frequency of transmit DMA operations in a Gigabit Ethernet network.

- TxComplete interrupt (frame transmission complete without error) is issued after successful transmission of an Ethernet frame which has already been transferred to the device with the TxIndicate bit in the TFD's TFC field is a logic 1. A recommended use of this feature is to avoid setting the TxIndicate bit in every TFD, but instead only set the TxIndicate bit in the last TFD of a TFDList, or in every Nth frame (where N>1).

- TxComplete interrupt (frame transmission encountered an error) is issued if an error occurs during transmission of an Ethernet frame which has already been transferred to the device independent of the TxIndicate bit setting in the TFD's TFC field. When an error occurs, the transmit MAC of the device is disabled (and must be re-enabled to resume operation). Transmit DMA operation continues in spite of transmit errors except for the case of a transmit underrun error (indicated by the TxUnderrun bit in the TxStatus register). To resume transmit DMA operation after a transmit underrun error, the transmit DMA, transmit FIFO, and transmit MAC functions within TC9021 must be reset.

• IntRequested interrupt is issued after expiration of the TC9021 Countdown timer register. The Countdown timer register can be programmed to generate an interrupt at fixed intervals.

A common use of interrupts during transmit DMA operation is to determine which TFDs have been successfully transmitted so the host system can free the memory occupied by old TFDs. Interrupts however usually incur a significant cost in terms of host system performance, requiring a large percentage of processor time to service. While interrupts are expensive, memory is usually abundant, therefore a trade off which minimizes interrupts in exchange for more memory usage is desirable.

## 6.3.2 "Interrupt-Less" Transmit DMA

TC9021's transmit DMA can operate without generating host system processor interrupts. In this mode of operation, the host system does not set the TxIndicate or TxDMAIndicate bits in the TFC field of any TFDs used to transfer Ethernet frames from system memory. Thus, an interrupt is not issued by the device to indicate successful DMA transfer or successful transmission of each Ethernet frame. An interrupt will only be issued by the device in the event of a transmit error, but this case should be rare.

Without the use of interrupts, the device provides another mechanism for the host system to determine which Ethernet frames have been successfully transmitted. This mechanism allows the host system to free memory locations holding old TFD lists. This "interrupt-less" mechanism involves using the TxFrameId field of the TxStatus register.

The TxFrameld field of the TxStatus register indicates the last Ethernet frame which was successfully transmitted. Using this information, the host system can infer successful transmission of all Ethernet frames up to the frame indicated by the TxFrameld field of the TxStatus register. Thus, the host system decides when to poll the TxFrameld field of the TxStatus register (for example, when the amount of memory occupied by old TFD lists becomes excessive) and avoid generation of processor intensive interrupts by the device.

### 6.3.3 Receive DMA Interrupts

Interrupts can be generated by the device based on a number of events related to receive DMA operation:

- RxDMAComplete interrupt is issued after successful transfer of one or more Ethernet frames (based on the interrupt coalescing configuration) from the device to the host system memory. Interrupt coalescing should he used in conjunction with the **RxDMAComplete** interrupt given the frequency of frame receipts in a Gigabit Ethernet network.

- RxDMAPriority interrupt is issued if a received Ethernet frame contains a Tag Control Information field with priority greater than or equal to the priority set in the RxDMAIntCtrl register.

- RFDListEnd interrupt is issued if the end of the RFD list is reached (indicated by an RFDNextPtr field with a value of 0x000000000), or a RFD with the RFDDone bit of the RFS field with a value of logic 1 is encountered.

#### 6.3.4 Receive DMA Interrupt Coalescing

A common use of interrupts during receive DMA operation is to indicate when new Ethernet frames have been transferred to host system memory.

Interrupts however usually incur a significant cost in terms of host system performance, requiring a large percentage of processor time to service. One way to improve the performance of the host system is to optimize the number of interrupts issued by the device related to receive DMA operation.

Depending upon the arrival rate of Ethernet frames and user programmable parameters, a single interrupt can be used to indicate multiple Ethernet frames have been received. The host will be able to handle multiple received frames within the same interrupt service routine.

While minimizing interrupts can improve host system performance, it can also require more host system memory usage, and increase network latency. Therefore, a balance between interrupt frequency and network latency must be reached to optimize performance.

## 6.4 ACPI

The TC9021 supports operating system directed power management according to the ACPI specification.

Power management registers in the PCI configuration space, as defined by the PCI Bus Power Management Interface specification, Revision 1.0 are described in section 6.10.

### 6.4.1 Power Management States

The TC9021 supports several power management states. The PowerState field in the PowerMgmtCtrl register determines TC9021's current power state.

The power states are defined as follows:

- D0 Uninitialized (power state 0, D0u) is entered as a result of hardware reset, or after a transition from D3 Hot to D0. This state is the same as D0 Active except that the PCI configuration registers are uninitialized. In this state, the device is unable to respond to PCI I/O or memory cycles and can not operate as a PCI master; it responds to PCI configuration cycles only. The device cannot signal wake events (WAKE/PMEN) from the D0u state.

- D0 Active (power state 0) is the normal operational power state for the device. In this state, the PCI configuration registers have been initialized by the system, including the IoSpace, MemorySpace, and BusMaster bits in the Config Command register, so the device is able to respond to PCI I/O, memory and configuration cycles and can operate as a PCI master. In Forced Configuration mode or mode (set WakeOnLan by the WakeOnLanEnable bit in the WakeEvent register), TC9021 bypasses the D0u state and will enter the D0a state after power up or hardware reset. The device cannot signal wake events (WAKE/PMEN) from the D0a state.

- D1 (power state 1) is a "light-sleep" state. The device optionally supports this state determined by the D1Support bit in the ConfigParm word in the EEPROM. The D1 state allows transition back to D0 with no

delay. In this state, the device responds to PCI configuration accesses, to allow the system to change the power state. In D1 the device does not respond to any PCI I/O or memory accesses. The TC9021's function in the D1 state, if power management events are enabled (PmeEn bit set), is to recognize wake events and pass them on to the system by asserting the PMEN signal on the PCI bus.

- D2 (power state 2) is a partial power-down state. The device optionally supports this state determined by the D2Support bit in the ConfigParm word in the EEPROM. D2 allows a faster transition back to D0 than is possible from the D3 state. In this state, the device responds to PCI configuration accesses, to allow the system to change the power state. In D2 the device does not respond to any PCI I/O or memory accesses. The TC9021's function in the D2 state, if power management events are enabled (PmeEn bit set), is to recognize wake events and pass them on to the system by asserting the PMEN signal on the PCI bus.

- D3 Hot (power state 3, D3h) is the power down state for the device if power management events are disabled (via PmeEn bit in the PowerMamtCtrl register). In D3 Hot, the device loses all PCI configuration information except. for the value in PowerState. In this state, the device responds to PCI configuration accesses, to allow the system to change the power state back to D0 Uninitialized. In D3 Hot, the device does not respond to any PCI I/O or memory accesses. The TC9021's main responsibility in the D3 Hot state, if power management events are enabled (PmeEn bit set), is to recognize wake events and signal those to the system by asserting the PMEN signal on the PCI bus.

- D3 Cold (power state 3, D3c) is the power down state for the device if power management events are disabled (via PmeEn bit in the PowerMgmtCtrl register). When power is restored, the system guarantees the assertion of hardware reset, which puts the device into the D0 Uninitialized state. The TC9021's main responsibility in the D3 Cold state, if power management events are enabled (PmeEn bit set), is to recognize wake events and signal those to the system by asserting the PMEN signal on the PCI bus.

Since the PCI bus power is removed during D3 Cold state, the device requires auxiliary power supply to support power management event detection.

## 6.5 Wake On LAN

Wake on LAN is a key component of the IBM/Intel® Advanced Manageability Alliance (AMA) initiative.

The TC9021 implements a portion of the Wake On LAN functionality defined by the AMA initiative. Specifically, the device can be configured to respond to wake up frames sent by a Wake On LAN management station.

### 6.5.1 Power Management Events

The TC9021 can generate power management events, sometimes also called wake events, to the host system as a result of Wake Packet reception, Magic Packet reception, or due to a change in the link status. The WakeEvent register gives the host system control over which of these events are passed to the system. Wake events are signaled over the PCI bus using the PMEN signal.

A wake event can only be recognized if the device is in one of the D1, D2, or D3 power states. When the device is in either of the two D0 power states, it will not be able to signal wake events.

When a desired wake event occurs, the device sets the appropriate event bit in the WakeEvent register, sets the PmeStatus bit in the PowerMgmtCtrl register, and asserts the WAKE/PMEN pin.

The host system responds to PMEN by scanning the power management configuration registers of all devices, finding the PmeStatus set in TC9021's PowerMgmtCtrl register. The operating system then clears the PmeEn bit in the PowerMgmtCtrl register causing WAKE/PMEN to be de-asserted.

### 6.5.1.1 Wake Packet

A Wake Packet event is controlled by the WakePktEnable bit in WakeEvent register. The WakePktEnable bit has no effect when TC9021 is in the D0 power state, as the wake process can

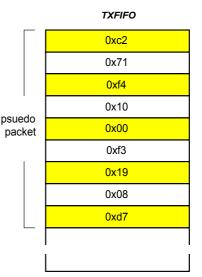

only take place in states D1, D2, or D3. When the device detects a Wake Packet, it signals a wake event on WAKE (if WAKE assertion is enabled), and sets the WakePktEvent bit in the WakeEvent register. The device can signal that a wake event has occurred when it receives a pre-defined frame from another station. The host system transfers a set of frame data patterns into the transmit FIFO using the TxDMA function before placing the device in a power-down state. Once powered down, the device compares receive frames with the frame patterns in the transmit FIFO. When a matching frame is received (and also passes the filtering mode set in the ReceiveMode register), a wake event is signaled.

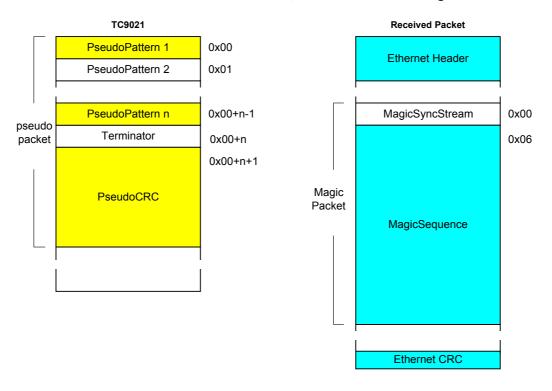

Frame patterns are written to the transmit FIFO in a single "pseudo-packet". Prior to transferring this pseudo-packet, the host system should first set the TxReset in the AsicCtrl (to reset the transmit FIFO pointers and prevent transmission) then prepare a TFD that points to a single data buffer. The buffer should contain one or more frame patterns placed contiguously. The number of frame patterns is limited by the transmit FIFO size. The FragLen field in the TFD must exactly equal the sum of the frame pattern bytes. Also, the host system must set the WordAlian field to 'x1' in the TFC field of the TFD to prevent frame word-alignment. Finally, the host system must write the TFD's address to the TFDListPtr register to transfer the frame into the transmit FIFO.

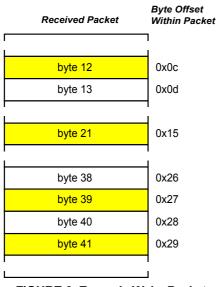

The frame patterns in the transmit FIFO specify which bytes in the incoming frames are to be examined. A CRC is calculated over these bytes and compared with a CRC value supplied in the frame pattern. This matching technique may result in false wake events being reported to the host system. Each wake packet pattern contains one or more byte-offset/byte-count pairs, an end-of-pattern symbol, and a 4-byte CRC value. The byte-offset indicates the number of frame bytes to be skipped in order to reach the next group of bytes to be included in the CRC calculation. The byte-count. indicates the number of bytes in the next group to be included in the CRC calculation. End-of pattern, which is a byte value of 0x00, indicates the end of the pattern for that wake frame. Immediately following the end-of-pattern is a 4-byte CRC. The CRC calculation uses the same polynomial as the Ethernet MAC FCS. The pseudo packet frame patterns are described in section 6.10.

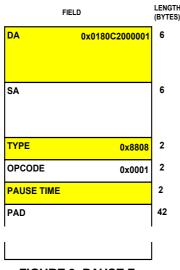

An example pseudo-packet (based on the ARP packet example from Appendix A of the "OnNow Network Device Class Power Management Specification") loaded into the transmit FIFO of the TC9021 is shown in Figure 5.

FIGURE 5: Example Psuedo Packet