# DECchip 21130 PCI Integrated Graphics and Video Accelerator

# **Technical Reference Manual**

Order Number: EC-QD2QC-TE

**Revision/Update Information:**

This manual supersedes the *DECchip 21130 PCI Integrated Graphics and Video Accelerator Technical Reference Manual* (EC-QD2QB-TE). It describes chip revision DC7538C.

Digital Equipment Corporation Maynard, Massachusetts

#### November 1995

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1995. All rights reserved. Printed in U.S.A.

AccuLook, DEC, DECchip, DECsystem, Digital, Digital Semiconductor, OpenVMS, RapiDraw, VAX, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

Digital Semiconductor is a Digital Equipment Corporation business.

Apple is a registered trademark of Apple Computer, Inc. Brooktree is a registered trademark and RAMDAC is trademark of Brooktree Corporation. DDC, VAFC, and VESA are trademarks of the Video Electronics Standards Association. Hercules is a registered trademark of Hercules Computer Technology, Inc. Intel and Pentium are registered trademarks of Intel Corporation. Microsoft, MS, and Win32 are registered trademarks and Windows and Windows NT are trademarks of Microsoft Corporation. MIPS is a trademark of MIPS Computer Systems, Inc. Motorola is a registered trademark of Motorola, Inc. OpenGL is a registered trademark of Silicon Graphics Inc. OSF/1 is a registered trademark of Philips International B.V. UNIX is a registered trademark in the United States and other countries licensed exclusively through X/Open Company Limited.

All other trademarks and registered trademarks are the property of their respective holders.

# Contents

| Pı | eface .    |                                                  | xix        |

|----|------------|--------------------------------------------------|------------|

| 1  | Introdu    | iction                                           |            |

|    | 1.1<br>1.2 | Features                                         | 1–1<br>1–5 |

|    | 1.3        | Basic Programming Model                          | 1–5        |

|    | 1.3.1      | Extensions to the Basic Programming Model        | 1–6        |

|    | 1.4        | Chip Revisions                                   | 1–7        |

| 2  | Interna    | I Architecture                                   |            |

|    | 2.1        | PCI Interface                                    | 2–1        |

|    | 2.1.1      | PCI Registers                                    | 2–1        |

|    | 2.2        | Command FIFO                                     | 2–1        |

|    | 2.3        | Command Parser                                   | 2–3        |

|    | 2.3.1      | Pixel-Processing Pipeline Coherence              | 2–3        |

|    | 2.3.2      | Frame Buffer Writes                              | 2–4        |

|    | 2.3.2.1    | Fill Mode                                        | 2–4        |

|    | 2.3.2.2    | Bresenham Setup HardwareBresenham Setup Hardware | 2–4        |

|    | 2.4        | Pixel Engine                                     | 2–4        |

|    | 2.5        | Memory Controller                                | 2–5        |

|    | 2.5.1      | Pixel Merge                                      | 2–5        |

|    | 2.5.2      | Write Buffer                                     | 2–6        |

|    | 2.5.3      | Frame Buffer and Device Access Requests          | 2–6        |

|    | 2.6        | Core Registers                                   | 2–7        |

|    | 2.7        | DMA Read FIFO                                    | 2–7        |

|    | 2.8        | Copy Buffer                                      | 2–8        |

|    | 2.9        | Frame Buffer and Device Access                   | 2–8        |

|    | 2.10       | Generic Peripheral Port                          | 2–8        |

|    | 2.11       | VGA Subsystem                                    | 2–9        |

|    | 2.12       | Frame Buffer Memory                              | 2–9        |

|    | 2.12.1     | Frame Buffer Configurations                      | 2–10       |

| 2.12.2 | Hardware Mode Restrictions | 2–10 |

|--------|----------------------------|------|

| 2.13   | Video Back End             |      |

| 2.13.1 |                            |      |

| 2.13.2 | Video Refresh              | 2–11 |

| 2.13.3 | Pixel Occlusion Bitmap     | 2–11 |

| 2.13.4 | Cursor Generation          |      |

| 2.13.5 | VAFC Port                  | 2–12 |

| 2.13.6 | Palette and DAC            | 2–13 |

| 2.14   | Clocks and Clock Control   | 2–13 |

# 3 Pinout

| 3.1 | Signal List                       | 3–1  |

|-----|-----------------------------------|------|

| 3.2 | Signal Descriptions               | 3–4  |

| 3.3 | Signals by Function and Direction | 3–11 |

# 4 Electrical Specifications

| 4.1   | PCI Electrical Specification Conformance         | 4–1  |

|-------|--------------------------------------------------|------|

| 4.2   | Absolute Maximum Ratings                         | 4–1  |

| 4.3   | Normal Operating Conditions                      | 4–2  |

| 4.4   | Supply Current and Power Dissipation             | 4–2  |

| 4.4.1 | Test Conditions                                  | 4–2  |

| 4.5   | dc Specifications                                | 4–3  |

| 4.5.1 | Operating Specifications                         | 4–5  |

| 4.6   | ac Specifications                                | 4–6  |

| 4.6.1 | Parameters for PCI Clock Domain Signals          | 4–7  |

| 4.6.2 | PCI Cycle Timing                                 | 4–10 |

| 4.6.3 | Memory Cycle Timing                              | 4–16 |

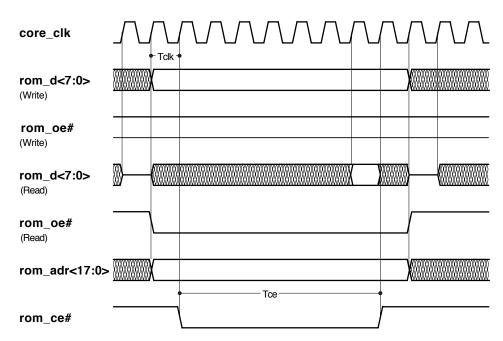

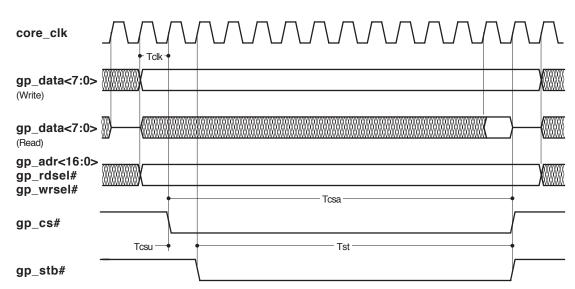

| 4.6.4 | ROM and GPP Data Cycle Timing                    | 4–21 |

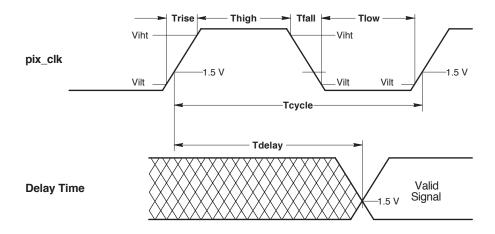

| 4.6.5 | Parameters for Pixel Clock and VAFC Clock Domain |      |

|       | Signals                                          | 4–23 |

| 4.6.6 | VAFC Cycle Timing                                | 4–26 |

|       |                                                  |      |

# 5 Mechanical Specifications

# 6 Thermal Specifications

# 7 Address Space

| 7 4     |                                                |      |

|---------|------------------------------------------------|------|

| 7.1     | Overview                                       | 7–1  |

| 7.2     | Configuration Space                            | 7–2  |

| 7.3     | ROM Space                                      | 7–2  |

| 7.4     | VGA Memory Space                               | 7–2  |

| 7.5     | 2DA Memory Space                               | 7–2  |

| 7.5.1   | 2DA Base Address 0 Memory Space                | 7–2  |

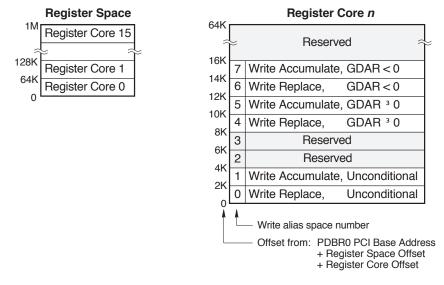

| 7.5.1.1 | Base Address 0 Core Space Organization         | 7–3  |

| 7.5.1.2 | Base Address 0 Register Space Organization     | 7–5  |

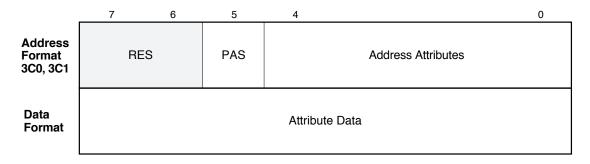

| 7.5.1.3 | Base Address 0 Alternate Control Space Writes  | 7–9  |

| 7.5.2   | Base Address 1 Memory Space                    | 7–10 |

| 7.5.2.1 | Base Address 1 VGA Alternate Register Space    | 7–10 |

| 7.5.2.2 | Base Address 1 Generic Peripheral Port Space   | 7–11 |

| 7.5.2.3 | Base Address 1 Interrupt Status Register Space | 7–12 |

| 7.5.2.4 | Base Address 1 Palette and DAC Register Space  | 7–12 |

| 7.5.2.5 | Base Address 1 ROM Sparse Space Access         | 7–13 |

# 8 Register Descriptions

| 8.1     | Overview                                   | 8–1  |

|---------|--------------------------------------------|------|

| 8.2     | PCI Configuration Registers                | 8–10 |

| 8.2.1   | PCI Identification Register                | 8–11 |

| 8.2.2   | PCI Command and Status Register            | 8–12 |

| 8.2.3   | PCI Class and Revision Register            | 8–16 |

| 8.2.4   | PCI Latency Timer and Header Type Register | 8–17 |

| 8.2.5   | PCI Device Base Address Registers          | 8–18 |

| 8.2.5.1 | PDBR0 Functions                            | 8–19 |

| 8.2.5.2 | PDBR1 Functions                            | 8–19 |

| 8.2.6   | PCI Expansion ROM Base Address Register    | 8–21 |

| 8.2.7   | PCI Interrupt Line Register                | 8–22 |

| 8.2.8   | PCI Clock Control Register                 | 8–23 |

| 8.3     | Miscellaneous Registers                    | 8–25 |

| 8.3.1   | Command Status Register                    | 8–25 |

| 8.3.1.1 | Write Memory Barrier                       | 8–26 |

| 8.3.2   | Interrupt Status Register                  | 8–27 |

| 8.4     | Graphics Command Registers                 | 8–29 |

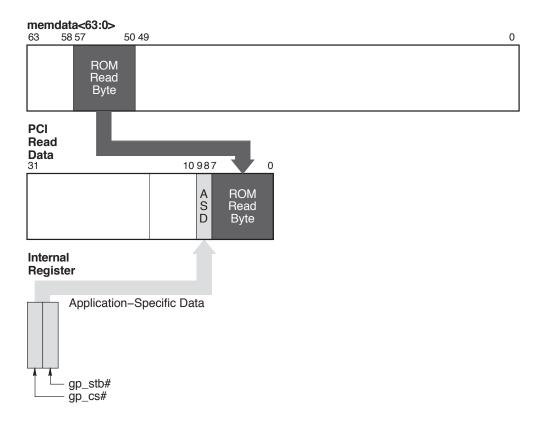

| 8.4.1   | Slope Registers                            | 8–30 |

| 8.4.2   | Span Width Register                        | 8–33 |

| 8.4.2.1 | GSWR Read                                  | 8–33 |

| 8.4.2.2 | GSWR Write                                 | 8–34 |

| 8.4.3    | Continue Register                           | 8–35 |

|----------|---------------------------------------------|------|

| 8.4.3.1  | GCTR Write                                  | 8–35 |

| 8.4.3.2  | GCTR Read                                   | 8–37 |

| 8.4.4    | Copy-64 Source and Destination Registers    | 8–38 |

| 8.4.5    | Copy-64A Source and Destination Registers   | 8–40 |

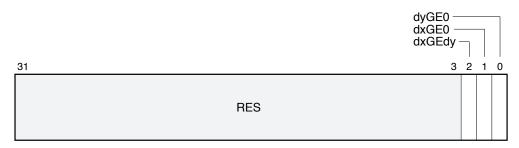

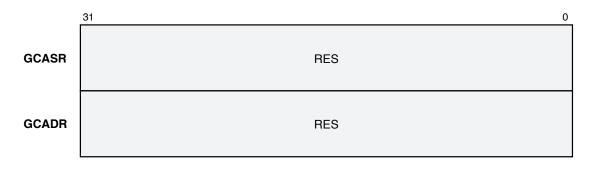

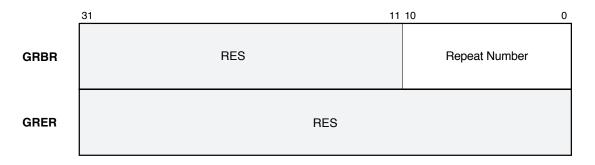

| 8.4.6    | Repeat Begin and End Registers              | 8–41 |

| 8.5 Gra  | aphics Control Registers                    | 8–42 |

| 8.5.1    | Mode Register                               | 8–43 |

| 8.5.2    | Deep Register                               | 8–46 |

| 8.5.2.1  | Gib-Endian Support                          | 8–47 |

| 8.5.3    | Slope-No-Go Registers                       | 8–50 |

| 8.5.3.1  | GSNR<7:0> Write                             | 8–50 |

| 8.5.3.2  | GSNR<7:0> Read                              | 8–51 |

| 8.5.4    | Copy Buffer Registers                       | 8–53 |

| 8.5.5    | Pixel Shift Register                        | 8–55 |

| 8.5.6    | Address Register                            | 8–56 |

| 8.5.7    | Data Register                               | 8–58 |

| 8.5.7.1  | GDAR Opaque-Fill and Transparent-Fill Modes | 8–58 |

| 8.5.7.2  | GDAR Line Mode                              | 8–59 |

| 8.5.8    | Foreground and Background Registers         | 8–60 |

| 8.5.9    | Raster Operation Register                   | 8–63 |

| 8.5.10   | Pixel Mask Register                         | 8–66 |

| 8.5.10.1 | GPXR Stipple Modes                          | 8–66 |

| 8.5.10.2 | GPXR Simple Mode                            | 8–67 |

| 8.5.10.3 | GPXR Any Mode                               | 8–67 |

| 8.5.11   | Bresenham 1 Register                        | 8–68 |

| 8.5.11.1 | GB1R Line Mode                              | 8–68 |

| 8.5.11.2 | GB1R Scaled-Copy Mode                       | 8–69 |

| 8.5.12   | Bresenham 2 Register                        | 8–70 |

| 8.5.13   | Bresenham 3 Register                        | 8–71 |

| 8.5.13.1 | GB3R Line Mode                              | 8–71 |

| 8.5.13.2 | GB3R Scaled-Copy Mode                       | 8–72 |

| 8.5.14   | Bresenham Width Register                    | 8–73 |

| 8.5.15   | DMA Base Address Register                   | 8–74 |

| 8.5.15.1 | GDBR DMA-Read Copy Mode                     | 8–74 |

| 8.5.15.2 | GDBR Scaled-Copy Mode                       | 8–75 |

| 8.5.16   | Scaled-Copy Control Register                | 8–76 |

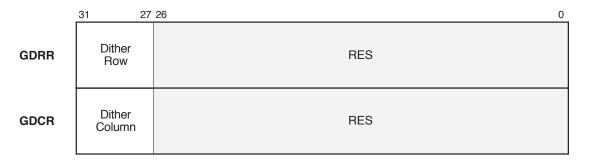

| 8.5.17   | Dither Row and Column Registers             | 8–81 |

| 8.6 Ha   | rdware Cursor Registers                     | 8–82 |

| 8.6.1    | Cursor Mode Register                        | 8–82 |

| 8.6.2    | Cursor Base Address Register                | 8–84 |

| 8.6.3    | Cursor XY Register                          | 8–85 |

| 8.7 Vid  | eo Control Registers                        | 8–85 |

| 8.7.1   | Video Base Address, Line Increment, and Line Width    |       |

|---------|-------------------------------------------------------|-------|

|         | Registers                                             | 8–86  |

| 8.7.2   | Video Valid Register                                  | 8–88  |

| 8.8     | Video Format Registers                                | 8–90  |

| 8.8.1   | Video Pixel Format Register                           | 8–91  |

| 8.8.1.1 | Pixel Formatting                                      | 8–95  |

| 8.8.1.2 | Addressing the RAM LUT in 15-bpp and 16-bpp           |       |

|         | True-Color Modes                                      | 8–96  |

| 8.8.1.3 | Pixel Occlusion Bitmap                                | 8–98  |

| 8.8.2   | Video Pixel Occlusion Bitmap Base Address Register    | 8–100 |

| 8.8.3   | Video Pixel Occlusion Bitmap Current Address Register | 8–101 |

| 8.8.4   | Video Current Refresh Address Register                | 8–102 |

| 8.8.5   | Alternate Video Control Register                      | 8–103 |

| 8.9     | Palette and DAC Registers                             | 8–104 |

| 8.9.1   | Palette and DAC RAM Write and Read Address Registers  | 8–105 |

| 8.9.2   | Palette and DAC RAM Color Register                    | 8–106 |

| 8.9.3   | Palette and DAC Cursor Write and Read Address         |       |

|         | Registers                                             | 8–107 |

| 8.9.4   | Palette and DAC Cursor Color Register                 | 8–108 |

| 8.9.5   | Palette and DAC Pixel Mask Register                   | 8–109 |

| 8.9.6   | Palette and DAC Status Register                       | 8–110 |

| 8.9.7   | Palette and DAC Command Register 0                    | 8–111 |

| 8.9.8   | Palette and DAC Command Register 1                    | 8–112 |

| 8.9.9   | Palette and DAC Signature Analysis Registers          | 8–114 |

| 8.10    | VGA Register Overview                                 | 8–115 |

| 8.11    | VGA External and General Registers                    | 8–116 |

| 8.11.1  | VGA Miscellaneous Output Register                     | 8–117 |

| 8.11.2  | VGA Feature Control Register                          | 8–119 |

| 8.11.3  | VGA Input Status 0 Register                           | 8–120 |

| 8.11.4  | VGA Input Status 1 Register                           | 8–121 |

| 8.12    | VGA Sequencer Registers                               | 8–122 |

| 8.12.1  | VGA Sequencer Index Register                          | 8–122 |

| 8.12.2  | VGA Sequencer Data Register                           | 8–123 |

| 8.12.3  | VGA Sequencer Reset Register                          | 8–124 |

| 8.12.4  | VGA Sequencer Clocking Mode Register                  | 8–125 |

| 8.12.5  | VGA Sequencer Plane Mask Register                     | 8–127 |

| 8.12.6  | VGA Sequencer Character Map Select Register           | 8–128 |

| 8.12.7  | VGA Sequencer Memory Mode Register                    | 8–129 |

| 8.13    | VGA CRT Controller Registers                          | 8–130 |

| 8.13.1  | VGA CRTC Index Register                               | 8–132 |

| 8.13.2  | VGA CRTC Data Register                                | 8–134 |

| 8.13.3  | VGA CRTC Horizontal Total Register                    | 8–135 |

| 8.13.4  | VGA CRTC Horizontal Display End Register              | 8–136 |

| 8.13.5  | VGA CRTC Start and End Horizontal Blank Registers    | 8–137 |

|---------|------------------------------------------------------|-------|

| 8.13.6  | VGA CRTC Start and End Horizontal Sync Registers     | 8–139 |

| 8.13.7  | VGA CRTC Vertical Total Register                     | 8–141 |

| 8.13.8  | VGA CRTC Overflow Register                           | 8–142 |

| 8.13.9  | VGA CRTC Preset Row Register                         | 8–143 |

| 8.13.10 | VGA CRTC Maximum Scanline Register                   | 8–144 |

| 8.13.11 | VGA CRTC Cursor Start and End Registers              | 8–145 |

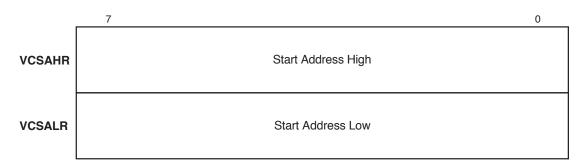

| 8.13.12 | 0 0                                                  | 8–147 |

| 8.13.13 |                                                      | 8–148 |

| 8.13.14 |                                                      | 8–149 |

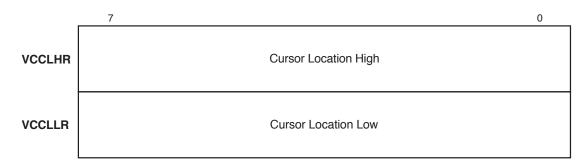

| 8.13.15 | 1 5 0                                                | 8–151 |

| 8.13.16 | 0                                                    | 8–152 |

| 8.13.17 | 8                                                    | 8–153 |

| 8.13.18 | 0 0                                                  | 8–154 |

| 8.13.19 | 0                                                    | 8–155 |

| 8.13.20 | 1 0                                                  | 8–157 |

| 8.14    | VGA Extended Registers                               | 8–157 |

| 8.14.1  | VGA Extended Paging Control Register                 | 8–158 |

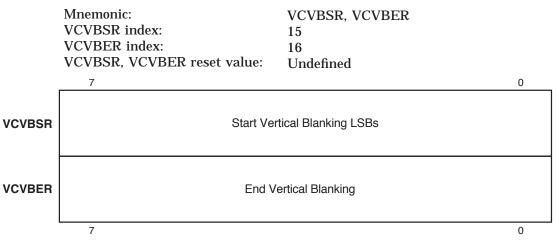

| 8.14.2  | VGA Extended Host Page Offset A and B Registers      | 8–160 |

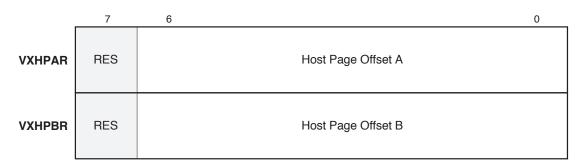

| 8.14.3  | VGA Extended Split-Screen Start Address High and Low |       |

|         | Byte Register                                        | 8–161 |

| 8.14.4  | VGA Extended Interlace Control Register              | 8–162 |

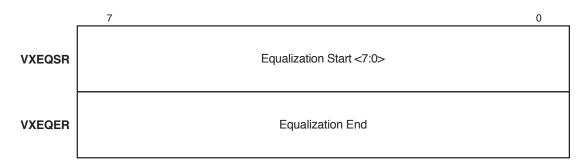

| 8.14.5  | VGA Extended Equalization Start and End Registers    | 8–163 |

| 8.14.6  | VGA Extended Half-Line Register                      | 8–164 |

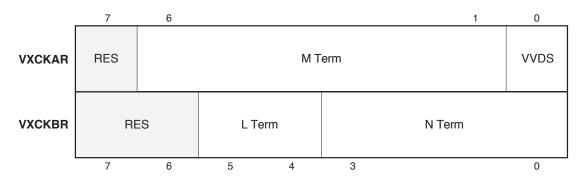

| 8.14.7  | VGA Extended Timing Control A Register               | 8–165 |

| 8.14.8  | VGA Extended Timing Control B Register               | 8–166 |

| 8.14.9  | VGA Extended Video FIFO Control Register             | 8–167 |

| 8.14.10 |                                                      | 8–168 |

| 8.14.11 | VGA Extended Interface Control Register              | 8–171 |

| 8.15    | VGA Graphics Controller Registers                    | 8–171 |

| 8.15.1  | VGA Graphics Controller Index Register               | 8–172 |

| 8.15.2  | VGA Graphics Controller Data Register                | 8–173 |

| 8.15.3  | VGA Graphics Controller Set/Reset Register           | 8–174 |

| 8.15.4  | VGA Graphics Controller Enable Set/Reset Register    | 8–175 |

| 8.15.5  | VGA Graphics Controller Color Compare Register       | 8–176 |

| 8.15.6  | VGA Graphics Controller Data Rotate Register         | 8–177 |

| 8.15.7  | VGA Graphics Controller Read Map Select Register     | 8–178 |

| 8.15.8  | VGA Graphics Controller Mode Register                | 8–179 |

| 8.15.9  | VGA Graphics Controller Miscellaneous Register       | 8–181 |

| 8.15.10 | 1 0                                                  | 8–182 |

| 8.15.11 | VGA Graphics Controller Bit Mask Register            | 8–183 |

| 8.16    | VGA Attribute Controller Registers                   | 8–183 |

| 8.16.1  | VGA Attribute Controller Index/Data Register         | 8–184 |

| 8.16.2 | VGA Attribute Controller Palette Registers           | 8–186 |

|--------|------------------------------------------------------|-------|

| 8.16.3 | VGA Attribute Controller Mode Register               | 8–187 |

| 8.16.4 | VGA Attribute Controller Overscan Register           | 8–188 |

| 8.16.5 | VGA Attribute Controller Color Plane Enable Register | 8–189 |

| 8.16.6 | VGA Attribute Controller Pixel Panning Register      | 8–190 |

| 8.16.7 | VGA Attribute Controller Color Select Register       | 8–191 |

| 8.17   | VGA Color Registers                                  | 8–191 |

| 8.17.1 | VGA Color Pixel Address Write Mode and Read Mode     |       |

|        | Registers                                            | 8–192 |

| 8.17.2 | VGA Color DAC State Register                         | 8–193 |

| 8.17.3 | VGA Color Pixel Data Register                        | 8–194 |

| 8.17.4 | VGA Color Pixel Mask Register                        | 8–195 |

# 9 PCI Operations

| 9.1     | Configuration Operations            | 9–1  |

|---------|-------------------------------------|------|

| 9.2     | Memory Reads and Writes             | 9–2  |

| 9.2.1   | Memory Write to Core Space          | 9–2  |

| 9.2.2   | Memory Read of Core Space           | 9–3  |

| 9.2.2.1 | Read Interlock                      | 9–3  |

| 9.3     | Target Operations                   | 9–4  |

| 9.3.1   | Access Granularity                  | 9–5  |

| 9.3.2   | Transaction Termination             | 9–5  |

| 9.4     | Master Operation                    | 9–9  |

| 9.4.1   | DMA Read Transfer                   | 9–10 |

| 9.4.2   | Transaction Termination             | 9–10 |

| 9.4.3   | Aborted DMA Transaction Termination | 9–11 |

| 9.5     | Parity                              | 9–11 |

| 9.6     | Bus Parking                         | 9–11 |

| 9.7     | Functions Not Supported             | 9–12 |

|         |                                     |      |

# 10 Graphics Operations

| 10.1    | Overview                         | 10–1  |

|---------|----------------------------------|-------|

| 10.1.1  | Frame Buffer Writes              | 10–1  |

| 10.1.2  | Graphics Command Register Writes | 10–2  |

| 10.1.3  | Invoking Graphics Operations     | 10–3  |

| 10.1.4  | Register Load Synchronization    | 10–4  |

| 10.1.5  | Source and Destination Operands  | 10–5  |

| 10.2    | Graphics Modes                   | 10–6  |

| 10.2.1  | Simple Mode                      | 10–7  |

| 10.2.2  | Opaque-Stipple Mode              | 10–9  |

| 10.2.2. |                                  | 10–11 |

| 10.2.3    | Transparent-Stipple Mode                        | 10–12 |

|-----------|-------------------------------------------------|-------|

| 10.2.3.1  | Transparent-Stipple with Pixel Mask Modes       | 10–13 |

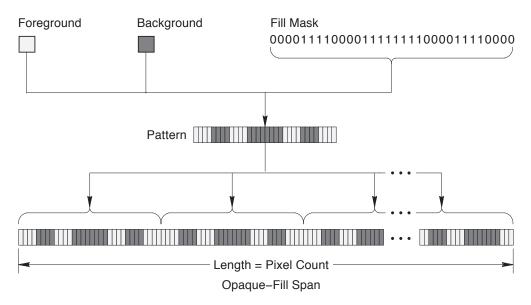

| 10.2.4    | Opaque-Fill Mode                                | 10–14 |

| 10.2.4.1  | Opaque Extended-Pattern Fill Mode               | 10–16 |

| 10.2.5    | Transparent-Fill Mode                           | 10–17 |

| 10.2.5.1  | Transparent Extended-Pattern Fill Mode          | 10–18 |

| 10.2.6    | Copy Mode                                       | 10–19 |

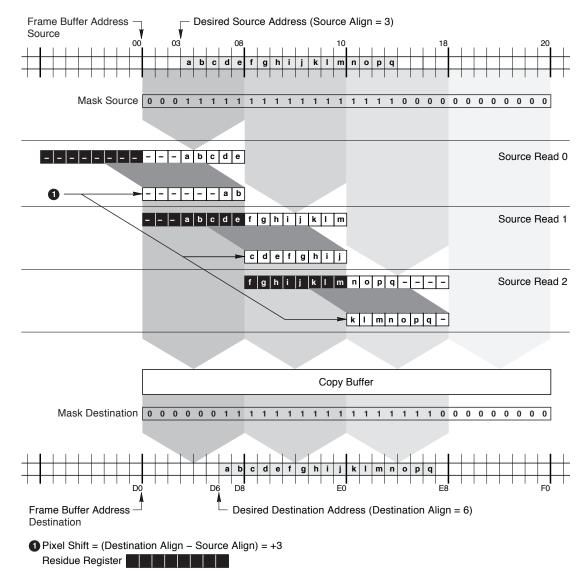

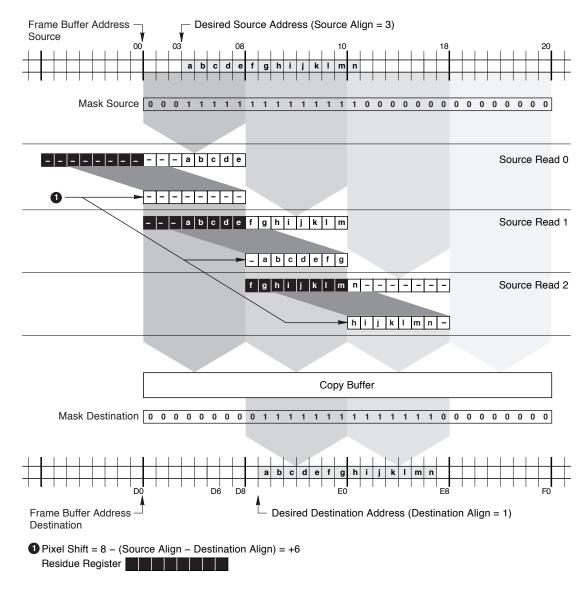

| 10.2.6.1  | Source and Destination Alignment                | 10–22 |

| 10.2.6.2  | Backward Copies                                 | 10–25 |

| 10.2.6.3  | Priming and Flushing the Residue Register       | 10–26 |

| 10.2.6.4  | Copy Direction Flag                             | 10–28 |

| 10.2.6.5  | 64-Byte Unmasked Span Copies                    | 10–29 |

| 10.2.6.6  | Copy Buffer Operation                           | 10–29 |

| 10.2.6.7  | Fast Frame Buffer Access Using the Copy Buffer  |       |

|           | Registers                                       | 10–32 |

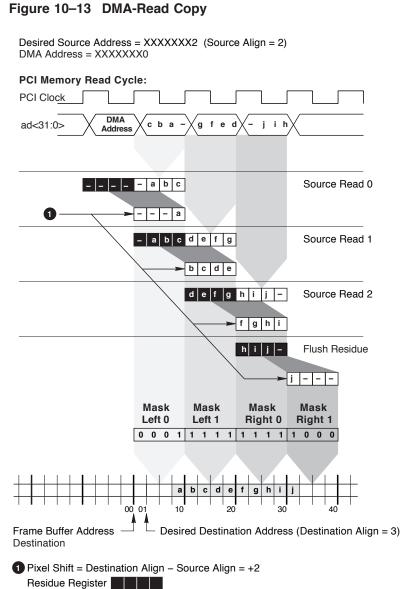

| 10.2.7    | DMA-Read Copy Mode                              | 10–33 |

| 10.2.7.1  | Priming and Flushing the Residue Register       | 10–36 |

| 10.2.8    | Scaled-Copy Mode                                | 10–39 |

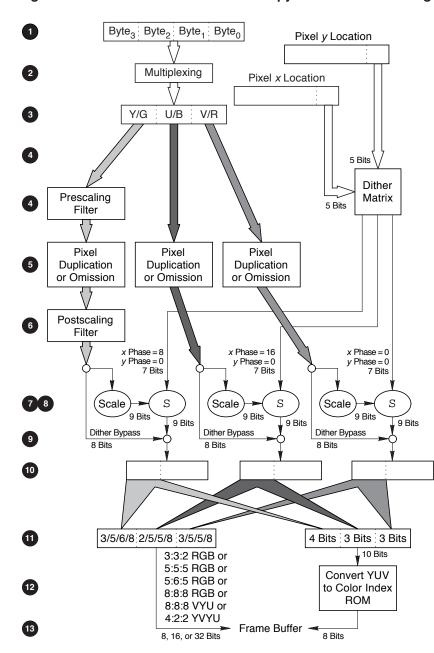

| 10.2.8.1  | Video Rendering Pixel Flow                      | 10–42 |

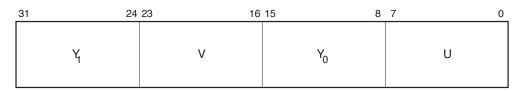

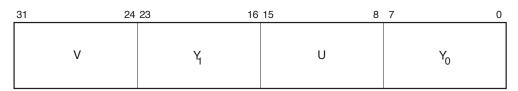

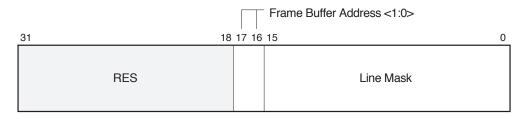

| 10.2.8.2  | YUV Pixel Formats                               | 10–44 |

| 10.2.8.3  | 16-bpp and 32-bpp RGB Formats                   | 10–46 |

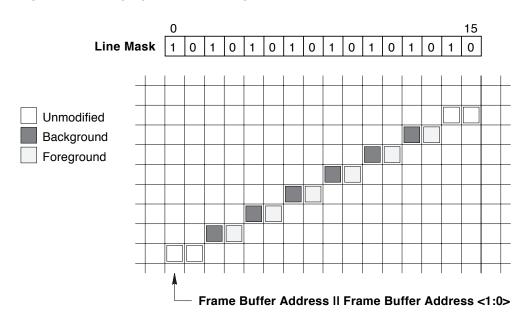

| 10.2.8.4  | Rendering Full Frames                           | 10–46 |

| 10.2.8.5  | Unoccluded or Trivially Occluded Target Windows | 10–46 |

| 10.2.8.6  | Nontrivially Occluded Windows                   | 10–48 |

| 10.2.8.7  | Determining the Command FIFO Entry Availability | 10–48 |

| 10.2.8.8  | Scaling                                         | 10–48 |

| 10.2.8.9  | Programming the Bresenham Scaler for Unoccluded |       |

|           | Spans                                           | 10–49 |

| 10.2.8.10 | Scaling of Occluded Spans                       | 10–50 |

| 10.2.8.11 | Specifying Span Starting and Trailing Edges     | 10–51 |

| 10.2.8.12 | Required Software Interlock                     | 10–51 |

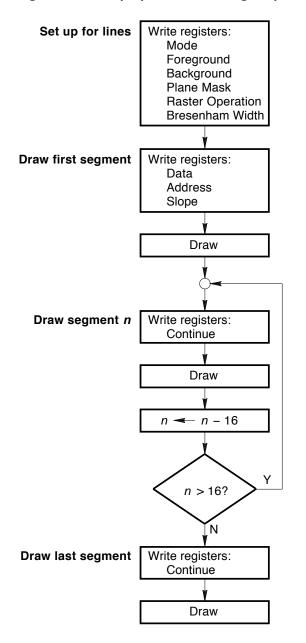

| 10.2.9    | Opaque-Line Mode                                | 10–52 |

| 10.2.9.1  | Drawing Lines with Frame Buffer Writes          | 10–52 |

| 10.2.9.2  | Drawing Lines with the Slope Registers          | 10–54 |

| 10.2.9.3  | Extending and Linking 2D Lines                  | 10–57 |

| 10.2.10   | Transparent-Line Mode                           | 10–62 |

# 11 Programming

| 11.1 PCI Configuration Firmware                                 | 11–1  |

|-----------------------------------------------------------------|-------|

| 11.1.1 Device Address Mapping                                   | 11–1  |

| 11.1.2 Bus Mastering                                            | 11–2  |

| 11.1.3 Interrupt Routing                                        | 11–3  |

| 11.1.4 Expansion ROM                                            | 11–3  |

| 11.2 Mode Switching                                             | 11–3  |

| 11.2.1 VGA-to-2DA Mode Switching                                | 11–3  |

| 11.2.2 2DA-to-VGA Mode Switching                                | 11–4  |

| 11.2.2.1 Expected 2DA Operation During VGA Mode                 | 11–5  |

| 11.3 Bit-Block Transfers                                        | 11–5  |

| 11.3.1 Screen-to-Screen Copy                                    | 11–5  |

| 11.3.2 Host-to-Screen Copy                                      | 11–8  |

| 11.3.3 Scaled-Copy                                              | 11–8  |

| 11.4 Dither Mathematics                                         | 11–8  |

| 11.5 Scaling Filters                                            | 11–9  |

| 11.6 Overlays                                                   | 11–10 |

| 11.6.1 Flicker-Free Monochrome Overlay Support                  | 11–10 |

| 11.6.2 True Monochrome Overlay with Pixel Occlusion Bitmap      |       |

| Hardware                                                        | 11–11 |

| 11.6.3 True 8-bpp Overlay in 16-bpp or 32-bpp Frame Buffers     | 11–12 |

| 11.7 Fills                                                      | 11–13 |

| 11.7.1 Solid                                                    | 11–13 |

| 11.7.2 Stippling or Filling with a Monochrome Brush             | 11–14 |

| 11.7.3 Tiling or Filling with a Non-Monochrome Brush            | 11–14 |

| 11.8 Lines                                                      | 11–15 |

| 11.8.1 Line Drawing Under X                                     | 11–15 |

| 11.8.2 Line Drawing Under Win32                                 | 11–17 |

| 11.9 Text                                                       | 11–19 |

| 11.10 Repeat Loop Examples                                      | 11–19 |

| 11.11 Video Registers                                           | 11–22 |

| 11.11.1 Modifying the Contents of the Video Registers           | 11–22 |

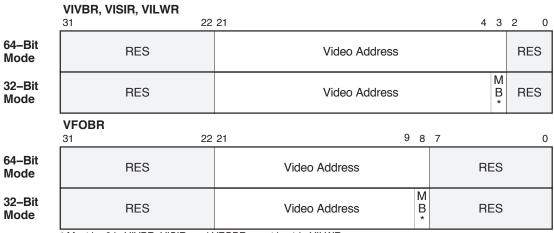

| 11.11.2 Video Registers in 64-Bit and 32-Bit Frame Buffer Modes | 11–23 |

| 11.11.3 Video Refresh Calculations                              | 11–25 |

| 11.12 Programming for Alpha CPUs                                | 11–26 |

| 11.12.1 Programmed I/O Through the CPU Write Buffer             | 11–27 |

| 11.12.2 Address and Continue Register Access                    | 11–28 |

### 12 Hardware Interface

| 12.1 Frame Buffer Interface                           | 12–1  |

|-------------------------------------------------------|-------|

| 12.1.1 Hardware Mode Restrictions                     | 12–1  |

| 12.1.2 Frame Buffer Configuration Sensing             | 12–5  |

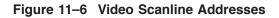

| 12.2 VGA Subsystem                                    | 12–6  |

| 12.2.1 PCI-to-VGA Interface                           | 12–6  |

| 12.2.2 VGA-to-Frame Buffer Memory Interface           | 12–6  |

| 12.2.3 VGA-to-Video Back End Interface                | 12–6  |

| 12.3 ROM and Generic Peripheral Port Interface        | 12–8  |

| 12.3.1 GPP Read and Write Access                      | 12–8  |

| 12.3.2 GPP Interrupts                                 | 12–9  |

| 12.4 Video Port and Display Monitor Interface         | 12–9  |

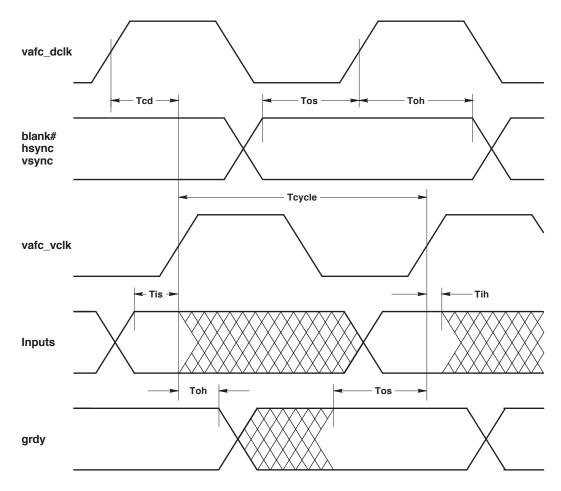

| 12.4.1 VESA Advanced Feature Connector                | 12–9  |

| 12.4.1.1 VAFC Operation                               | 12–10 |

| 12.4.1.2 Relationship Between vafc_vclk and vafc_dclk | 12–10 |

| 12.4.1.3 VAFC Pixel Output Modes                      | 12–10 |

| 12.4.1.4 VAFC Pixel Input Modes                       | 12–11 |

| 12.4.1.5 VAFC Input Windows                           | 12–12 |

| 12.4.1.6 VAFC Blank Enable                            | 12–12 |

| 12.4.1.7 VAFC Output Screen Resolutions               | 12–12 |

| 12.4.1.8 VAFC Input Screen Resolutions                | 12–13 |

| 12.4.2 Video Port Transceivers                        | 12–13 |

| 12.4.3 Monitor Connection                             | 12–13 |

| 12.4.4 Display Power Management Signaling             | 12–14 |

| 12.4.5 Display Data Channel                           | 12–14 |

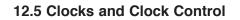

| 12.5 Clocks and Clock Control                         | 12–15 |

| 12.5.1 Memory Clock                                   | 12–15 |

| 12.5.2 Core Clock                                     | 12–15 |

| 12.5.3 Pixel Clock                                    | 12–15 |

| 12.5.4 VGA Dot Clock                                  | 12–16 |

| 12.5.5 Test Clock                                     | 12–16 |

# A Pin Summary

# **B** Register Summary

# C Technical Support, Ordering Information, and Associated Literature

### Index

# Figures

| 1–1  | Supported VESA Display Modes                        | 1–4  |

|------|-----------------------------------------------------|------|

| 1–2  | DECchip 21130 in Minimum System Configuration       | 1–5  |

| 1–3  | Explanation of 21130 Chip Face Labels               | 1–8  |

| 2–1  | DECchip 21130 Block Diagram                         | 2–2  |

| 4–1  | Clock Domains                                       | 4–3  |

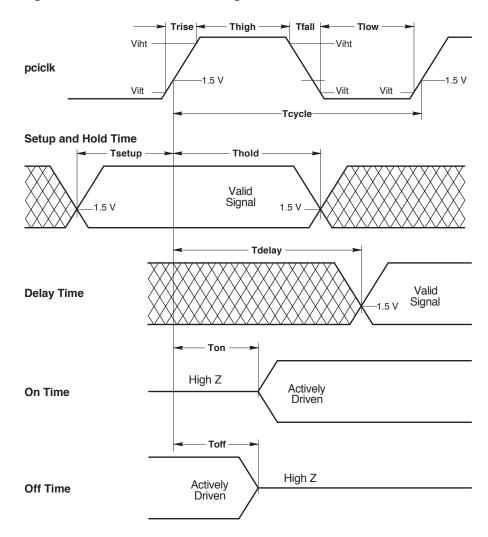

| 4–2  | PCI Clock Domain Signal ac Parameter Measurements   | 4–7  |

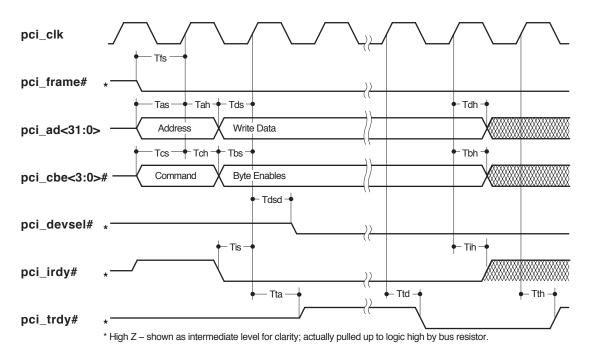

| 4–3  | PCI Write — Cycle Start Timing                      | 4–10 |

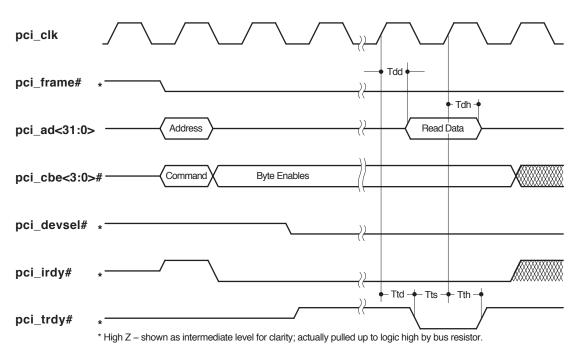

| 4–4  | PCI Read — Cycle Start Timing $\ldots$              | 4–12 |

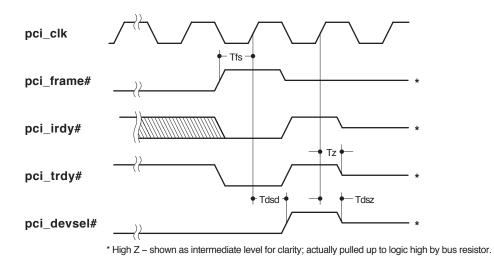

| 4–5  | PCI Read or Write — Cycle End Timing                | 4–13 |

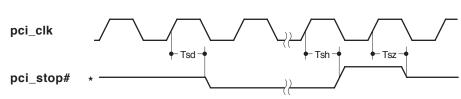

| 4–6  | PCI Target Disconnect or Abort — pci_stop# Timing   | 4–14 |

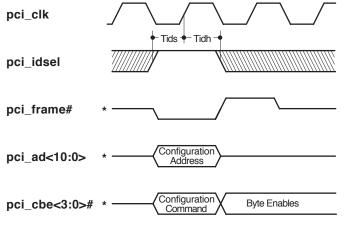

| 4–7  | PCI Configuration Cycle — pci_idsel Timing          | 4–15 |

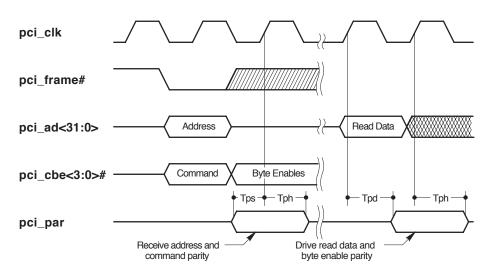

| 4–8  | PCI Parity — pci_par Timing                         | 4–16 |

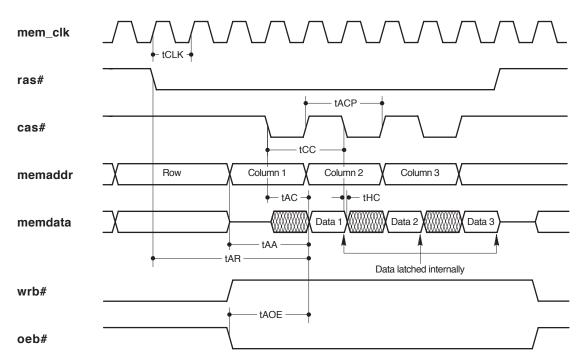

| 4–9  | Hyperpage Mode Memory Write Cycle Timing            | 4–17 |

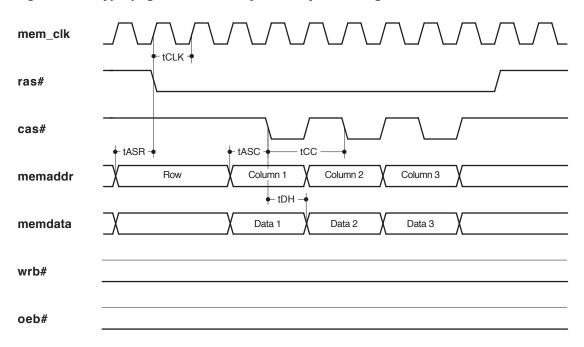

| 4–10 | Hyperpage Mode Memory Read Cycle Timing             | 4–18 |

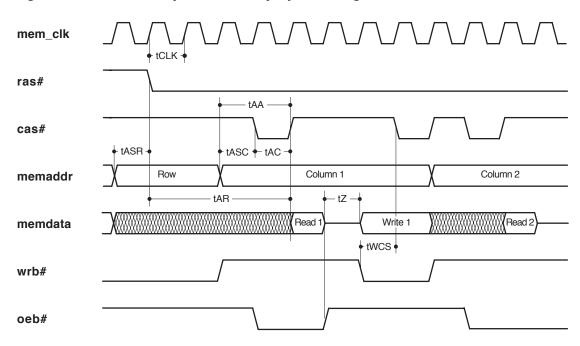

| 4–11 | Read-Modify-Write Memory Cycle Timing               | 4–19 |

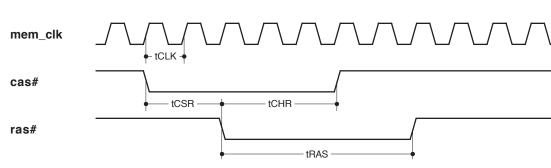

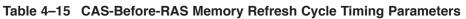

| 4–12 | CAS-Before-RAS Memory Refresh Cycle Timing          | 4–20 |

| 4–13 | ROM Data Cycle Timing                               | 4–21 |

| 4–14 | GPP Data Cycle Timing                               | 4–22 |

| 4–15 | Pixel Clock Domain Signal ac Parameter Measurements | 4–23 |

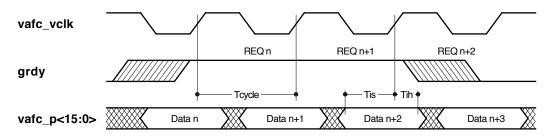

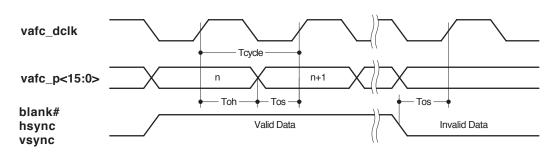

| 4–16 | VAFC Clock Domain Signal ac Parameter Measurements  | 4–24 |

| 4–17 | VAFC Request Cycle Timing                           | 4–26 |

| 4–18 | VAFC Video Data Transfer Cycle Timing               | 4–27 |

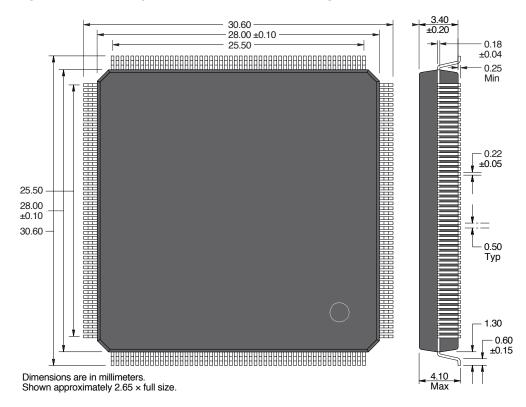

| 5–1  | DECchip 21130 208-Pin PQFP Package                  | 5—1  |

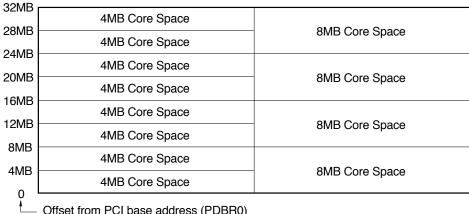

| 7–1  | Memory Space Organization                           | 7–4  |

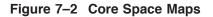

| 7–2  | Core Space Maps                                     | 7–4  |

| 7–3  | Base Address Register 0 Register Space Organization | 7–5  |

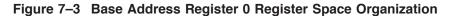

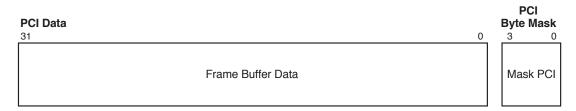

| 7–4  | ROM Sparse Space PCI Read Data Format               | 7–15 |

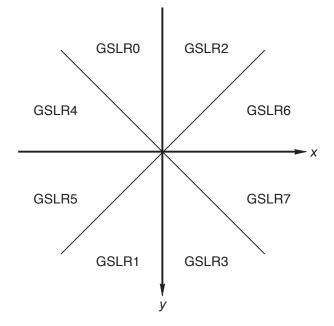

| 8–1  | Slope Registers and Drawing Octants                 | 8–32 |

|      |                                                     |      |

| 8–2   | Gib-Endian Transfers                                  | 8–48  |  |  |  |  |

|-------|-------------------------------------------------------|-------|--|--|--|--|

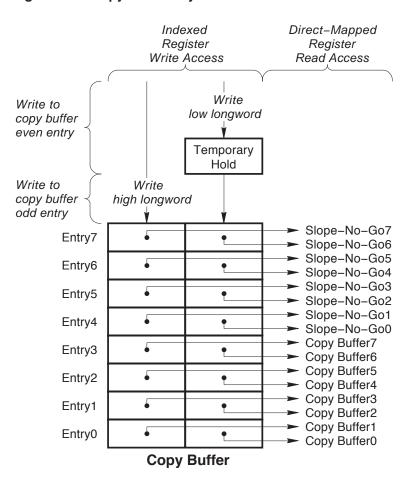

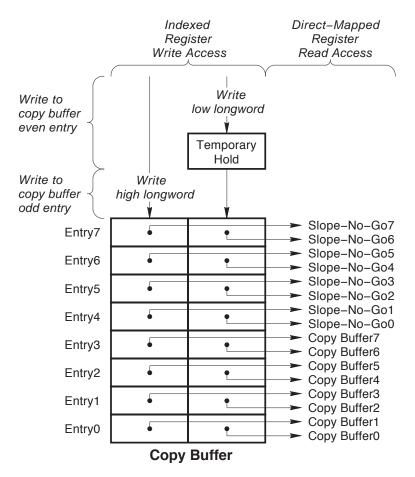

| 8–3   | Copy Buffer Layout                                    |       |  |  |  |  |

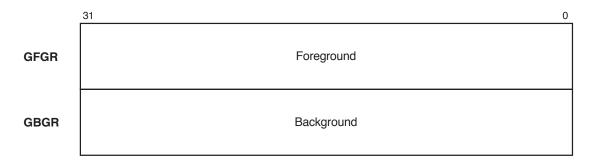

| 8–4   | Foreground and Background as a Function of Bitmap     |       |  |  |  |  |

|       | Depth                                                 | 8–62  |  |  |  |  |

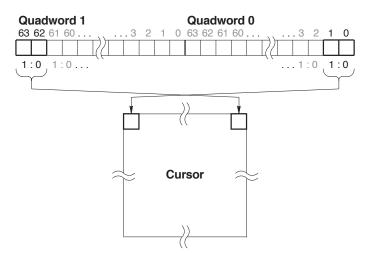

| 8–5   | Cursor Value Bits to Pixels Mapping                   | 8–83  |  |  |  |  |

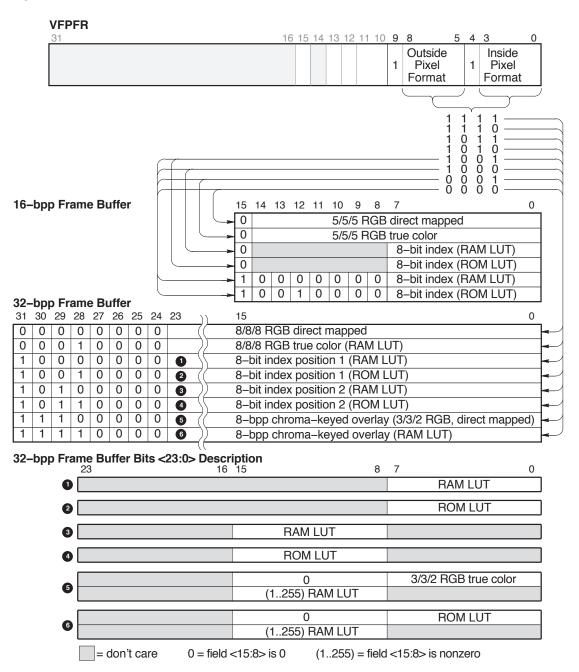

| 8–6   | Variable Pixel Formats                                | 8–94  |  |  |  |  |

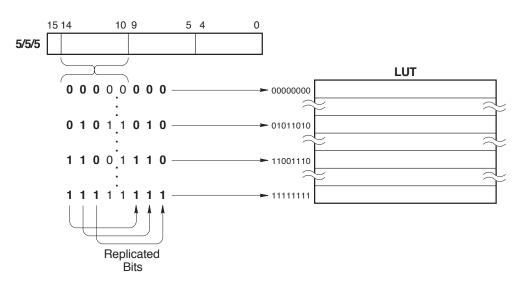

| 8–7   | RAM LUT Addressing in 15-bpp and 16-bpp True-Color    |       |  |  |  |  |

|       | Modes                                                 | 8–97  |  |  |  |  |

| 8–8   | Pixel Occlusion Bitmap Format                         | 8–98  |  |  |  |  |

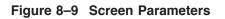

| 8–9   | Screen Parameters                                     | 8–131 |  |  |  |  |

| 10–1  | Simple Mode PCI Write-Data Format                     | 10–7  |  |  |  |  |

| 10–2  | Opaque-Stipple Mode PCI Write-Data Format             | 10–9  |  |  |  |  |

| 10–3  | Opaque-Stipple Mode Operation                         | 10–10 |  |  |  |  |

| 10–4  | Transparent-Stipple Mode PCI Write-Data Format        | 10–12 |  |  |  |  |

| 10–5  | Transparent-Stipple Mode Operation                    | 10–13 |  |  |  |  |

| 10–6  | Opaque-Fill Mode PCI Write-Data Format                | 10–14 |  |  |  |  |

| 10–7  | Opaque-Fill Mode Operation                            | 10–15 |  |  |  |  |

| 10–8  | Copy Mode PCI Write Data Formats                      | 10–20 |  |  |  |  |

| 10–9  | Forward Span Copy                                     | 10–24 |  |  |  |  |

| 10–10 | Primed Forward Span Copy                              | 10–27 |  |  |  |  |

| 10–11 | Copy Buffer Layout                                    | 10–31 |  |  |  |  |

| 10–12 | DMA-Read Copy-Mode PCI Write-Data Format              | 10–34 |  |  |  |  |

| 10–13 | DMA-Read Copy                                         | 10–38 |  |  |  |  |

| 10–14 | Scaled-Copy Mode PCI Write Data Format                | 10–40 |  |  |  |  |

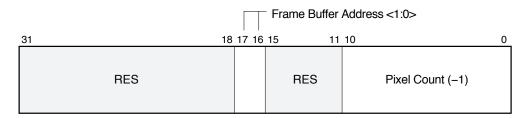

| 10–15 | Scaled-Copy PCI DMA Start Address                     | 10–41 |  |  |  |  |

| 10–16 | Host-to-Screen Scaled-Copy and Video Rendering Pixel  |       |  |  |  |  |

|       | Flow                                                  | 10–43 |  |  |  |  |

| 10–17 | MCSR Format                                           | 10–48 |  |  |  |  |

| 10–18 | Opaque-Line Mode PCI Write-Data Format                | 10–53 |  |  |  |  |

| 10–19 | Opaque Line Drawing                                   | 10–58 |  |  |  |  |

| 10–20 | Opaque-Line Drawing Sequence                          | 10–61 |  |  |  |  |

| 11–1  | BitBlt Using Copy Mode Example                        | 11–7  |  |  |  |  |

| 11–2  | Overlay Data in 16-bpp and 32-bpp Frame Buffers       | 11–13 |  |  |  |  |

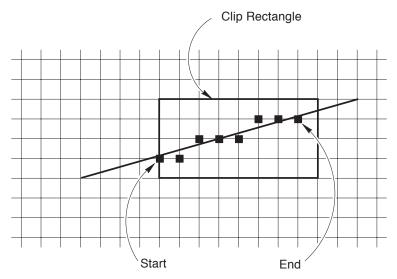

| 11–3  | Drawing Clipped Lines                                 | 11–16 |  |  |  |  |

| 11–4  | Frame Buffer Address Space in 64-Bit and 32-Bit Modes | 11–24 |  |  |  |  |

| 11–5  | Video Address in 64-Bit and 32-Bit Modes              | 11–25 |  |  |  |  |

| 11–6  | Video Scanline Addresses                              | 11–26 |  |  |  |  |

| 12–1 | VGA Subsystem Interfaces | 12–7  |

|------|--------------------------|-------|

| 12–2 | Clock Generation         | 12–17 |

# Tables

| 1–1  | 21130 Chip Revision Levels                                            | 1–7  |

|------|-----------------------------------------------------------------------|------|

| 2–1  | Mode Restrictions                                                     | 2–11 |

| 3–1  | Signal List                                                           | 3–1  |

| 3–2  | Signal Description                                                    | 3–4  |

| 3–3  | Signals by Function                                                   | 3–11 |

| 3–4  | Signals and Active Levels by Direction                                | 3–15 |

| 4–1  | Absolute Maximum Ratings                                              | 4–2  |

| 4–2  | Normal Operating Conditions                                           | 4–2  |

| 4–3  | Pin Characteristics                                                   | 4–4  |

| 4–4  | dc Parameters                                                         | 4–6  |

| 4–5  | PCI Clock Domain Signal ac Parameters                                 | 4–8  |

| 4–6  | PCI Write — Cycle Start Timing Parameters                             | 4–10 |

| 4–7  | PCI Read — Cycle Start Timing Parameters                              | 4–12 |

| 4–8  | PCI Read or Write — Cycle End Timing Parameters                       | 4–13 |

| 4–9  | PCI Target Disconnect or Abort — pci_stop# Timing                     |      |

|      | Parameters                                                            | 4–14 |

| 4–10 | PCI Configuration Cycle — pci_idsel Timing Parameters $\dots$         | 4–15 |

| 4–11 | PCI Parity — pci_par Timing Parameters                                | 4–16 |

| 4–12 | Hyperpage Mode Memory Write Cycle Timing                              |      |

|      | Parameters                                                            | 4–17 |

| 4–13 | Hyperpage Mode Memory Read Cycle Timing Parameters                    | 4–18 |

| 4–14 | Read-Modify-Write Memory Cycle Timing Parameters                      | 4–19 |

| 4–15 | CAS-Before-RAS Memory Refresh Cycle Timing                            |      |

|      | Parameters                                                            | 4–20 |

| 4–16 | ROM and GPP Data Cycle Timing Parameters                              | 4–21 |

| 4–17 | Pixel Clock and VAFC Clock Domain Signal ac                           |      |

|      | Parameters                                                            | 4–25 |

| 4–18 | VAFC Request Cycle Timing Parameters                                  | 4–26 |

| 4–19 | VAFC Video Data Transfer Cycle Timing Parameters                      | 4–27 |

| 6–1  | Airflow Versus Temperature                                            | 6–1  |

| 7–1  | Core Space per Frame Buffer Option                                    | 7–3  |

| 7–2  | Registers Supported by Write Alias Spaces 1, 4, 5, 6, and $\tilde{a}$ |      |

|      | 7                                                                     | 7–6  |

| 7–3  | Base Address Register 0 Register Map                              | 7–7   |

|------|-------------------------------------------------------------------|-------|

| 7–4  | Targets for Writes to Alternate Control Space                     | 7–9   |

| 7–5  | Base Address Register 1 Memory Space Map                          | 7–10  |

| 7–6  | Base Address Register 1 VGA Register Map                          | 7–11  |

| 7–7  | Base Address Register 1 Palette and DAC Register Map              | 7–13  |

| 7–8  | ROM Sparse Space PCI Read Data Field Description                  | 7–15  |

| 8–1  | 21130 Registers                                                   | 8–2   |

| 8–2  | Palette Snoop Response                                            | 8–14  |

| 8–3  | Memory Clock Frequency Select                                     | 8–24  |

| 8–4  | Graphics Modes                                                    | 8–45  |

| 8–5  | Boolean Raster Operations                                         | 8–64  |

| 8–6  | GSCR Mode Field Description                                       | 8–77  |

| 8–7  | Typical Scaled-Copy Mode Operations                               | 8–79  |

| 8–8  | Cursor Pixel Value Bit Description                                | 8–83  |

| 8–9  | Video Pixel Formats                                               | 8–92  |

| 8–10 | Variable Pixel Formats                                            | 8–95  |

| 8–11 | Pixel Occlusion Bitmap Field Description                          | 8–98  |

| 8–12 | VGA Register Port Map                                             | 8–115 |

| 8–13 | VGA External and General Register Port Map                        | 8–116 |

| 8–14 | Displayed Vertical Size as Function of HSP and VSP $\ldots$       | 8–118 |

| 8–15 | VGA CRTC and Extended Register Indices                            | 8–132 |

| 8–16 | Typical Pixel Clock Frequencies                                   | 8–170 |

| 8–17 | VGA Graphics Controller Write Modes                               | 8–180 |

| 9–1  | PCI Transactions to 2DA Memory Space                              | 9–6   |

| 9–2  | PCI Transactions to Configuration Space and Expansion             |       |

|      | ROM Space                                                         | 9–7   |

| 9–3  | PCI Transactions to VGA Memory and I/O Space                      | 9–8   |

| 9–4  | Snooped DAC Write PCI Transactions to VGA Space                   | 9–9   |

| 10–1 | Mode-Dependent Frame Buffer Write Operations                      | 10–2  |

| 10–2 | Graphics Command Register Write Operations                        | 10–3  |

| 10–3 | Source and Destination Operands According to Mode $\ldots \ldots$ | 10–5  |

| 10–4 | Simple Mode Parameters                                            | 10–7  |

| 10–5 | Opaque-Stipple Mode Parameters                                    | 10–9  |

| 10–6 | Transparent-Stipple Mode Parameters                               | 10–12 |

| 10–7 | Opaque-Fill Mode Parameters                                       | 10–14 |

| 10–8 | Transparent-Fill Mode Parameters                                  | 10–17 |

| 10–9 | Copy Mode Parameters                                              | 10–19 |

| 10–10 | Copy Mode Span Limits                               | 10–21 |

|-------|-----------------------------------------------------|-------|

| 10–11 | Assigning the Pixel Shift Value                     | 10–25 |

| 10–12 | DMA-Read Copy-Mode Parameters                       | 10–33 |

| 10–13 | Edge Mask Settings in DMA-Read Copy Mode            | 10–37 |

| 10–14 | Edge Mask for Short Spans in DMA-Read Copy Mode     | 10–37 |

| 10–15 | Scaled-Copy Mode Parameters                         | 10–39 |

| 10–16 | Scaled-Copy Mode PCI Write Data Field Description   | 10–40 |

| 10–17 | Opaque-Line Mode Parameters                         | 10–52 |

| 10–18 | Opaque-Line Mode Parameters Using Slope Registers   | 10–55 |

| 10–19 | Transparent-Line Mode Parameters                    | 10–62 |

| 11–1  | 21130 Base Address and Memory Space Enable Fields   | 11–1  |

| 11–2  | PCI Latency Timer and Bus Master Enable Fields      | 11–3  |

| 11–3  | Cursor Color Displayed with Monochrome Overlay      | 11–12 |

| 11–4  | Fully Shadowed, Pseudo-Shadowed, and Video-Disabled |       |

|       | Registers                                           | 11–22 |

| 11–5  | Video Address Configuration Registers               | 11–25 |

| 12–1  | Pin Usage in VGA Mode                               | 12–2  |

| 12–2  | Pin Usage in 32-bit GPP and ROM Modes               | 12–2  |

| 12–3  | Pin Usage in 64-bit GPP and ROM Modes               | 12–3  |

| 12–4  | Pin Usage in 32-bit GPP and VAFC Modes              | 12–4  |

| 12–5  | DPMS States                                         | 12–14 |

| A–1   | Signals by Function                                 | A-1   |

| B–1   | 21130 Register Alphabetical List                    | B–1   |

| B–2   | 21130 Register Summary                              | B–5   |

|       |                                                     |       |

# Preface

This manual describes the architecture, internal design, external interface, and specifications of the DECchip 21130 PCI Integrated Graphics and Video Accelerator.

#### Audience

This manual is for system designers, software developers, and hardware engineers who use the DECchip 21130.

# **Manual Organization**

This manual includes the following chapters and appendices and an index.

**Chapter 1 Introduction Chapter 2 Internal Architecture Chapter 3 Pinout Chapter 4 Electrical Specifications Chapter 5 Mechanical Specifications Chapter 6 Thermal Specifications Chapter 7 Address Space Chapter 8 Register Descriptions Chapter 9 PCI Operations Chapter 10 Graphics Operations** Chapter 11 Programming Chapter 12 Hardware Interface Appendix A Pin Summary **Appendix B Register Summary** Appendix C Technical Support, Ordering, and Associated Literature Index

### **Conventions**

The following conventions are used throughout this manual.

#### Abbreviations

• bpp

The terms "bits per pixel" and "bits/pixel" are abbreviated as bpp.

#### • Binary Multiples

When representing binary multiples, the abbreviations K, M, and G (kilo, mega, and giga) have the following values.

$\begin{array}{lll} K = & 2^{10} \ (1024) \\ M = & 2^{20} \ (1,048,576) \\ G = & 2^{30} \ (1,073,741,824) \end{array}$

For example:

| 2KB =       | 2 kilobytes =  | $2 \times 2^{10}$ bytes  |

|-------------|----------------|--------------------------|

| 4MB =       | 4 megabytes =  | $4 \times 2^{20}$ bytes  |

| 8GB =       | 8 gigabytes =  | $8 \times 2^{30}$ bytes  |

| 2K pixels = | 2 kilopixels = | $2 \times 2^{10}$ pixels |

| 4M pixels = | 4 megapixels = | $4 \times 2^{20}$ pixels |

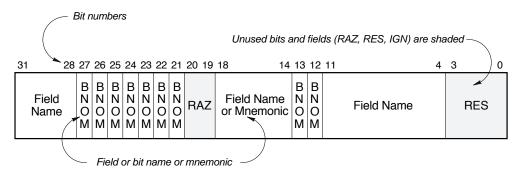

#### • Register Access

The abbreviations used to indicate the type of access to register fields and bits have the following definitions:

#### IGN — Ignore

Bits and fields specified as IGN are ignored when written.

#### MBZ — Must Be Zero

Software must never place a nonzero value in bits and fields specified as MBZ. Reads return unpredictable values. Such fields are reserved for future use.

#### RAZ — Read As Zero

Bits and fields specified as RAZ are ignored on writes and return a zero when read.

#### **RC** – **Read Clears**

Bits and fields specified as RC are cleared when read. Unless otherwise specified, such fields cannot be written.

#### **RES** — **Reserved**

Bits and fields specified as RES are reserved by Digital and should not be used; however, zeros can be written to reserved fields that cannot be masked.

#### **RO** – Read Only

Bits and fields specified as RO can be read and are ignored (not written) on writes.

#### RW — Read/Write

Bits and fields specified as RW can be read and written.

#### **R/W1C — Read/Write One to Clear**

Bits and fields specified as R/W1C can be read. Writing a one clears these bits for the duration of the write; writing a zero has no effect.

#### WO — Write Only

Bits and fields specified as WO can be written but not read.

#### Addresses

Unless otherwise noted, all addresses and offsets are hexadecimal.

#### Aligned and Unaligned

The terms *aligned* and *naturally aligned* are interchangeable and refer to data objects that are powers of two in size. An aligned datum of size  $2^n$  is stored in memory at a byte address that is a multiple of  $2^n$ ; that is, one that has *n* low-order zeros. For example, an aligned 64-byte stack frame has a memory address that is a multiple of 64.

A datum of size  $2^n$  is *unaligned* if it is stored in a byte address that is not a multiple of  $2^n$ .

#### **Bit Notation**

Multiple-bit fields can include contiguous and noncontiguous bits contained in angle brackets (<>). Multiple contiguous bits are indicated by a pair of numbers separated by a colon (:). For example, <9:7,5,2:0> specifies bits 9,8,7,5,2,1, and 0. Similarly, single bits are frequently indicated with angle brackets. For example, <27> specifies bit 27.

#### Caution

Cautions indicate potential damage to equipment or loss of data.

#### **Data Units**

The following data unit terminology is used throughout this manual.

| Term     | Words | Bytes | Bits | Other    |  |

|----------|-------|-------|------|----------|--|

| Byte     | 1⁄2   | 1     | 8    | _        |  |

| Word     | 1     | 2     | 16   | _        |  |

| Dword    | 2     | 4     | 32   | Longword |  |

| Quadword | 4     | 8     | 64   | 2 Dwords |  |

| Hexaword | 16    | 32    | 256  | 8 Dwords |  |

#### External

Unless otherwise stated, throughout this manual the term external means not contained in the DECchip 21130.

#### Note

Notes emphasize particularly important information.

#### Numbering

All numbers are decimal or hexadecimal unless otherwise indicated. In cases of ambiguity, a subscript indicates the radix of nondecimal numbers. For example, 19 is decimal, but  $19_{16}$  and 19A are hexadecimal. (Also see Addresses.)

#### **Ranges and Extents**

Ranges are specified by a pair of numbers separated by two periods (..) and are inclusive. For example, a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in angle brackets (<>) separated by a colon (:) and are inclusive. Bit fields and register sets are often specified as extents. For example, bits <7:3> specifies bits 7, 6, 5, 4, and 3, and GSLR<7:0> specifies a set of eight graphics slope registers.

#### **Register Figures**

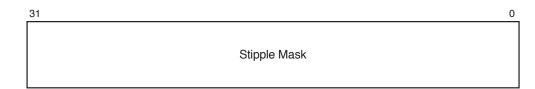

The following figure defines the conventions used in register format figures.

#### **Signal Names**

Signal names are printed in lowercase, boldface type. Low-asserted signals are indicated by the number sign (#) suffix. For example, **pll\_clk\_in** is a high-asserted signal, and **pll\_clk\_in**# is a low-asserted signal.

# 1 Introduction

The DECchip 21130 is a DRAM-based, 2D graphics accelerator for desktop systems running Microsoft Windows 3.1, Windows 95, and Windows NT. The 21130 integrates a peripheral component interconnect (PCI) interface, graphics accelerator, RAMDAC, phase-locked loop (PLL) timing generators, VGA controller, and video windowing hardware to merge graphics and video data.

The 21130 continues to refine Digital's proven graphics architecture. It incorporates most of the 2D graphics features introduced with the DECchip 21030 and adds many new features in a smaller package at lower cost.

# 1.1 Features

The following is a summary of the 21130 hardware features.

#### **PCI Interface**

The 21130 provides a glueless PCI interface with separate access to the VGA controller, 2D accelerator, and external BIOS ROM. It includes the PCI registers and supports PCI master and target transactions and direct memory access (DMA) read capability. The interface is fully electrically compliant with the *PCI Local Bus Specification, Revision 2.0.* The 21130 and connected external devices present only one PCI load.

Integrated Multimedia Real-Time Video Display Acceleration Includes:

- YUV-to-RGB index color space conversion

- Image scaling for arbitrary source and destination bitmap sizes

- Support for the Microsoft display control interface (DCI) for video acceleration (Video for Windows)

- Support for industry-standard codecs (Indeo, Cinepak, Video1, MPEG1, JPEG, Px64)

• VESA advanced feature connector (VAFC)

#### Faster and Simpler Line Drawing

In many systems, software is responsible for all of the cumbersome line setup calculations, including generating the Bresenham error and address increments for the major and minor axis steps as well as the initial error term.

In the 21130's streamlined interface, software needs to write only the absolute dx and absolute dy values of the line segment to one of eight slope registers, implicitly specifying the drawing octant. The 21130 then automatically generates all of the Bresenham terms, initializes the Bresenham registers, and draws up to 16 pixels. Lines can be extended beyond 16 pixels simply by using the continue register.

#### **Graphics and Multimedia Video Pipeline**

The pipeline includes the command FIFO and parser, pixel engine, DMA read FIFO, and graphics registers. It provides real-time scale, dither, and YUV-to-RGB index conversion for video display in a window or full-screen video display.

#### **DMA Engine for Image Data**

The 21130 has the DMA-read copy mode for fast host-to-screen bit-block transfers (BitBlts) and the scaled-copy mode for host-to-screen stretchBlt transfers. These modes allow large, contiguous regions to be directly transferred from main memory to the frame buffer. The onchip PCI interface allows main memory, other PCI graphics devices, or PCI video devices to be the external source.

#### **Proprietary Dithering**

The 21130 implements Digital's AccuLook dithering algorithm (patent-pending) to support rendering to 8-bpp and 16-bpp bitmaps. The quality of dithered 8-bpp pseudo-color images surpasses standard 16-bpp, direct-color image quality. The quality of the dithered 16-bpp, direct-color images is comparable to 24-bpp, true-color image quality.

#### 64-Byte Copy Buffer

The copy buffer supports high-bandwidth local frame buffer BitBlts.

#### Bresenham Line Drawing Engine and Setup Hardware

The onchip Bresenham line drawing engine and setup hardware performs Bresenham per-pixel line stepping and most of the Bresenham-term setup.

#### **Color Expansion**

The 21130 expands monochrome bitmaps to various pixel depths for drawing text or filling regions with solid or bitonal brushes.

#### 32-Bit or 64-Bit DRAM Display Memory Controller

The memory controller provides a 64-bit data path to the frame buffer. When the VAFC port is active, the memory controller is in 32-bit frame buffer mode, and the upper half of the data path is available for full-time video I/O. The memory controller supports hyperpage mode (extended data out—EDO) DRAMs, and linear frame-buffer addressing in 1, 2, or 4MB frame buffer configurations.

#### **VGA Controller**

The VGA controller supports VGA modes through  $13_{16}$ . It includes the video timing function and VGA registers.

#### Palette and DAC

The 21130's palette and DAC includes a 24-bit, true-color DAC; a 256-color RAM look-up table (LUT) for graphics; and a 256-color ROM LUT for video.

#### VAFC Port

The VAFC port passes bidirectional RGB or indexed 8- or 16-bit video on the upper 32 bits of the DRAM data path.

#### **Generic Peripheral Port**

The generic peripheral port (GPP) provides access to 8-bit devices such as video processing circuits, audio chips, or  $I^2C$  controllers. The 8-bit GPP is multiplexed on the DRAM data path.

#### 64 $\times$ 64 $\times$ 2 Onchip Cursor

The 21130 incorporates onchip cursor control. It retains a cursor image in its off-screen frame buffer memory and passes its control to the palette and DAC.

#### High-Performance CRT Controller

The 21130 CRTC supports the following VESA-standard, 75-Hz, noninterlaced resolutions (Figure 1–1):

$\begin{array}{ll} 1280 \times 1024 \mbox{ 8-bpp} \\ 1024 \times 768 & \mbox{ 8- and 16-bpp} \\ 800 \times 600 & \mbox{ 8-, 16-, and 24-bpp} \\ 640 \times 480 & \mbox{ 8-, 16-, and 24-bpp} \end{array}$

Note

For resolutions with 1024 or more vertical scanlines, the vertical front porch must be a minimum of two scanlines.

Figure 1–1 shows the supported VESA modes. The figure does not show lower-resolution, VGA-compatible display formats for VGA text and graphics (VGA modes 0 through  $13_{16}$ ).

|             |                                                    | 8–bpp       | 16–bpp       | 24–bpp*        | 32–bpp            |              |

|-------------|----------------------------------------------------|-------------|--------------|----------------|-------------------|--------------|

| 640 X       | 480                                                | 31.50       | 63.00        | 94.50          | 126.00            |              |

| 010 A 100   |                                                    | 101         | 111          | 112            | 112               |              |

|             |                                                    | 49.50       | 99.00        | 148.50         | 198.00            |              |

| 800 X       | 600                                                | 103         | 114          | 115            | 115               |              |

| 1004 V      | 700                                                | 78.75       | 157.50       | *Packed pixels | , not accelerated | d            |

| 1024 X 768  |                                                    | 104         | 117          |                |                   |              |

| 1000 V 1    | 004                                                | 135.00      |              |                |                   |              |

| 1280 X 1024 |                                                    | 107         |              |                |                   |              |

| Legend:     |                                                    |             |              |                |                   |              |

| 31.50       | 31.50 Peak memory bandwidth (MB/s) 1MB frame buffe |             |              |                |                   | frame buffer |

| 101         | VESA                                               | A Int10 mod | e (hexadecir | mal)           | 2MB               | frame buffer |

#### Figure 1–1 Supported VESA Display Modes

The peak memory bandwidth is the product of the pixel rate and pixel depth.

#### **Display Power-Management Signaling**

The 21130 also supports the VESA display power-management signaling (DPMS) for EPA Energy Star (Green PC) requirements. (See the *VESA Monitor Timing Proposed Standard for 640X480, 800X600, and 1280X1024 at 75 Hz, VDMT 75HZ Rev 1.2P* and the VESA *Display Power Management Signaling (DPMS) Proposal, Version 1.0p, Revision 0.7p* for more information.)

#### **Functions Not Supported**

The 21130 does not support the complete Windows set of 256 Boolean raster operations. The Windows manager and most applications typically use only three or four of the 256 Boolean raster operations (raster ops or ROPs). The most commonly used ROPs are included in the 16 functions supported by the 21130 hardware. For the infrequent cases when either the Windows NT display driver or Windows 95 display driver encounters an unsupported

ROP, it defaults to the graphics device interface (GDI). This does not affect performance for Windows or the majority of applications (including Windows benchmarks) and has only a negligible effect on the performance of the remaining minority of applications.

#### 1.2 Minimum System

The DECchip 21130 plays with a multiplicity of processors and operating systems and graphical user interfaces (GUIs). Its high level of integration facilitates the lowest cost graphics and multimedia subsystem implementation with the minimum real-estate requirements on the motherboard or as a plug-and-play option.

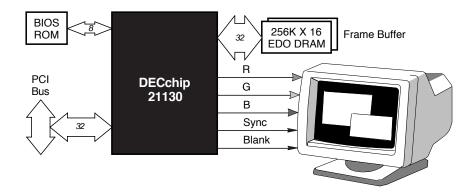

The 21130 allows simple, glueless, multimedia subsystem implementations. Figure 1-2 shows the simplest configuration, requiring only four chips.

Figure 1–2 DECchip 21130 in Minimum System Configuration

## **1.3 Basic Programming Model**

In the basic 21130 programming model, the processor writes directly to addresses within the 21130's frame buffer address space. The data is interpreted according to the current graphics mode to perform the desired operation. Exceptions to this paradigm are described next.

There are four primary 21130 operating modes: simple, stipple, line, and copy. Each primary mode of operation has an associated byte mask, Boolean raster operation, and bitmap depth. The byte mask determines which bits in a pixel can be modified during a write. The raster operation provides one of sixteen 2-operand Boolean functions of source (or pattern) and destination, and

#### **1.3 Basic Programming Model**

automatically performs a read-modify-write cycle when necessary. The bitmap depth specifies how pixel data maps to frame buffer Dwords.

#### Simple Mode

In simple mode, writes to the frame buffer are similar to writes to main memory, except for the optional effects of the byte mask, pixel mask, raster operation, and bitmap depth. In this mode, the byte mask and the pixel mask determine which pixels are written.

#### **Stipple Mode**

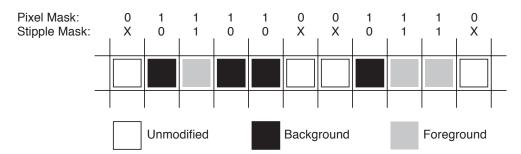

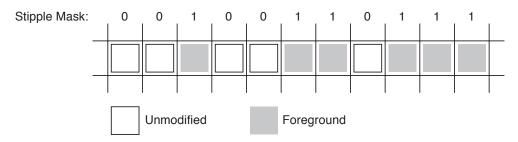

In stipple mode (color expansion mode), data written to the frame buffer is interpreted as a monochrome pattern, in which the following occurs:

- Ones are expanded into foreground pixels.

- Zeros are either expanded into background pixels (opaque stipple mode) or not expanded (transparent stipple mode).

In the opaque and transparent stipple modes, the pixel mask can be programmed to write fewer than 32 pixels.

#### Line Mode

In line mode, the processor sets up registers for the Bresenham engine and then writes into the frame buffer at the starting address of the line. The data written by the processor is interpreted as a monochrome pattern, in which the following occurs:

- Ones are expanded into foreground pixels.

- Zeros are either expanded into background pixels (opaque line mode) or have no effect (transparent line mode).

#### **Copy Mode**

In copy mode, the processor writes alternately to the source and destination address within the frame buffer. The data written by the processor is interpreted as a bit mask that specifies which pixels are to be read (source) or written (destination).

#### 1.3.1 Extensions to the Basic Programming Model

Several extensions to the basic programming model are available.

#### Stipple-Fill Mode

In stipple-fill mode, each write causes the 21130 to fill as many as 2K pixels on a scanline, using the 32-bit data as a 32-bit monochrome pattern.

#### **1.3 Basic Programming Model**

#### Line Mode

In line mode, the eight slope registers (one per octant) allow the processor to offload some of the traditional line setup computations. The processor writes the absolute values of the line rise and run to one of the slope registers, implicitly specifying a drawing octant, and causes the 21130 to generate the Bresenham address and error terms and draw up to 16 pixels at one time. Consequently, the processor can specify a short, connected line with one 32-bit write. Lines can be extended beyond 16 pixels simply by writing the continue register.

#### Copy Mode

In copy mode, the copy-64 source and copy-64 destination registers allow the processor to read 64 unmasked bytes from the source and write 64 unmasked bytes to the destination with one write to each register. This makes full use of the 64-byte copy buffer for large area copies of 8-bit pixels.

In the DMA copy modes, the processor can specify the addresses of the source in PCI memory space. One write to the frame buffer then causes the 21130 to begin reading from the PCI and writing to the frame buffer.

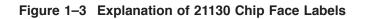

## 1.4 Chip Revisions

There are 21130 chips with different revision levels. As a result, you need to check for the chip revision number printed on the face of the chip. Table 1–1 describes the revision levels and Figure 1–3 shows where to locate the printed revision level on the chip. This information is also available in the PCI class and revision register (PCRR, see Section 8.2.3).

This manual describes revision C (DC7538C).

| Revision Level | Chip Revision Number |

|----------------|----------------------|

| A              | DC7538A              |

| В              | DC7538B              |

| С              | DC7538C              |

Table 1–1 21130 Chip Revision Levels

# **2** Internal Architecture

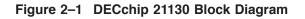

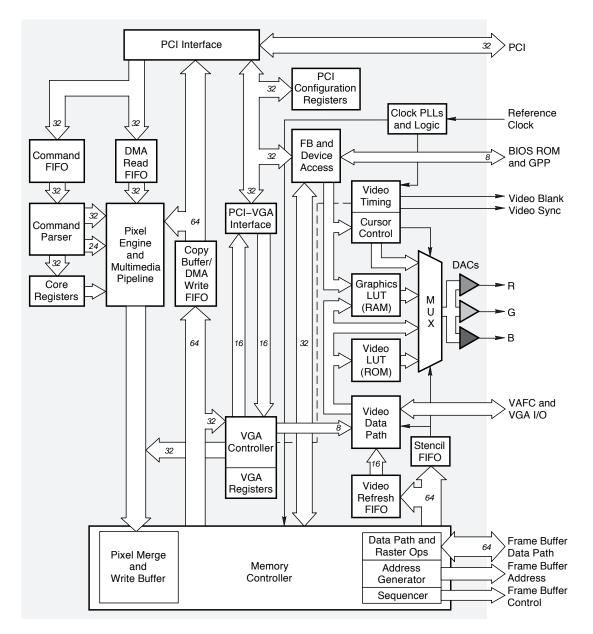

This chapter describes the DECchip 21130 microarchitecture. Figure 2–1 is a block diagram of the chip showing its major functional areas.

# 2.1 PCI Interface

The PCI interface connects the 21130 core to the PCI bus. The primary function of the PCI interface is to keep the command FIFO filled with writes and commands issued over the PCI to the 21130 registers and frame buffer.

The PCI interface supports most of the PCI bus commands as a target. It also allows the 21130 to be a PCI master for direct memory access (DMA) operations, transferring pixel data between memory that can be accessed from the PCI and the 21130 frame buffer. DMA read data is taken from the PCI and passed to the DMA read FIFO. As a target or master, the PCI interface initiates and responds to different types of termination sequences. The PCI interface controls all access to the PCI configuration registers.

#### 2.1.1 PCI Registers

The PCI registers reside in the 21130 PCI configuration space and include the device-independent registers required for all PCI devices as well as the PCI device-specific registers in the 21130.

# 2.2 Command FIFO

The command FIFO contains 64 Dword entries. It buffers writes to the frame buffer and core registers for processing by the 21130 core. The PCI interface loads the command FIFO with an address followed by an arbitrary number of data entries. The command parser unloads the entries and initiates processing.

#### 2.2 Command FIFO

#### 2.2 Command FIFO

The command FIFO contains only core-space write data, such as writes to the 21130 core registers, alternate control space, and frame buffer space. Because the PCI interface accepts burst memory writes to base address 0 as a PCI target, the command FIFO can independently store an address or data in each of its 64 entries. In other words, the command FIFO can hold any combination of addresses and data, from one address and 63 entries of burst data to 32 pairs of address and data entries. If the command parser detects a sequence of one address and multiple data entries, it generates and matches the correct address to each data entry when it unloads the command FIFO.

The command FIFO is a boundary between chip clocking domains (see Figure 4–1). The input runs at the PCI clock rate and the output runs at the 21130 core clock rate.

## 2.3 Command Parser

The command parser processes graphics commands and register write accesses. It unloads graphics commands (in the form of address and data) from the command FIFO and performs initial processing before passing commands to the pixel engine. If the command parser detects a sequence of one address and multiple data entries, it generates an address for each data entry.

The command parser runs at the 21130 core clock rate.

#### 2.3.1 Pixel-Processing Pipeline Coherence

The pixel-processing pipeline consists of the pixel engine, pixel-merge function, write buffer, and memory controller. The command parser imposes hardware register interlocks to ensure coherent processing through the pipeline. The interlocks allow the pipeline to operate concurrently with register updates; that is, updates to graphics operation parameters.

Most of the parameter registers are double-buffered. The command parser schedules buffered-register loading and swapping, and, in certain cases, delays command processing to maintain parameter coherence through the pipeline. In the case of writes to the command status register, raster operation register, mode register, and scaled-copy control register, the interlock mechanism waits until the pipeline has been flushed before it resumes processing.

Note \_\_\_\_\_

The deep register is not managed by hardware interlock and requires software scheduling.

#### 2.3 Command Parser

#### 2.3.2 Frame Buffer Writes

The command parser detects all writes to the frame buffer and begins processing the graphics command specified by the current graphics mode. The command parser does not perform any pixel address or data calculations, but forwards *predigested* commands to the pixel engine for processing.

#### 2.3.2.1 Fill Mode

For all fill mode drawing, the command parser breaks large-span fill commands into 32-pixel span commands which the pixel engine can accept and process. The pixel engine can process individual pixels, 16-pixel lines, and 32-pixel spans.

#### 2.3.2.2 Bresenham Setup Hardware

The command parser incorporates the Bresenham setup hardware (the Bresenham engine is in the pixel engine). When the command parser receives a write to the slope registers, span width register, or slope-no-go registers, it calculates the Bresenham terms: length, initial error, error increments 1 and 2, and address increments 1 and 2. When the write is to a slope register or the span width register, the command parser also forwards the line command to the pixel engine. The command parser forwards all other line, span, and pixel mode drawing commands directly to the pixel engine.

#### 2.4 Pixel Engine

The pixel engine does all of the pixel address and value calculations. It receives single-pixel, 16-pixel line, and 32-pixel span commands from the command parser and reduces them into individual 16-bit-aligned or 64-bit-aligned frame buffer address and data pairs destined for the memory controller. The pixel engine contains the following pixel processing hardware to generate pixel addresses and data.

• Stipple logic

The stipple logic expands a monochrome bitmap (and optional bitmap mask) into foreground or background color (or neither), on a per-pixel basis over a 16-pixel line or 32-pixel span.

#### 2.4 Pixel Engine

• Bresenham engine

The Bresenham engine steps through the pixels of a line (up to 16 pixels at a time), generating a pixel address for each step.

• Dither logic

The dither logic implements Digital's AccuLook dithering algorithm. The algorithm maps 8 bits per channel (24-bpp) YUV or RGB color to various combinations of 8-, 16-, or 32-bpp YUV or RGB. The source of the 24-bpp RGB is the scaled-copy, 24-bit pixel stream.

After the pixel engine reduces spans into pixels and calculates the modedependent pixel data, it translates pixel addresses into frame buffer addresses as a function of the frame buffer depth and target bitmap. The pixel engine forwards each memory access to the pixel-merge function.

The pixel engine receives data directly from the memory controller for copy operations. In copy mode, the pixel engine first forwards a series of read requests, tagged with the source address, to the pixel-merge function. Eventually, the memory controller returns source pixel data (64 bits at a time) to the copy buffer. Then, when instructed by the command parser, the pixel engine unloads the copy buffer and forwards that data back to the pixel-merge function as a write tagged with the destination address.

The pixel engine runs at the core clock rate.

# 2.5 Memory Controller

The memory controller provides the interface to the frame buffer and responds to requests from two sources: the pixel engine and the frame buffer and device access function. It responds to requests from the pixel engine (through the pixel-merge function and write buffer) for accelerated drawing operations in the frame buffer.

#### 2.5.1 Pixel Merge

To improve drawing performance, the pixel merge function merges pixel writes to eliminate consecutive writes to different bytes at the same quadword address. (Such write sequences occur frequently during line drawing and multimedia operations.) The pixel merge function:

- Receives requests for frame buffer writes from the pixel engine

- Temporarily stores the requests

- Determines if the writes are to different bytes in the same quadword

- Merges consecutive writes to the same quadword

#### 2.5 Memory Controller

Consecutive writes are not merged if they do not use the same raster operation or if consecutive operations are writing to the same byte. The pixel merge buffer is flushed when the write buffer is empty.

The pixel merge function runs at the core clock rate.

#### 2.5.2 Write Buffer

The DRAM sequencer often processes write commands faster than the graphics engine generates them, and the write buffer helps to optimize DRAM use between drawing operations and screen refresh. The write buffer is a 16-entry FIFO that buffers merged writes from the pixel engine. The memory controller unloads the buffer when the DRAM is available for drawing.

The write buffer is written at the core clock rate and read at the memory clock rate (twice the core clock rate).

As long as the write buffer contains valid entries, the memory controller continues to unload addresses and data. The memory controller performs a Boolean ROP function on each write, as specified by the raster operation register. If the ROP is a function of the destination, the memory controller automatically performs the necessary read-modify-write operation.

The memory controller returns requested read data to the pixel engine through the copy buffer.

#### 2.5.3 Frame Buffer and Device Access Requests

The memory controller responds to occasional asynchronous requests from the frame buffer and device access function for the following:

- Direct host reads of the frame buffer

- External EEPROM reads and writes

- GPP reads and writes

Note \_\_\_\_\_

The 21130 supports one external (E)(E)PROM. It and its associated functions are referred to as the BIOS ROM, EEPROM, flash ROM, PCI expansion ROM (space), and ROM ((sparse) space).

To conserve 21130 pins, the GPP address, data, and control lines are tied to a subset of the memory controller address and data lines. Therefore, to read or write the external EEPROM or a generic peripheral, the memory controller

## 2.5 Memory Controller

must interrupt processing of write buffer address and data. (See Section 2.12.2 for more information about mode restrictions due to shared pins.)

When the memory controller receives a request from the frame buffer and device access function, it suspends write-buffer entry processing within a maximum latency and services the request. The frame buffer and device access function specifies the type of access and passes address and data as required. The memory controller performs the following cycles:

- GPP or EEPROM access—the memory controller drives an address and either drives (write) or latches (read) a byte of data.

- Cursor data fetch—the memory controller performs a frame buffer read at the specified address and returns two successive quadwords to the frame buffer and device access function.

After an asynchronous access has been serviced, the memory controller resumes processing addresses and data from the write buffer.

The memory controller also issues CAS-before-RAS refresh cycles frequently enough to keep the dynamic memory refreshed.

The memory controller runs at twice the core clock rate, and can perform CAS page-mode cycles at the core clock rate.

# 2.6 Core Registers

The core registers are all the registers physically implemented in the base address 0 register space core (Section 7.5.1). Many of the core registers are double-buffered to allow pipelined graphics processing to overlap register updates. The command parser controls the core register read access, write access, and double-buffering.

# 2.7 DMA Read FIFO

The DMA read FIFO contains 32 Dword entries. It is loaded by the PCI interface during a DMA-read copy operation and unloaded by the pixel engine. The DMA read FIFO contains only pixel data.

The DMA read FIFO is a boundary between chip clocking domains (see Figure 4–1). The input runs at the PCI clock rate and the output runs at the 21130 core clock rate.

## 2.8 Copy Buffer

# 2.8 Copy Buffer

The copy buffer contains 8 quadword (64-bit) entries. It is used when transferring data from a frame buffer source to a destination in the frame buffer.

The memory controller returns source data to the copy buffer. In copy mode, the pixel engine forwards the data, tagged with a destination address, down the pixel processing pipeline to the memory controller.

# 2.9 Frame Buffer and Device Access

The frame buffer and device access (FBDA) function collects requests for access to the frame buffer and external devices (GPP and EEPROM) from several sources. It prioritizes and forwards the requests to the memory controller. The memory controller processes the requests as interrupts to write-buffer processing. The following requests are routed to the FBDA function:

- Direct frame buffer read—from the host through the PCI interface.

- External EEPROM read and write—PCI expansion ROM space read requests detected and routed by the PCI interface.

The FBDA function provides the signals required to write one 8-bit EEPROM and a generic peripheral.

# 2.10 Generic Peripheral Port

The generic peripheral port (GPP) consists of an 8-bit data bus and several control signals. It can connect, with little or no glue logic, to many types of devices including audio chips, DSPs, and a variety of video processing components.